第4章-并行接口P0~P3和单片机的中断系统

单片机原理及接口技术第四版答案

单片机原理及接口技术第四版答案【篇一:《单片机原理及接口技术(第2版)张毅刚》第4章习题及答案】第4章 at89s51单片机的中断系统思考题及习题41.外部中断1的中断入口地址为 ,定时器1的中断入口地址为。

答:0013h;001bh2.若(ip)=00010100b,则优先级最高者为,最低者为。

答:外部中断1,定时器t13.中断服务子程序与普通子程序有哪些相同和不同之处?答:reti指令在返回的同时自动清除相应的不可寻址的优先级触发器,以允许下次中断,而ret指令则没有这个操作。

除了这一点两条指令不同外,其它操作都相同。

4.下列说法正确的是。

答:da. 各中断源发出的中断请求信号,都会标记在at89s51的ie寄存器中b. 各中断源发出的中断请求信号,都会标记在at89s51的tmod寄存器中c. 各中断源发出的中断请求信号,都会标记在at89s51的ip寄存器中d. 各中断源发出的中断请求信号,都会标记在at89s51的tcon与scon寄存器中5.at89s51单片机响应外部中断的典型时间是多少?在哪些情况下,cpu将推迟对外部中断请求的响应?答:在一个单一中断的系统里,at89s51单片机对外部中断请求的响应时间总是在3~8个机器周期之间。

在下述三种情况下,at89s51将推迟对外部中断请求的响应:(1)at89s52正在处理同级或更高优先级的中断。

(2)所查询的机器周期不是当前正在执行指令的最后一个机器周期。

(3)正在执行的指令是reti或是访问ie或ip的指令。

如果存在上述三种情况之一,at89s52将丢弃中断查询结果,将推迟对外部中断请求的响应。

6.中断查询确认后,在下列各种at89s51单片机运行情况下,能立即进行响应的是。

a. 当前正在进行高优先级中断处理b. 当前正在执行reti指令c. 当前指令是div指令,且正处于取指令的机器周期d. 当前指令是mov a,r3答:d7. at89s51单片机响应中断后,产生长调用指令lcall,执行该指令的过程包括:首先把的内容压入堆栈,以进行断点保护,然后把长调用指令的16位地址送,使程序执行转向中的中断地址区。

第5章 并行接口P0~P3

大多数口线都有双重功能,具体介绍如下:

PO口—1.作为输入/输出口。

2.作为地址/数据总线 ,接外围芯片时PO口分时输出低 8 位地址与数据信号。

P1口—作为输入/输出口。

P1.0 T2引脚,定时/计数器2外部计数脉冲输入 P1.1 T2EX引脚,定时/计数器2触发和方向控制 P1.5 MOSI引脚,在系统编程数据输入 P1.6 MISO引脚,在系统编程数据输出 P1.7 SCK引脚,在系统编程时钟输入

这是为了避免错读引脚的电平信号,例如用一根口线去 驱动一个晶体管基极,当向口线写“1”,晶体管导通,导通 的PN结会把引脚的电平拉低,如读引脚数据,则会读为0 , 而实际上原口线的数据为1。因而采用读锁存器Q的值而避免 了错读。究竟是读引脚还是读 锁存器,CPU内部会自行判断 是发读引脚脉冲还是读锁存器脉冲,读者不必在意。

归纳四个并行口使用的注意事项如下:

1.如果单片机内部有程序存贮器,不需要扩展外部存贮器和 I/O接口,单片机的四个口均可作I/O口使用。

2.四个口在作输入口使用时,均应先对其写“1”,以避免误 读。

3.P0口作I/O口使用时应外接10K的上拉电阻,其它口则可不必。 4.P2可某几根线作地址使用时,剩下的线不能作I/O口线使用。 5.P3口的某些口线作第二功能时,剩下的口线可以单独作I/O

内容提要

★单片机的并行接口P0~P3

★ PO~P3端口的功能和内部结构 ★ PO~P3端口的编程 ★ 用并行口设计LED数码显示和键盘电路 ★ 并行接口小结

★MCS-51单片机的中断系统

★ 中断的基本概念 ★ 中断的系统结构 ★ 中断的响应过程 ★ 中断的的应用编程

★小结

I/0接口

微机原理试题及答案

第一章1-1选择1.计算机中最常用的字符信息编码是(A )A ASCIIB BCD码C 余3码D 循环码2.要MCS-51系统中,若晶振频率屡8MHz,一个机器周期等于(A ) gsA 1.5B 3C 1D 0.53.MCS-51的时钟最高频率是(A ).A 12MHzB 6 MHzC 8 MHzD 10 MHz4.以下不是构成的控制器部件(D ):A程序计数器、B指令寄存器、C指令译码器、D存储器5.以下不是构成单片机的部件(D )A 微处理器(CPU)、B存储器C接口适配器(I\O接口电路)D打印机6.下列不是单片机总线是(D )A地址总线B控制总线C数据总线D输出总线7.-49D的二进制补码为.(B )A 11101111B 11101101C 0001000D 111011008.十进制29的二进制表示为原码(C )A 11100010B 10101111C 00011101D 000011119.十进制0.625转换成二进制数是(A )A 0.101B 0.111C 0.110D 0.10010选出不是计算机中常作的码制是(D )A 原码B反码C补码 D ASCII1-2填空1.计算机中常作的码制有原码、反码和补码2.十进制29的二进制表示为000111013.十进制数-29的8位补码表示为.111000114.单片微型机CPU、存储器和I\O接口三部分组成.5.若不使用MCS-51片内存器引脚EA必须接地.6.输入输出设备是计算机与外部世界交换信息的载体.7.十进制数-47用8位二讲制补码表示为.110100018.-49D的二讲制补码为.111011019.计算机中最常用的字符信息编码是ASCII10.计算机中的数称为机器数,它的实际值叫一真值。

1-3判断1.我们所说的计算机实质上是计算机的硬件系统与软件系统的总称。

(寸)2.MCS-51 上电复位时,SBUF=00H。

(x )。

SBUF不定。

并行接口和中断

JB P1.1,LIG ;开关开,转LIG SETB P1.0 SJMP AGA LIG: CLR P1.0 ;开关开,二极管灭 ;开关合上,二极管亮

SJMP AGA

第4章

并行接口P0-P3和单片机的中断系统

读锁存器 1 内部总线 写锁存器 P1.x 锁存器 CL Q 2 读引脚 D Q

第4章

并行接口P0-P3和单片机的中断系统

总结:

在没有外扩任何芯片时,MCS-51单片机内部并行口

可以作为输出口,直接与输出外设连接,常用的输出外设

是发光二极管(也可以接扬声器); MCS-51单片机内部 并行口也可以作为输入口,直接与输入外设连接,常用的

输入外设是开关。

第4章

并行接口P0-P3和单片机的中断系统

4.3 七段LED显示器接口

在单片机控制系统中显示器是必不可少的外设。常用

的显示器有发光二极管,数码管和液晶显示器。本节介绍

数码管接口。 4.3.1 数码管简介 4.3.2 单个七段LED数码管的接口

4.3.3 多个七段LED数码管的接口

第4章

并行接口P0-P3和单片机的中断系统 a b c d e a b c COM d e f g Dp 共阳极 共阴极 COM

4.3.1 数码管简介

CP Q

注意: 1、P1口作输入口时,P10—P17上的信号经过缓冲器送到内部数据总线上。 在读引脚之前,要先将锁存器置1,否则可能读错。

2、CPU对P1口的读操作有2种:读引脚和读—改—写锁存器。

返回

第4章

并行接口P0-P3和单片机的中断系统

4.1.3 P2口结构

地址控制线

+5V

读锁存

P2.0 D Q

第4章 80C51单片机IO端口及应用最终

24

参考程序:

#include <reg51.h> void main(void) { unsigned char i; P2=0xff; for(;;) { i=P2; P1=i; } }

25

4.6单片机I/O口控制电磁继电器

在控制系统中,常常存在电子电路与电气电路的互 相连接问题,需要电子电路控制电气电路的执行元件, 例如电动机、电磁铁、电灯等,同时实现电子线路与电 气电路的电隔离,以保护电子电路和人身的安全,继电 器在其中起了重要的桥梁作用。

控制

T1

内部总线 写锁存器 读引脚

D P0.x Q 锁存器 Q

BUF2

MUX

P0.x引脚 T2

图4-1 P0口的位电路结构

4

2.P0口工作原理 (1)P0口作为地址/数据总线分时复用口

当80C51单片机外部扩展存储器或者I/O接口芯片,需要 P0口作为地址/数据总线分时使用时,“控制”信号输出高 电平;转换开关MUX 将T2与反相器输出端接通,同时“与 门”开锁,“地址或数据”信号通过与门驱动T1管,并通过 反相器驱动T2管,使得P0.x引脚的输出状态随“地址/数据” 状态的变化而变化。具体输出过程如下。

注意,当P0口作输出口使用时,输出级属开漏电路,在 P0.x引脚应外接上拉电阻。

6

② P0口作为I/O口输入时,端口中的两个三态缓冲器用于读 操作。有2种读操作:读锁存器和读引脚。

“读引脚”:当执行一般的端口输入指令时,引脚上的外部 信号既加在三态缓冲器BUF2的输入端,又加在场效应管T2 漏极上,若此时T2导通,则引脚上的电位被钳在0电平上。 为使读引脚能正确地读入,在输入数据时,要先向锁存器置 “1”,使其Q反端为0,使输出级T1和T2两个管子均被截止, 引脚处于悬浮状态;作高阻抗输入。“读引脚”脉冲把三态 缓冲器打开,于是引脚上的数据经缓冲器到内部总线;

单片机原理及接口技术课后答案李朝青第三版

第一题 8051单片机包含哪些主要逻辑功能部件?1.CPU2.ROM3.RAM4.Timer/Counter5.UART(串口)(通用异步串行接收机发送机)6.4个8bits Port(并口)7.Int0,int1(外部中断)第二题8051的/EA端有什么用处?1.EA端Enable Address(外部程序存储器地址允许输入端)2.低电平有效3.EA=0(低电平有效)时,只允许访问外部存储器4.EA=1时,可以访问部和外部存储器5.EA还有复用功能,Vpp(Pulse of Programming)(编程脉冲)(固化编程电压输入端)第三题8051的存储器分为那几个空间?怎样区别不同空间的寻址?1.ROM(片ROM和片外ROM统一编址)(使用MOVC)(数据传送指令)(16bits地址)(64KB)2.片外RAM(MOVX)(16bits地址)(64KB)3.片RAM(MOV)(8bits地址)(256B)•什么是普林斯顿结构?哈佛结构?1.普林斯顿结构,ROM和RAM统一编址2.哈佛结构,ROM和RAM分开编址第四章8051片RAM的空间是怎样分配的?1.片RAM有256B2.低128B是真正的RAM区3.高128B是SFR(特殊功能寄存器)区•真正的RAM区可以分成那几个部分?1.4个工作寄存器区(R0~R7)2.位寻址区3.真正的RAM区第五题简述布尔处理存储器的空间分配,片RAM中包含哪些可位寻址单元?1.片RAM区从00H~FFH(256B)2.其中20H~2FH(字节地址)是位寻址区3.对应的位地址是00H~7FH第六题如何简洁地判断8051正在工作?1.用示波器观察8051的XTAL2端是否有脉冲信号输出(判断震荡电路工作是否正常?)2.ALE(地址锁存允许)(Address Latch Enable)输出是fosc的6分频3.用示波器观察ALE是否有脉冲输出(判断 8051芯片的好坏?)4.观察PSEN(判断8051能够到EPROM 或ROM中读取指令码?)5.因为/PSEN接外部EPROM(ROM)的/OE端子6.OE=Output Enable(输出允许)第七题 8051如何确定和改变当前工作寄存器组?1.PSW(程序状态字)(Program Status Word)中的RS1和RS02.可以给出4中组合3.用来从4组工作寄存器组中进行选择4.PSW属于SFR(Special Function Register)(特殊功能寄存器)第十题 8051的/EA信号有什么功能?在使用8031的时候,EA信号引脚应该如何处理?1.EA=Enable Address(外部程序存储器地址允许输入端)2.EA=0(低电平有效)只允许访问外部存储器3.EA=1外ROM都可以访问4.因为8031没有片ROM5.只能访问片外的EPROM6.应该使EA=0(有效)第十二题部RAM第128B单元划分成那几个主要部分?各部分主要功能是什么?1.当前工作寄存器组(4组)(00H~1FH)2.位寻址区(20H~2FH)3.真正的RAM区(30H~7FH)第十三题使单片机复位有哪几种方法?复位后机器的初始状态如何?1.上电复位2.上电复位+手动复位3.脉冲复位4.复位会重置一些寄存器第十四题开机复位后,CPU使用的是哪组工作寄存器?它们的地址什么什么?1.8051有4个工作寄存器组2.分别从R0~R73.分别位于 00H~07H,08H~0FH,10H~17H,18H~1FH4.开机复位后,默认使用寄存器组0第十五题 PSW的作用是什么?作用是什么?1.PSW是一个SFR(特殊功能寄存器)2.位于片RAM的高128B3.具体地址D0H(00H~FFH)(片RAM的编址)(8bits编址方法)4.PSW=Program Status Word(程序状态字)•PSW的常用标志位有哪些?1.CY=Carry(进位标志位)2.AC=Auxiliary Carry(辅助进位标志位)(半进位标志位)3.F0用户标志位4.RS1,RS0,用来选择当前工作寄存器组(R0~R7)(4选1)5.OV=Overflow(溢出标志位)6.P=Parity(奇偶校验位)第十五题位地址7CH和字节地址7CH如何区别?位地址7CH在片RAM中什么地方?1.片RAM的地址从00H~FFH2.其中20H~2FH(字节地址)是位寻址区(bits)3.位地址从00H~7FH4.位地址7CH位于字节地址2FH5.可以从寻址方式来区分6.位地址使用位寻址方式7.字节地址使用直接寻址,间接寻址第十七题 8051的时钟周期,震荡周期有什么关系?1.震荡周期2.时钟周期=状态周期(state)3.时钟周期=2*振荡周期4.机器周期=6*时钟周期=12*震荡周期5.指令周期=1~4个机器周期第十八题一个机器周期的时序如何划分?1.一个机器周期=12个震荡周期=6个时钟周期(状态周期)2.S1P1,S1P2,S2P1,S2P2,S3P1,S3P2,S4P1,S4P2,S5P1,S5P2,S6P1,S6P23.其中s=state(状态),p=phase(相位)第十九题什么叫做堆栈?SP是什么?它的作用是什么?8051堆栈的容量不能超过多少个字节?1.Stack(堆栈)2.具有FILO,LIFO的特性3.SP=Stack Pointer(堆栈指针)4.SP是栈顶指示器评论这1.微处理器,RAM,ROM,以及I/O口,定时器,构成的微型计算机称为单片机。

单片机题库分章节答案(C语言)

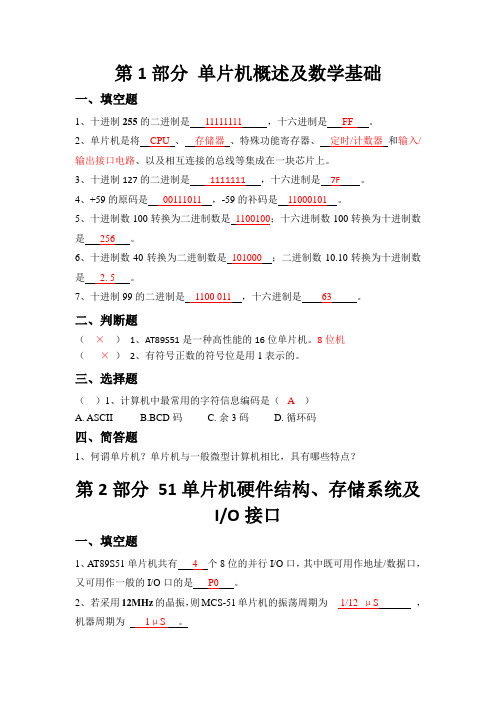

第1部分单片机概述及数学基础一、填空题1、十进制255的二进制是11111111,十六进制是FF 。

2、单片机是将CPU、存储器、特殊功能寄存器、定时/计数器和输入/输出接口电路、以及相互连接的总线等集成在一块芯片上。

3、十进制127的二进制是1111111,十六进制是7F。

4、+59的原码是00111011,-59的补码是11000101。

5、十进制数100转换为二进制数是1100100;十六进制数100转换为十进制数是256。

6、十进制数40转换为二进制数是101000;二进制数10.10转换为十进制数是 2. 5。

7、十进制99的二进制是1100 011,十六进制是63。

二、判断题(×)1、AT89S51是一种高性能的16位单片机。

8位机(×)2、有符号正数的符号位是用1表示的。

三、选择题()1、计算机中最常用的字符信息编码是(A)A. ASCIIB.BCD码C. 余3码D. 循环码四、简答题1、何谓单片机?单片机与一般微型计算机相比,具有哪些特点?第2部分51单片机硬件结构、存储系统及I/O接口一、填空题1、AT89S51单片机共有 4 个8位的并行I/O口,其中既可用作地址/数据口,又可用作一般的I/O口的是P0。

2、若采用12MHz的晶振,则MCS-51单片机的振荡周期为__ 1/12 μS __ ,机器周期为____1μS __。

3、AT89S51单片机字长是___8___位,有___40根引脚。

4.89S51单片机是8位单片机,其PC计数器是16位。

5.若单片机使用的晶振频率是6MHz,那么一个振荡周期是1/6µS,一个机器周期是2μSµS。

6.89S51单片机是+5 V供电的。

4.0-5.5V7.堆栈是内部数据RAM区中,数据按先进后出的原则出入栈的。

8.MSC-51系列单片机具有 4 个并行输入/输出端口,其中_P0_口是一个两用接口,它可分时输出外部存储器的低八位地址和传送数据,而_P1__口是一个专供用户使用的I/O口,常用于第二功能的是P3 口。

2020智慧树,知到《单片机原理及应用》章节测试【完整答案】

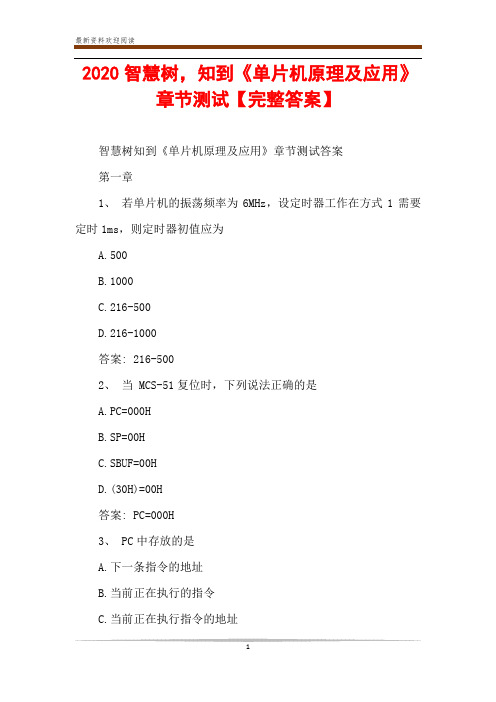

2020智慧树,知到《单片机原理及应用》章节测试【完整答案】智慧树知到《单片机原理及应用》章节测试答案第一章1、若单片机的振荡频率为6MHz,设定时器工作在方式1需要定时1ms,则定时器初值应为A.500B.1000C.216-500D.216-1000答案: 216-5002、当 MCS-51复位时,下列说法正确的是A.PC=000HB.SP=00HC.SBUF=00HD.(30H)=00H答案: PC=000H3、 PC中存放的是A.下一条指令的地址B.当前正在执行的指令C.当前正在执行指令的地址D.下一条要执行的指令答案: 下一条要执行的指令4、所谓CPU是指A.运算器与控制器B.运算器与存储器C.输入输出设备D.控制器与存储器答案: 运算器与控制器5、当ALE信号有效时,表示A.从ROM读取数据B.从P0口可靠地送出地址低8位C.从P0口送出数据D.从RAM中读取数据答案: 从P0口可靠地送出地址低8位6、世界上第一台电子见算计诞生于( )年。

A.1946B.1956C.1940D.1950答案: 19467、以微处理器为核心组成的微型计算机属于( )计算机。

A.第一代B.第二代C.第三代D.第四代答案: 第四代8、个人计算机属于( )。

A.小巨型机B.小型计算机C.微型计算机D.中型计算机答案: 微型计算机9、通常所说的PC是指( )。

A.大型计算机B.小型计算机C.中型计算机D.微型计算机答案: 微型计算机10、 8051单片机的字长是位A.8B.4C.16D.32答案: 811、存储器分成内存和外存两大部分,其中外内存可以直接与CPU交换信息。

A.对B.错答案: 错12、当MCS-51上电复位时,堆栈指针SP=07H。

( )A.对B.错答案: 对13、MCS-51的特殊功能寄存器分布在00H~7FH地址范围内。

( )A.对B.错答案: 错14、程序存储器和数据存储器的作用不同,程序存储器一般用存放数据表格和程序,而数据存储器一般用来存放数据( )A.对B.错答案: 错15、 MCS-51上电复位时,SBUF=00H。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

/RD /WR

20

例1.设计一电路,监视某开关K,用发光二极管LED显示开 关状态。如果开关合上,LED 亮;开关断开,LED熄灭。 分析:设计电路如图4. 2如示。 开关接在P1.1口线,LED接P1.0口线; 开关断开时,P1.1为+5V,对应数字量为“1”; 开关合上时,P1.1电平为0V,对应数字量为“0”。 这样,可以用JB指令对开关状态进行检测 。

DSP: MOV DPTR,#TAB1

MOVC A,@A+DPTR MOV P1,A RET TAB1:DB 3FH,06H,5BH,4FH,66H DB 6DH,7DH,07H ; “0~4”的字形码 ; “5~7”的字形码 ;查字形码表1 ;送P1口输出

34

例2:如图接有五个共阴极数码管的动态显示接口电路, 用74LS373接成直通的方式作驱动 电路,阴极用非 门74LS04反相门驱动,字形选择由P1口提供,位选 择由P3口控制。当P3.0~P3.4轮流输出1时,五个数 码管轮流显示。P1.7接开关,当开关打向位置“1”时, 显示“12345”字样,当开关打向“2”时,显示 “HELLO”字样。

6

四个端口的结构的相同之处: 都有两个输入缓冲器,分别受内部读锁存器和读引脚 控制信号的控制。

都有锁存器(即专用寄存器PO~P3) 都是场效应管输出驱动。

依据每个端口的不同功能,内部结构亦有不同之处, 以下重点介绍不同之处。

7

结构:P0口的输出驱动电路由上拉场效应管T1和驱 动场效应T2组成,控制电路包括一个与门, 一个非 门和一个模拟开关MUX。

30

LED数码管每段需10~20mA的驱动电流,可用TTL 或CMOS器件驱动。 字形码的控制输出方式 硬件译码方式:如采用BCD7段译码/驱动器 74LS48、74LS49、CD4511-- (共阴极)

74LS46、74LS47、CD4513-- (其阳极)

软件查表方式

31

软件查询数码管显示有静态接口与动态接口两种方式 静态接口—一个并行口接一个数码管,占用引脚多。 固定显示。 动态接口—段选共同接到一个并行口,每个数码管的 com端接不同的引脚上。循环显示。

14

P1口仅作通用I/O口使用,并且输出驱动部分接有上拉电 阻。 当作输入时,使用同P0一样, 要先对该口写“1”。

读锁存器 1 内部总线 写锁存器 P1.x 锁存器 CL 2 读引脚 (b)P1口位结构

15

Vcc

内部上拉电阻 Q T P1.x 引脚

D

P2口作通用I/O口时,多路开关MUX倒向左边; P2口作为高8位地址线时,MUX倒向右边。 注意:当P2口的某几位作地址线使用时,剩下的P2口线 不能作I /O口线使用。 P2口的位结构比P1多了一个转

彭周华 zhouhuapeng@

1

4.1

单片机的并行接口P0-P3

4.1.1 PO-P3接口的功能和内部结构 4.1.2 编程举例 4.1.3 用并行口设计LED显示与键盘电路 4.1.4 并行接口小结 4.2 MCS-51单片机的中断系统 4.2.1 8XX51中断系统结构

4.2.2 中断响应过程

19

如果单片机需要扩展外部存贮器。 P0口作AD0-AD7, P2口作A8-A15,P3口的某些 口线(/RD, /WR)作第二功能(控制线)使用。

P2 P0 ALE /PSEN

A8A15

AD0AD7

锁 存 器

A0A7

地址总线A0A15

D 0 D 7

控制总线

数据总线D0D7

8051

22

CLR P1.0 AGA: SETB P1.1 JB P1.1,LIG SETB P1.0 SJMP AGA LIG: CLR P1.0 SJMP AGA END

;使发光二极管灭 ;先对P1口写入“1” ;开关断开,转LIG ;开关闭合,二极管亮

P1.0 89C51 89S51 P1.1

LED +5V 1K K

LED正偏时才能发亮,按电路接法:

当P1.0输出“1”, 当P1.0

LED正偏而发亮;

输出“0”,LED 的两端电压为 0 而熄灭。

21

+5V 10uF

Vcc -EA RST

LED P1.0 +5V 89C51

1K 1K

30P

XTAL1 30P P1.1

XTAL2 GND

K

开关合上,LED 亮; 开关打开,LED熄灭。

8

CPU发控制电平“0”,封锁与门,使T1管截止,同时 使MUX开关同下面的触点接通,使锁存器的\Q与T2栅 极接通。

9

CPU向端口输出数据。写脉冲加在CL上、数据通过内部总 线经D锁存器和T2反相,从P0口的这一位引脚上输出。

P0作I/O口使用时应外接10K的上拉电阻。

10

输入操作时有两个三态缓冲器用于读操作。 缓冲器2用于读端口引脚的数据。当执行端口读指令时,读引 脚脉冲打开三态缓冲器2,于是端口引脚数据经三态缓冲器2送 到内部总线。 缓冲器1用于读取锁存器Q端的数据。执行“读-修改-写”指令 (ANL P0,A),即是读锁存器Q的数据。

29

显示 字符

0 1 2 3 4 5 6 7 8 9 A B C D E F H P

段

dp 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 g 0 0 1 1 1 1 1 0 1 1 1 1 0 1 1 1 1 1 f 1 0 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 e 1 0 1 0 0 0 1 0 1 0 1 1 1 1 1 1 1 1

27

LED的管脚排列见图(a)。其中COM为公共点; 根据内部的接线形式,可分成共阴极型图(b)和共阳 极型图(c)。

com a b c d a b c d e f g dp

com

e f

g

(a)

(b)

dp

(c)

28

LED数码管的a ~ g七个发光二极管因加正电压而发 亮,加零电压而不能发亮,不同亮暗的组合就能形成不 同的字形,这种组合称之为字形码。 显然共阳极和共阴极的字形码是不同的,其字形码见 下表。

符

d 1 0 1 1 0 1 1 0 1 1 0 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 1 1 0 1 0 0 0 0 c

号

b 1 1 1 1 1 0 0 1 1 1 1 0 0 1 0 0 0 1 a 1 0 1 1 0 1 1 1 1 1 1 0 1 0 1 1 1 1

;高四位亮,低四位送“1” ;读P1口引脚开关状态至A ;低四位开关状态转换到高四位 ;保留高四位 ;从P1口输出 ;循环

26

键盘和显示器是单片机应用系统中常用的输入输出装置。 LED数码管是常用的显示器之一,下面介绍用单片机并行 口如何设计LED数码显示控制电路。 1. LED显示器工作原理 LED有着显示亮度高,响应速度快的 特点,最常用的是七段式LED显示器, 又称数码管。 七段LED显示器内部由七个条形发光 二极管和一个小圆点发光二极管组成, 根据各管的亮暗组合成字符。

23

电路图中二极管亮度不够。

P1.0 89C51 LED

下面两种电路,可增加驱动能力使得二极管更亮些。 1、接成灌电流形式

P1.0 LED +5V

2、加驱动电路

P1.0

1

LED

+5V

24

例2:如图所示,P1.0~P1.3接四个开关, P1.4~P1.7接四 个发光二极管,编程将开关的状态反映到发光二极管上。

读锁存器 1 内部总线 写锁存器 D Q P3.x 锁存器 CL 2 读引脚 第二输入功能 第二输出功能 Vcc

内部上拉电阻 P3.x 引脚

3 4

T

(d)P3口位结构

17

输入时,引脚的信号通过三态缓冲器4进入第二输入功能端。 两种功能的引脚输入都应使T截止。 注意:P3的各位根据需要设定。 把几条引脚设为第二功能, 剩下的引脚可作I/O使用,采用位操作形式。

11

读锁存器是为了避免错读引脚的电平信号。 究竟读引脚还是读锁存器,CPU内部会自行判断是发读引 脚脉冲还是读锁存器脉冲。

12

注意:当P0作输入端口使用时,应先对该口写入“1” 使场效应管T2截止,再进行读入操作,以防场效应管 处于导通状态,使引脚箝位到零,而引起误读。

13

内部控制信号为“1”,转换开关MUX打向上面的触点, 使反相器的输出端和T2管栅极接通。 输出的地址或数据:信号通过与门驱动T1管,同时通过 反相器驱动T2管完成信息传送 输入的数据通过缓冲器进入内部总线。

十六进制代码 共阴 3F H 06 H 5B H 4F H 66 H 6D H 7D H 07 H 7F H 6F H 77 H 7C H 39 H 5E H 79 H 71 H 76 H F3 H 共阳 C0 F9 A4 B0 99 92 82 F8 80 90 88 83 C6 A1 86 84 FF BF

4.2.3 中断的程序设计 4.3 小 结

2

接口电路:CPU与外设设备之间的电路。 功能: 解决总线使用冲突、协调快速CPU与慢速外设。 分类:并行接口、串行接口、定时/计数器、A/D、 D/A等。 MCS-51单片机有P0、P1、P2、P3四个8位双向 I/O口,四个口共32根端口线,每个端口可以按字节 输入或输出,也可以按位进行输入或输出。 P0口为三态双向口能带8个TTL电路; P1、P2、P3口为准双向口,负载能力为4个TTL电 路。

3

4.1.1.1 PO-P3接口功能 P0-具有双重功能 1. 作为输入/输出(I/O)口。 2. 作为地址/数据复用总线,P0口分时输出低 8 位地址 (A0-A7)与数据信号(D0-D7)。