数字逻辑设计分析题

数字电路与逻辑设计习题及参考答案

数字电路与逻辑设计习题及参考答案一、选择题1. 以下表达式中符合逻辑运算法则的是 D 。

·C=C 2 +1=10 <1 +1=12. 一位十六进制数可以用 C 位二进制数来表示。

A . 1 B . 2 C . 4 D . 163. 当逻辑函数有n 个变量时,共有 D 个变量取值组合?A. nB. 2nC. n 2D. 2n 4. 逻辑函数的表示方法中具有唯一性的是 A 。

A .真值表 B.表达式 C.逻辑图 D.状态图5. 在一个8位的存储单元中,能够存储的最大无符号整数是 D 。

A .(256)10 B .(127)10 C .(128)10 D .(255)106.逻辑函数F=B A A ⊕⊕)( = A 。

C.B A ⊕D. B A ⊕ 7.求一个逻辑函数F 的对偶式,不可将F 中的 B 。

A .“·”换成“+”,“+”换成“·” B.原变量换成反变量,反变量换成原变量 C.变量不变D.常数中“0”换成“1”,“1”换成“0” 8.A+BC= C 。

A .A+B +C C.(A+B )(A+C ) +C9.在何种输入情况下,“与非”运算的结果是逻辑0。

DA .全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是1 10.在何种输入情况下,“或非”运算的结果是逻辑1。

AA .全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为111.十进制数25用8421BCD 码表示为 B 。

101 010112.不与十进制数()10等值的数或代码为 C 。

A .(0101 8421BCD B .16 C .2 D .813.以下参数不是矩形脉冲信号的参数 D 。

A.周期 B.占空比 C.脉宽 D.扫描期 14.与八进制数8等值的数为: BA. 2B.16C. )16D. 215. 常用的BCD码有 D 。

A.奇偶校验码B.格雷码码 D.余三码16.下列式子中,不正确的是(B)+A=A B.A A1⊕=⊕=A ⊕=A17.下列选项中,______是TTLOC门的逻辑符号。

数字逻辑设计习题参考答案 (第2章)

数字逻辑设计习题册班级:学号:姓名:哈尔滨工业大学(威海)计算机科学与技术学院体系结构教研室第2章 逻辑代数基础2—1 填空1.摩根定理表示为:=⋅B A _B A +__;=+B A _B A ⋅__。

2. 函数表达式D C AB Y ++=,则其对偶式为='Y _D C B A ⋅⋅+)(_______。

3.根据反演规则,若C D C B A Y +++=,则=Y C D C B A ⋅++)(。

4.函数式CD BC AB F ++=写成最小项之和的形式结果为()15,14,113,12,11,7,6,3∑m ,写成最大项之积的形式结果为)10,9,8,5,4,2,1,0(∏M。

5. (33.33)10 =(100001.0101 )2 =( 41.2 )8 =( 21.5 )162—2 证明1.证明公式()()A BC A B A C +=++成立。

2.证明此公式B A B A A +=+成立。

3.证明此公式)()()()()(C A B A C B C A B A +⋅+=+⋅+⋅+成立。

左边 (由分配律得)右边BCA BCB C A BC BA AC AA C A B A +=+++=+++=++)1())((BA A AB B B A B A B A AB AB B A B A AB BA B B A +=+++=+++=++=++=)()()(ACBC A B C A AC B C A C B B A ++=+⋅+=+⋅+⋅+=)()()()()(ACBC A B BC A B AC A A ++=+++=4. 证明此公式1))(((=+++⋅++C B D B A C B D C C B A 成立。

左边5.证明此公式D C D C B A D AC D C B D C A ⊕=+++⊕)(成立。

左边2—3 用代数法化简下列各式 1.B A BC A F +=1 2.D C A ABD CD B A F ++=2F 1 F 23.CD D AC ABC C A F +++=3 F 34.)()(4C B A C B A C B A F ++⋅++⋅++=F 41))((0))((=+++=+++⋅=C B D B A C B C B D B A C B D C C B A DC DC BD C D C D C A D C B D C A D AC D C A D C B D C A D AC A B D C D C A D AC B A B D C D C A ⊕=++=⊕++⊕=+++⊕=+++⊕=+++⊕=)()()()()()()(1=++++=B A C B A ADC B C B AD C B C B AD =+=++=)()(CDA CDC B C A CD AC AB C A D A C B C A D D A C BC C A +=+++=+++=+++=+++=)()()()()(CB AC B C B A A C A C B A C A C B A +=++=++=+++=)()(x y x y x =+⋅+)()(5.C DE C BE CD B B A AC F ++++=5F 56.C B A AD C B A CD AB F ++++=6F 67.D BC A BD A BD CD B B A C A F +++++=7F 78. D D C C A B A F +++=8F 8 1=++++=D D C C A B A9. D AC D C A D C B D C D C A F ++++=)(9F 9CE B AC CE D B B AC C E D B AC B AC C E D B C A B AC C E D B D B C B B A AC C E D B D C B B A AC ++=+++=+++=++++=++++=+++++=)()()(DC B A AD B C AB AD D C B C AB AD A A C B D C AB +++=++++=++++=+++++=)()(1)()()()()(=++++=+++++=+++++=+++++=+++++=+++++=A CD B BD A C A A CD B BD B B A C A A CD B B A D A B C A A CD B B A BD D B A C A A BD CD B B A D B C A BD A BD CD B B A D BC C A DC D C D C B D C D C D C D C A D C B D C D C A +=++=++++=)()(10.D B AB C D B AB F +++++=10(y x y x x +=+)2—4用卡诺图化简下列各式1.C B A AB C B F ++=1 2.C B BC B A F ++=2F 1ABC += F 2B A +=3.C B C B C A C A F +++=3F 3C B B A C A ++=4.D C A C B AD C D C A ABD ABC F +++++=4D A F +=4111111111111AB CD0001111000011110D B AB C DB ABCD B AB ++=++⋅⋅=5.D B A AC C B A F ++=5 6.C B A AD C B A D C AB F ++++=6AC D B B A F ++=5 A C B DC F ++=6 7.D BC A BD A CD B B A C A F +F 7=18.D B D B C A C A F +++=8D)⊙(B C)⊙(8⋅=+++=A D C B A ABCD D C B A D C B A F11111111AB CD 00011110000111109.D C B A D AC D C B D C A F +++⊕=)(9D C D C F +=9 10. ))((10C AB B A F ++=C B C A F +=1011. C B AC D C A B A F +++=11AC C B B A F ++=1112.∑=mC B A P )7,6,5,2,1,0(),,(1AC C B B A P ++=2 13.=D C B A P )14,11,10,9,8,7,6,4,3,2,1,0(),,,(2D C C A D A B P +++=2 14.∑=mD C B A P )15,14,13,12,10,9,8,6,4,1,0(),,,(3D A D B C B AB D C P ++++=315. ∑=m D C B A P )15,14,13,11,9,7,6,5,3,1(),,,(4F 15=D+BC2—5 用卡诺图化简下列带有约束条件的逻辑函数 1.∑∑+=d mD C B A P )15,14,13,2,1,0()12,11,9,8,6,3(),,,(1CD A D B C A P ++=1 2.∑∑+=d mD C B A P )15,14,13,10,9,8()12,11,6,5,4,3,2,0(),,,(2C B C BD P ++=23.D C B A D C B A D C A P ++++=3, 约束:0=+AC ABD C B D C A D C A P ++=34.CD B A CD B A P +=4, 约束:A B C D 为互相排斥的一组变量,即在任何情况下它们之中不可能两个同时为1。

数字逻辑考题及答案

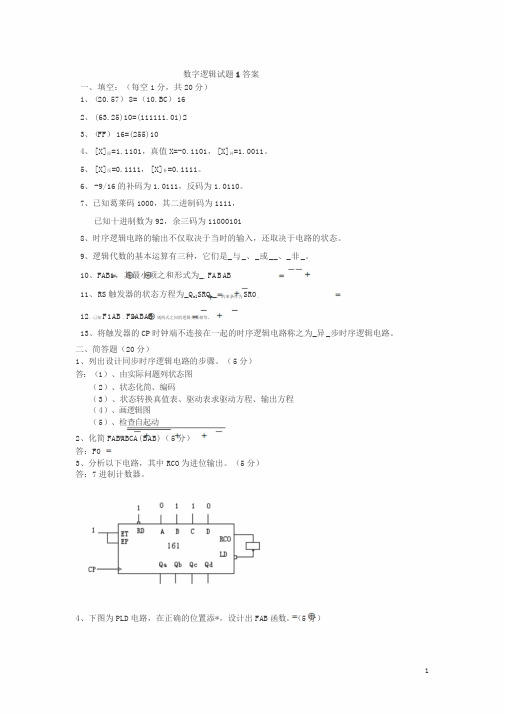

数字逻辑试题1答案一、填空:(每空1分,共20分)1、(20.57)8=(10.BC)162、(63.25)10=(111111.01)23、(FF)16=(255)104、[X]原=1.1101,真值X=-0.1101,[X]补=1.0011。

5、[X]反=0.1111,[X]补=0.1111。

6、-9/16的补码为1.0111,反码为1.0110。

7、已知葛莱码1000,其二进制码为1111,已知十进制数为92,余三码为110001018、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态。

9、逻辑代数的基本运算有三种,它们是_与_、_或__、_非_。

10、FAB1,其最小项之和形式为_。

FA B AB11、RS触发器的状态方程为_Q n1SRQ n_,约束条件为SR0。

12、已知F1AB、F2ABAB,则两式之间的逻辑关系相等。

13、将触发器的CP时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路。

二、简答题(20分)1、列出设计同步时序逻辑电路的步骤。

(5分)答:(1)、由实际问题列状态图(2)、状态化简、编码(3)、状态转换真值表、驱动表求驱动方程、输出方程(4)、画逻辑图(5)、检查自起动2、化简FABABCA(BAB)(5分)答:F03、分析以下电路,其中RCO为进位输出。

(5分)答:7进制计数器。

4、下图为PLD电路,在正确的位置添*,设计出FAB函数。

(5分)15分注:答案之一。

三、分析题(30分)1、分析以下电路,说明电路功能。

(10分)解:XY m(3,5,6,7)m(1,2,4,7)2分ABCiXY0000000101010010111010001101101101011111该组合逻辑电路是全加器。

以上8分2、分析以下电路,其中X为控制端,说明电路功能。

(10分)解:FXA B C XABCXABCXABCXABCXABC4分FX(ABC)X(A B C ABC)4分所以:X=0完成判奇功能。

数字逻辑考题与答案解析

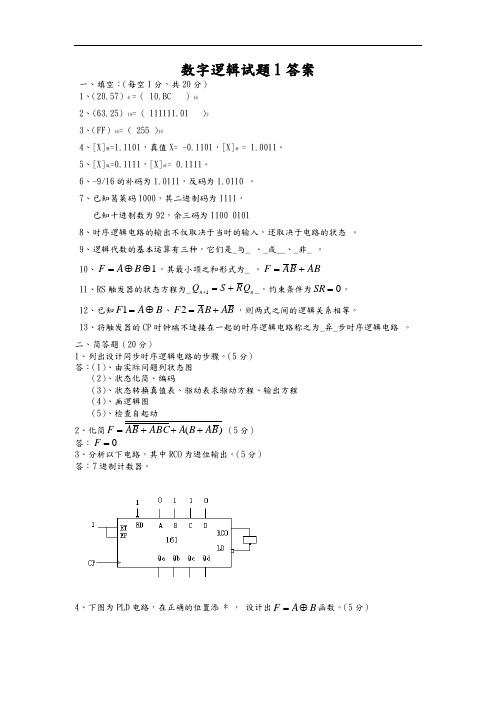

数字逻辑试题1答案一、填空:(每空1分,共20分)1、(20.57)8 =( 10.BC )162、(63.25) 10= ( 111111.01 )23、(FF )16= ( 255 )104、[X]原=1.1101,真值X= -0.1101,[X]补 = 1.0011。

5、[X]反=0.1111,[X]补= 0.1111。

6、-9/16的补码为1.0111,反码为1.0110 。

7、已知葛莱码1000,其二进制码为1111,已知十进制数为92,余三码为1100 01018、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态 。

9、逻辑代数的基本运算有三种,它们是_与_ 、_或__、_非_ 。

10、1⊕⊕=B A F ,其最小项之和形式为_ 。

AB B A F +=11、RS 触发器的状态方程为_n n Q R S Q +=+1_,约束条件为0=SR 。

12、已知B A F ⊕=1、B A B A F +=2,则两式之间的逻辑关系相等。

13、将触发器的CP 时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路 。

二、简答题(20分)1、列出设计同步时序逻辑电路的步骤。

(5分)答:(1)、由实际问题列状态图(2)、状态化简、编码(3)、状态转换真值表、驱动表求驱动方程、输出方程(4)、画逻辑图(5)、检查自起动2、化简)(B A B A ABC B A F +++=(5分)答:0=F3、分析以下电路,其中RCO 为进位输出。

(5分)答:7进制计数器。

4、下图为PLD 电路,在正确的位置添 * , 设计出B A F ⊕=函数。

(5分)5分注:答案之一。

三、分析题(30分)1、分析以下电路,说明电路功能。

(10分)解:∑∑==)7,4,2,1()7,6,5,3(mYmX2分A B Ci X Y0 0 0 0 00 0 1 0 10 1 0 0 10 1 1 1 01 0 0 0 11 0 1 1 01 1 0 1 01 1 1 1 18分2、分析以下电路,其中X为控制端,说明电路功能。

数字逻辑设计习题参考答案(第4章)

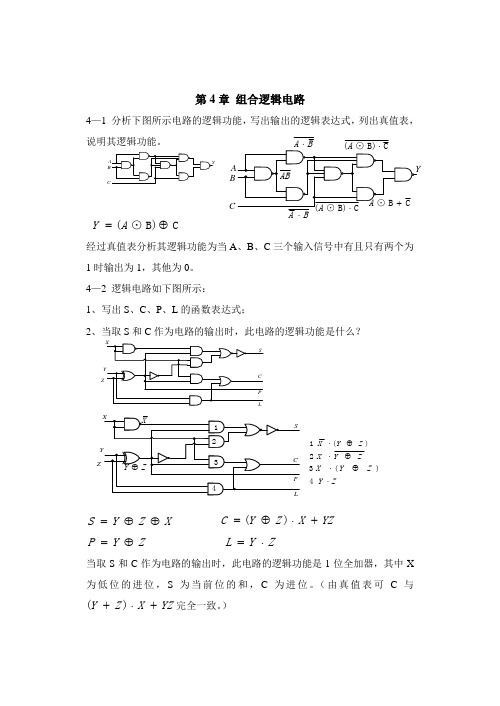

第4章 组合逻辑电路4—1 分析下图所示电路的逻辑功能,写出输出的逻辑表达式,列出真值表,说明其逻辑功能。

C B)⊙(⊕=A Y经过真值表分析其逻辑功能为当A 、B 、C 三个输入信号中有且只有两个为1时输出为1,其他为0。

4—2 逻辑电路如下图所示: 1、写出S 、C 、P 、L 的函数表达式;2、当取S 和C 作为电路的输出时,此电路的逻辑功能是什么?X Z Y S ⊕⊕= YZ X Z Y C +⋅⊕=)(Z Y P ⊕= Z Y L ⋅=当取S 和C 作为电路的输出时,此电路的逻辑功能是1位全加器,其中X 为低位的进位,S 为当前位的和,C 为进位。

(由真值表可C 与YZ X Z Y +⋅+)(完全一致。

)ZB CBA ⋅CB)⊙(⋅A Z)(Z Y X ⊕⋅ZY X ⊕⋅)(Z Y X ⊕⋅ZY ⋅12344—3 下图是由三个全加器构成的电路,试写出其输出1F ,2F ,3F ,4F 的表达式。

Z Y X F ⊕⊕=1 Z Y X F ⋅⊕=)(2Z XY Z XY F +⋅=3 XYZ F =44—4 下图是由3线/8线译码器74LS138和与非门构成的电路,试写出1P 和2P 的表达式,列出真值表,说明其逻辑功能。

ABC C B A m m m m Y Y P +⋅⋅=+=⋅=⋅=70707016543216543212m m m m m m Y Y Y Y Y Y P +++++=⋅⋅+⋅⋅=C B C A B A ++=P1的逻辑功能为当三个输入信号完全一致时输出为1。

P2的逻辑功能为当上输入信号不完全一致时输出为1。

4—5使用74LS138 译码器及少量门电路对三台设备状态进行监控,由不同指示灯进行指示。

当设备正常工作时,指示灯绿灯亮;当有一台设备出故障时,指示灯红灯亮;当有两台设备出故障时,指示灯黄灯亮;当有三台设备出故障时,指示灯红灯和黄灯都亮。

1234解:设输入变量A 、B 、C 分别对应三台设备的状态,0表示故障,1表示正常;输出变量X 、Y 、Z 表示绿、黄、红三个灯的亮灭,0表示灭,1表示亮,根据题意可得真值表如下:设ABC 分别连入74LS138的A 2A 1A 0 由真值表得 42104210Y Y Y Y m m m m Y ⋅⋅⋅=+++=6530Y Y Y Y Z ⋅⋅⋅=4—6 下图3.6是由八选一数据选择器构成的电路,试写出当1G 0G 为各种不同的取值时的输出Y 的表达式。

数字逻辑设计试题(6)

数字逻辑电路试题(卷)一、填空题(20分)1.数字电路只能处理__________信号,不能处理__________信号。

2.逻辑代数有__________、__________和__________三种基本运算。

3.每个触发器可记录__________位二进制码,因为它有__________个稳态。

4.对由与非门组成的基本R—S触发器,当R=__________,S=__________时触发器保持原状态不变。

5.组合逻辑电路的竞争冒险是__________和__________而引起的。

6.时序逻辑电路按其状态改变是否受统一时钟信号控制可将其分为__________和__________两种类型。

7.D/A转换器是将__________信号转换为__________信号。

8.二进制数10111111对应的八进制数为__________,十进制数为__________,十六进制数为__________。

9.两输入与非门的输入为0、1时,输出为__________。

10.两输入或非门的输入为0、1时,输出为__________。

二、选择题(20分)1.下列信号中,是数字信号的为()A.交通灯状态B.交流电压C.直流电压D.无线电波2.n个变量可构成最大项的个数为()A.n B.2n C.2 n D.2 n-13.逻辑函数F1=A○+B和F2=A⊙B满足()A.F1′=F2B.F1= F2○+1 C.F1= F2D.F1=F2′4.J—K触发器在时钟脉冲CP作用下,要使Q n+1=Q n,则输入信号必为()A.J=K=0 B.J=1,K=1 C.J=Q,K=Q D.J=Q,K=15.组合逻辑电路输出与输入的关系不能用()描述A.真值表B.卡诺图C.状态图D.逻辑函数表达式6.PAL是指()A.可编程逻辑阵列B.可编程阵列逻辑C.通用阵列逻辑D.只读存储器7.F(A.B.C.D)= BCD,它包含最小项的个数为()A.2 B.3 C.4 D.58.与二进制码10110对应的格雷码为()A.11001 B.11110 C.11101 D.111009.F(A,B,C,D)=CD,它含最大项的个数为()A.4 B.8 C.12 D.1610.用八选一数据选择器实现逻辑函数F=A B C+A C+ABC,其数据输入端D4为()A.B B.C C.1 D.0三、是非题(正确的在括号中打“√”,错误的打“×”,10分)1.10位二进制代码能表示的最大十进制数为1024。

数字逻辑设计试题(8)

数字逻辑电路试题(卷)一、填空题(20分)1.逻辑函数表达式有标准__________和标准__________两种标准形式。

2.逻辑函数F=AB+AB 的反函数F =__________对偶式F '=_________。

3.逻辑函数F=B C D +A B+AB C D+BC 的最小项之和形式F=∑m (__________),最大项之积形式F=∏M(__________)。

4.组合逻辑电路在任何时刻的稳定输出信号取决于__________。

5.模—数转换器按其工作原理可分为__________式和__________式两大类。

6.典型的PLD 由一个__________后跟一个__________组成。

7.移位寄存器是用来存放__________并能对所存放的 __________ 的逻辑部件。

8.卡诺图最大特点是具有__________。

9.将J —K 触发器转换为D 触发器,其J=__________,K=__________。

10.集成触发器的工作速度由最高工作频率决定,按最高工作频率的典型值可确定最快的为__________门电路,其次为__________门电路,最慢的为__________门电路。

11.输出仅与电路当时的状态有关,与电路当时的输入无关的时序逻辑电路称为__________型电路。

二、选择题(20分)1.和八进制数(76)8 等值的十进制是( )A .(62)10B .(76)10C .(64)10D .(60)102.十进制数769.2对应的8421码是( )A. 10010010010.0010B. 011101101001.0010C. 111001101001.0100D. 011101101001.01003.和二进制数10110对应的余3码为( )A. 10110B. 01101C. 11001D. 111014.ABD(ABC+A B D+A B C)=( ) A. 1 B. A C. A D. 05.用八选一数据选择实现函数F=∑m(0.1.7.9.11.12) ,若将 A 、B 、C 作为选择输入变量看待,则D3=( )A. D B . D C. 1 D. 06.如图2.6电路,若两个电路等效,其输入变量A 、B 的取值( )A. 相反B. 相同C. 不同D. 无法确定A AB F 1 F 2B图2。

数字逻辑设计第6章 时序逻辑电路习题与解答

L’/C 为 1 时,装入无效,161 对输入的 CLK 进行计数。 L’/C 为 1 或为 O 时,装入有效,而装入值为 D3=Q2,D2=Q1,D1=Q0,D0=串 行输入数据,所以该电路的功能将数据左移,低位补的是串行输入数据。 6-11 试分析图 6-74 的计数器在 C=1 和 C=0 时各为几进制计数器?

第 6 章 习题

6-1 说明时序电路和组合电路在逻辑功能和电路结构上有何不同?

题 6-1 答:

逻辑功能上,时序电路任一时刻的输出不仅取决于当时的输入,而且与电路 的原状态有关。

结构上的特点有两点: (1)时序电路中包含存储元件,通常由触发器构成。 (2)时序电路的存储元件的输出和电路输入之间存在着反馈连接。

Q2Q1Q0

000

/0

/1

001

/0

010

/0

101

/0

100

/0

011

由状态转换图可画出 Q2Q1Q0 和输出 F 的状态卡诺图如下:

Q1Q0 Q2 00 01 11 10

00

0

10

Q1Q0

Q2

00

01 11 10

00

10

0 10

11 0 X X

(a)Q2 卡诺图

Q1Q0 Q2 00 01 11 10

6-3 试分析图 6-69 所示时序逻辑电路的逻辑功能,写出电路的驱动方程、状态 方程和输出方程,画出电路的状态转换图。

F

FF0

DQ >C 1 Q

CLK

FF1

DQ >C 1 Q

图 6-69

题 6-3 解:根据图 6-69 可写出如下驱动方程:

数字逻辑电路设计题目

课题一交通灯控制逻辑电路设计一、概况为了确保十字路口的车辆顺利、畅通地通过, 往往都采用自动控制的交通信号灯来进行指挥。

其中红灯(R)亮表示该条道路禁止通行;黄灯(Y)亮表示停车;绿灯(G)亮表示允许通行。

1.1 交通灯控制器系统框图二、设计任务和要求1.设计一个十字路口交通信号灯控制器, 其要求如下:2.满足如图1.2顺序工作流程。

图中设南北方向的红、黄、绿灯分别为NSR、NSY、NSG, 东西方向的红、黄、绿灯分别为EWR、EWY、EWG。

它们的工作方式, 有些必须是并行进行的, 即南北方向绿灯亮, 东西方向红灯亮;南北方向黄灯亮, 东西方向红灯亮;南北方向红灯亮, 东西方向绿灯亮;南北方向红灯亮, 东西方向黄灯亮。

t为时间单位图1.2 交通灯顺序工作流程图. 2.应满足两个方向的工作时序: 即东西方向亮红灯时间应等于南北方向亮黄、绿灯时间之和, 南北方向亮红灯时间应等于东西方向亮黄、绿灯时间之和。

时序工作流程图见图3.3所示。

图3.3中, 假设每个单位时间为3秒, 则南北、东西方向绿、黄、红灯亮时间分别为15秒、3秒、18秒, 一次循环为36秒。

其中红灯亮的时间为绿灯、黄灯亮的时间之和, 黄灯是间歇闪耀。

467891011112503462503tNSG图1.3 交通灯时序工作流程图3.十字路口要有数字显示, 作为时间提示, 以便人们更直观地把握时间。

具体为: 当某方向绿灯亮时, 置显示器为某值, 然后以每秒减1计数方式工作, 直至减到数为“0”, 十字路口红、绿等交换, 一次工作循环结束, 而进入下一步某方向的工作循环。

例如: 当南北方向从红灯转换成绿灯时, 置南北方向数字显示为18, 并使数显计数器开始减“1”计数, 当减到绿灯灭而黄灯亮(闪耀)时, 数显得值应为3, 当减到“0”时, 此时黄灯灭, 而南北方向的红灯亮;同时, 使得东西方向的绿灯亮, 并置东西方向的数显为18。

4.可以手动调整和自动控制,夜间为黄灯闪耀。

数字逻辑设计试题(4)完成

1、逻辑变量的取值有_______ 、________2、基本的逻辑门电路有___________ ____________ ____________3、若将输入变量的全部组合和对应的输出函数列成的表格称为____________4、最简单的逻辑函数表达式的条件为___________、5、F(A.B.C)=BC它包含了_______个最大项。

6、F=AB(BC+AD+B)=_____________7、F=A+B+C+D的表达式称为___________表达式。

8、用0、1组成一串数码代表某个具有特定含义信息的过程称_________9、如图1.9电路称为_________10、PAL器件由一个_________和一个固定___________组成,中文名字称为_________11、DAC是将_________信号转换为___________信号的电路。

12、时序逻辑电路根据时钟脉冲源可分为______ 和_________电路二、选择题(20分)1、和二进制数(10001010.1)等值的十六进制数()A (8 A.8) 8B (212.2)8 C. (76.8)8 D. (92.8)82、和二进制数(100101)2对应的格雷码()A. 101010B. 110111C. 101000D. 1101103、和8421BCD码(100010010011.0011)对应的十进制数为()A. 893.3B. 896.7C. 893.6D. 983.74、F(ABC)=ABC+A BC+A B C+A B C的最大项为( )A. ΠM(0.2.4.7)B. ΠM(1.3.5.7)C.ΠM(0.2.4.6)D.ΠM(0.2.3.6)5、F=(A+B)(A+C)的反演式为()A. F=A B+A CB. F=A B+A CC. F=A B+A CD. F=A+BC6、对负逻辑而言,电路为与非门,对正逻辑而言为()A. 与门B. 或门C. 或非门D. 异或门7、D触发器在同步工作时,Q n=0要求达到Q n+1=1, 则D应为()A. 0B. 1C. 0或1 D 无法确定8、1个具有n位地址码输入,m位数据输出的ROM其存贮容量为()A. n×mB. 2n×mC. 2m×nD. 2m9、A·A·B·C·B=( )A. BB. AC. CD. 010、如图2.10为()A 三位同步二进制加法计数器 B. 三位同步二进制减法计数器C. 三位异步二进制加法计数器D. 三位异步二进制减法计数器三、改错题(指出错误并改正10分)1、两个n位二进制相加,第i位被加数为A i,加数为B i相邻低位进位为C i-1,则第i位的本位和S i的表达式为S i=A i B i C i+A i B i C i-1+A i B i C i-1+A i B i C i-1改正表达式为:2、只读存储器是由与阵列构成3、某一RAM器中,某同学说,它是只能读出而不能写入的一种存储器4、竞争冒险是由于门电路的延迟而产生的5、MUX称为数据分配器,也称为多路选择开关四、化简题(10分)1、用代数法化简F=A+C+A·B+C+B+C+AB C+A B C2、用卡诺图化简F=A B C+AB C+ABC+B C D五、分析题(本科16分,专科20分)1、如图5.1分析其逻辑功能2、如图5.2有边沿JK触发器组成,分析其逻辑功能六、设计题(本科班做1—3题,24分,专科做1—2题,20分)1、试用与非门设计一个“三变量一致电路”,假设输入信号原变量、反变量都存在2、试将T'触发器转换为J-K触发器,并用与非门转换,画出逻辑电路图3、试设计一个可逆的同步四进制计数器,要求:X=0时进行加法计数, X=1时进行减法计数, 用J-K触发器实现.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2. 分析下图所示的同步时序电路(10分)

1) 写出触发器的输入激励表达式,输出表达式和状态转换表(或状态转换图); 2) 说明该电路实现什么功能?

解:

(a)

010*'

00

*''1111

1110110

1J J Q X

Q Q Q J Q J Q J Q Q Q X Z Q Q ==⊕∴==⋅+⋅=⊕=⊕⊕=⋅

(b) X=0时,电路为四进制加法计数器; X=1时,电路为四进制减法计数器。

四 分析下图所示的组合逻辑电路(12分)

1 画出输出F 对输入Z 的定时关系图(假定输入X 和Y 都保持高电平,且每个门电路都有一个单位时间的延

迟);

2 判定该电路是否存在有静态冒险问题,如果存在静态冒险,请消除它。

10XQ Q **

10Q Q Z

000

01 0 001

10 0 010 11 0 011 00 1 100

11 0 101 00 0 110 01 0 111

10

1

解:

(a) 上图红线 (b) 存在冒险

五 设计并实现一位全减器(12分)

电路实现D=A-B-C 的功能,其中C 是来自低位的借位信号,D 是本位求得的差信号;电路还要产生向高位借位信号P 。

1 采用门电路实现该减法器电路(写出逻辑函数表达式,不做图);

2 采用74x138译码器和少量的逻辑门实现该减法器电路(画出电路图)。

解:

CBA D P 000 0 0 001

1

X Z Y

F

Z

F

010 1 1

011 0 0

100 1 1

101 0 0

110 0 1

111 1 1

六分析下面的电路,完成下面的问题(15分)1根据电路,完成给定的时序图;

2画出其状态转换图或状态转换表。

解:

(1) 上图红线 (2)

210Q Q Q ***

210Q Q Q

000 001 001 010 010 011 011 100 100

001

*'''20122012

*''''''''10102101021*'''''01200120

()1(())()1()Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q =⋅⋅+⋅=⋅⋅=⋅+⋅⋅=⋅+⋅⋅=⋅⋅+⋅=⋅⋅

101 010 110 000 111

000

七 请设计一个序列信号发生器,该电路能在时钟信号CP 作用下,周期性输出“110010”的串行序列信号;要求采用最小风险方法设计;采用D 触发器和必要门电路实现并画出电路原理图。

(10分)。

解:

210Q Q Q F

110 0 100 1 001 0 010 1 101 1 011 0 000 1 111

F 21Q Q

0Q

00 01 11 10 0 1 1 0 1

1

1

''

'0212F Q Q Q Q =⋅+⋅

八 设计一个101序列信号检测器,当输入连续出现101时,输出为1,否则输出为0;要求电路无风险(输入不可重叠,不做图)。

(10分)

例: 输入 1 1 0 1 0 1 0 0 1 1 0 1 1 1 0

输出 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0

解:状态转换表及编码

得到状态方程和激励方程

'

'01Z Q Q A =⋅⋅

*

'01Q Q A =⋅ *'10Q Q A =⋅

画出状态图

无效状态可以回到有效循环,该电路为自启动。

试分析如图所示电路的功能,其初始状态均为零。

解:(1)、此电路为由三个JK 触发器构成的异步时序逻辑电路 (2)

、列方程

CP 时钟方程:CP CP CP ==20,n

Q CP 01=(1分)

驱动方程:1

22111

11`

10020======K Q Q J K J K Q J n n n

(3分)

JK 触发器的特性方程:

n n n Q K Q J Q +=+1

状态方程:n n n Q Q Q 0210=+n n Q Q 111=+n

n n n Q Q Q Q 21012

=+ (3)状态转换表

(4)画状态转换图

此电路为能自启动的异步5进制加法计数器

试分析图3(a)所示时序电路,画出其状态表和状态图。

设电路的初始状态为0,试画出在图3(b)所示波形作用下,Q和Z的波形图。

图3

答案:

2. 试分析图4所示的计数器在M = 1和M = 0时各为几进制。

同步十进制加法计数器74160的功能表如表1所示。

74160

D 0 D 1 D 2 D 3

EP C ET

CLK Q 0 Q 1 Q 2 Q 3

LD R D

1

CLK 计数输入

Y

进位输出

1

M

74160

图4

表1 同步十进制加法计数器74160的功能表

答案:

LD= 0,下一个CLK到达时将D3D2D1D0 = 0010(二)置入电路中,使M=1时,电路进入1001(九)以后'

Q3Q2Q1Q0 = 0010,再从0010继续做加法计数,因此电路在0010到1001这八个状态见循环,形成八进制计数器。

LD= 0,下一个CLK到达时将D3D2D1D0 = 0001(一)置入电路中,使M=0时,电路进入1001(九)以后'

Q3Q2Q1Q0 = 0001,再从0001继续做加法计数,因此电路在0001到1001这九个状态见循环,形成九进制计数器。

3. 试分析下图(图5)所示的同步时序电路,写出各触发器的驱动方程,电路的状态方程和输出方程,画出状态

转换表和状态转换图。

图5 答案:。