2.3 VHDL对象、数据类型及运算符

VHDL的运算符号

VHDL的运算符号VHDL中主要有六类运算符号:赋值运算、逻辑运算、算术运算关系运算、连接运算、移位运算运算符号主要用于各类表达式中;运算可以分为单目运算(只有一个运算量)和双目运算(针对两个运算量);进行双目运算时,两个运算量必须类型相同;VHDL中运算没有左右优先级差别,同一表达式中进行多个运算时必须用括号表达先后差别;在同类运算中,单目运算优先;在所有运算符号中,NOT的优先级别最高;在一般运算中,优先顺序排列为:算术—关系—逻辑可以通过加括号来改变运算的优先顺序;赋值运算符<= 信号赋值:将右端值赋给左端信号;:= 变量赋值:将右端值赋给左端变量;或用于赋初始值;=> 数组内部分元素赋值;适用类型:所有数据类型;赋值号两边的数据类型原则上应该相同;逻辑运算符NOT AND OR NAND NOR XOR适用类型:STD_LOGIC STD_LOGIC_VECTORBIT BIT_VECTOR BOOLEAN逻辑运算结果为同类型逻辑量;对数组类型进行逻辑运算时,参与运算的两个数据位数必须相等,所做运算为对应位进行;算术运算:/ (除)* (乘) + (加)- (减)MOD(求模)REM(取余)**(指数) ABS(绝对值)适用类型:INTEGER REAL BIT BIT_VECTOR TIME加/减运算的结果为同类型算术量;注意:算术运算大多数只用于抽象的编程(行为设计);只有少数算术运算符能够进行综合,应尽量只使用加/减;对数组类型进行算术运算时,两边位数必须相同;关系运算:=> (大于等于)<= (小于等于)> (大于)< (小于) /= (不等于)= (等于)适用类型:等于和不等于适用于所有类型;其他运算适用于整数、实数、位、位矢量,以及枚举类型和数组类型;可比较位长度不相同的情况(从左向右逐位比较);关系运算的结果为boolean类型: false true注意:小于等于符号与信号赋值符号的写法相同,应注意使用位置和意义;连接运算:&适用类型bit bitvector character stringstd_logic std_logic_vector连接运算结果为同类型元素构成的数组;库和包集合除了实体、结构体外的第三种可编程结构Library 库编译后数据的集合,存放包集合定义、实体定义、构造体定义和配置定义,其功能相当于其他操作系统中的目录,经过说明后,设计中就可以使用库中的数据,实现共享;在前面图形输入的应用中,已多次采用库中的单元进行设计;库的使用:当使用库时,需要说明使用的库名称,同时需要说明库中包集合的名称及范围;每个实体都应独立进行库的说明;库的说明应该在实体之前;经过说明后,实体和结构体就可以自动调用库中的资源;库说明语句格式library 库名;use 库名.包集合名.范围(或项目名);例: library ieee;use ieee.std_logic_1164.all;VHDL中库的主要种类:IEEE库STD库ASIC库work库用户定义库IEEE库:含有IEEE的标准包集合“STD_LOGIC_1164”以及一些大公司提供的包集合;使用前必须说明;例:library ieee;use ieee.std_logic_1164.all; 使用标准逻辑量的定义和运算;use ieee.std_logic_unsigned.all; 无符号数算术运算的定义;use ieee.std_logic_arith.all; 使用符号数算术运算的定义;STD库:含有“STANDARD”包集合和“TEXTIO”包集合,使用前者时无需说明;ASIC库:由各公司提供,存放与逻辑门一一对应的实体,用于ASIC 设计的门级仿真,使用时需加以说明;例library altera;use altera.maxplus2.all;library lpm;use lpm.lpm_components.all;WORK库:WORK库为现行作业库,位于当前使用时设计文件的指定保存目录;WORK使用时通常无须说明;但在结构设计中进行元件的宏调用时需要说明;例:use work.all;用户定义库:由用户自定义生成,使用时需说明(指定库所在的路径);package 包集合用于罗列VHDL语言中使用的类型定义、信号定义、常数定义、元件定义、函数定义和过程定义等(类似于C语言中的include语句),方便不同模块的设计中公共定义的共享;数字电路设计中经常使用的包集合:ieee.std_logic_1164 逻辑量的定义ieee.std_logic_arith 数据转换,逻辑判断ieee.std_logic_unsigned 算术运算std.textio 文本数据输入/输出格式包集合在使用前必须采用use语句进行说明(在设计程序的最前面);包集合可以由用户自定义;包的结构与定义:(用户自定义的包集合)包集合标题+(包集合体)包集合标题:package 包集合名 is说明语句;(只有名称)end 包集合名;包集合体:package body包集合名 is说明语句;(完整定义)end 包集合名;例:(函数取自p.279 表4-38 )library ieee;use ieee.std_logic_1164.all;packge upac isconstant k: integer := 4;subtype cpu_bus is std_logic_vector(k-1downto 0); function conv_integer (x:std_logic_vector) return integer; end upac;packge body upac isfunction conv_integer (x: std_logic_vector) return integer is variable result: integer;beginresult := 0;for I in x'range loopresult :=result*2;case x(i) iswhen '0'|'L' => null;when '1'|'H' => result := result+1;when others => null;end case;end loop;return result;end conv_integer;end upac;用户自行编写的包集合将自动存放于WORK库中,使用时可采用下列语句调用use work.upac.all;configuration 配置在一个实体内可以编写多种不同的构造体,通过配置语句来进行选择;配置语句格式:configuration 配置名 of 实体名 isfor 选择的构造体名end for;end 配置名;此语句可以为设计增加更大的灵活性,可以对不同构造体进行比较。

VHDL数据类型(vhdl语法)

注意!变量定义的时候尽管可以直接赋初值,但系统往往忽略。 建议变量对象定义后再进行赋值。

精品课

信号和变量的比较

(1)信号和变量的对应关系不同:信号代表电路内部信号或 连接线路;而变量则不是。

(2)信号和变量声明的位置不同:信号声明在子程序、进程的外 部;而变量声明在子程序、进程的内部。

0); C<= A( 2 downto 1); B<= A(3) & D & ‘1’;

精品课

二、VHDL数据类型与数据对象

数值类型 (1)整数

Type Integer Is Range 231-1

-231 ~

限定整数取值范围的方法: Signal A: Integer; Signal B: Integer Range 0 to 7; Signal C: Integer Range -1 to 1;

end exam1; architecture m1 of exam1 is constant num : integer := 6; begin op <= ip + num; end m1;

精品课

二、VHDL数据类型与数据对象

(2) 信号 定义格式 Signal 信号名称: 数据类型 [:=初始值]; 信号相当于电路内部元件之间的物理连线,因 此信号的赋值有一定的延迟时间.

entity full_bit_adder is port(a,b,ci:in std_logic;

y,cout:out std_logic); end full_bit_adder;

architecture bh1 of full_bit_adder is

begin

(三)VHDL语言的数据类型及运算操作符

【例3-1】 PROCESS( A, B, C, D) BEGIN D<=A; X<=B+D; D<=C; Y<=B+D; END PROCESS; 结果: 结果:X<=B+C; Y<=B+C; PROCESS( A, B, C) VARIABLE D:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN D:=A; X<=B+D; D:=C; Y<=B+D; END PROCESS; 结果: 结果:X<=B+A; Y<=B+C; 信号量的值将进程语句最后所代入的值作为最终代入值。 信号量的值将进程语句最后所代入的值作为最终代入值。而变量 的值一经赋值就变成新的值。 的值一经赋值就变成新的值。这就是变量赋值和信号代入在操作 变量赋值和信号代入在操作 上的区别。 上的区别。

5. 布尔量 布尔量(Boolean) 一个布尔量具有两种状态,“真”或者“假”。虽然 或者“ “ 布尔量也是二值枚举量 二值枚举量,但它和位不同,没有数值的含义 和位不同, 二值枚举量 和位不同 没有数值的含义, 也不能进行算术运算 不能进行算术运算。它能进行关系运算 能进行关系运算。例如,它可以 不能进行算术运算 能进行关系运算 在IF语句中被测试,测试结果产生一个布尔量TRUE或者 FALSE。 一个布尔量常用来表示信号的状态或者总线上的情况 表示信号的状态或者总线上的情况。 表示信号的状态或者总线上的情况 如果某个信号或者变量被定义为布尔量,那么在仿真中将 自动地对其赋值进行核查。这一类型的数据的初始值一般 初始值一般 总为FALSE。 总为

表3-1 VHDL语言 3 类客体含义和说明场合

3.1.1 常数(Constant) 常数 常数是一个固定的值 固定的值。所谓常数说明 常数说明,就是对某一常 固定的值 常数说明 对某一常 数名赋予一个固定的值。通常赋值在程序开始前 数名赋予一个固定的值 程序开始前进行, 程序开始前 该值的数据类型则在说明语句中指明。常数说明的一般 格式如下: CONSTANT 常数名: 数据类型:=表达式; 常数名 数据类型 表达式; 表达式 例如: CONSTANT VCC: REAL:=5.0; CONSTANT DALY: TIME:=100 ns; CONSTANT FBUS: BIT_VECTOR:="0101";

VHDL语言的数据类型及运算

改:只须修改常数就可以替换所有相关数值。

2) 常数说明的一般格式

constant 常数名:数据类型:=表达式;

2020/2/25

5

3) 举例: constant vcc:real:= 5.0; constant delay:time:= 100 ns; constant fbus:bit_vector:=“0101”;

• 客体类别: • 信号(Signal) • 变量(Variable) • 常数(Constant) • 文件(File)

2020/2/25

2

VHDL语言三类客体的含义和说明场合

block

2020/2/25

3

• 电子电路设计中,信号、变量、常数、文件四类客体的 物理含义:

• 信号对应物理设计中的某一条硬件连接线; ➢ 常数对应数字电路中的电源和地等; ➢ 变量的对应关系不太直接,通常用于暂时数据的局部存

6

2. 变量(Variable)

1) 变量的作用 • 变量是局部量,用在进程、函数语句和过程语句

中作为局部的数据存储; • 用于描述算法和方便程序中的数值运算。

2) 变量说明语句的格式 variable 变量名:数据类型 约束条件:=表达式;

2020/2/25

7

3) 举例 variable x,y:integer; variable count:integer range 0 to 255:= 10;

Declared

qa <= r or t; qb <= (qa and not(g xor h));

END ARCHITECTURE logic;

Signal Declaration Inside Architecture

VHDL数据对象数据类型和运算操作符

VHDL数据对象数据类型和运算操作符VHDL (VHSIC Hardware Description Language) 是一种硬件描述语言,用于描述和设计集成电路。

在VHDL中,数据对象是用来存储数据的变量、信号和常量。

数据类型定义了数据对象的属性和行为,而运算操作符则用于对这些数据对象进行操作和计算。

数据对象:1. 变量(variable):变量是可以被修改和赋值的数据对象,其数值可以在运行时发生变化。

变量在使用前必须被声明,并且可以在任意位置被修改。

2. 信号(signal):信号是用于在电路之间传递数据的数据对象,它们是被连接在不同模块之间的通道。

信号的赋值是并行的,即一个信号可以同时接收多个值。

3. 常量(constant):常量是在设计中具有固定数值不可更改的数据对象,其值在设计过程中一直保持不变。

常量必须在声明时赋初值,并且不能在运行时被修改。

数据类型:VHDL中定义了多种数据类型,包括标量类型、复合类型和枚举类型等。

1. 标量类型(scalar type):标量类型表示单个数值,包括整数(integer)、实数(real)和布尔值(boolean)等。

3. 枚举类型(enumeration type):枚举类型表示一组具有命名值的数据对象,比如状态机中的状态值可以用枚举类型表示。

运算操作符:VHDL定义了多种运算操作符,用于对数据对象进行操作和计算,包括算术运算符、逻辑运算符、关系运算符和位运算符等。

1. 算术运算符(arithmetic operator):用于执行基本的数学运算,包括加法(+)、减法(-)、乘法(*)和除法(/)等。

2. 逻辑运算符(logical operator):用于执行逻辑运算,包括与(and)、或(or)、非(not)和异或(xor)等。

3. 关系运算符(relational operator):用于比较两个数据对象的关系,包括等于(=)、不等于(/=)、大于(>)和小于(<)等。

VHDL数据类型和运算符

-(2^31-1) to +(2^31-1) -1.0E+38 to +1.0E+38 ‘0’ ‘1’ “000” true false ‘A’ “abcd” 20 us

2011/6/13

11

VHDL语言的数据类型

整数

整数范围 -(2^31-1) to +(2^31-1)

不能看作矢量, 不能单独对某一位操作

2011/6/13

22

用户定义的数据类型

TYPE 数据类型名 IS 数据类型定义;

枚举类型 数组 记录类型 文件 时间 用户自定义的整数,实数 用户自定义的子类型

2011/6/13

23

用户定义的数据类型

枚举类型

TYPE 数据类型名 IS (元素,元素…..)

Type week IS (sun,mon,tue,wed,thu,fri,sat) Type std_logic IS (‘U’, ‘X’, ‘0’, ‘1’, ‘Z’, ‘W’, ‘L’ ,‘H’, ‘-’) Type bit IS (‘0’, ‘1’)

转换为integer

31

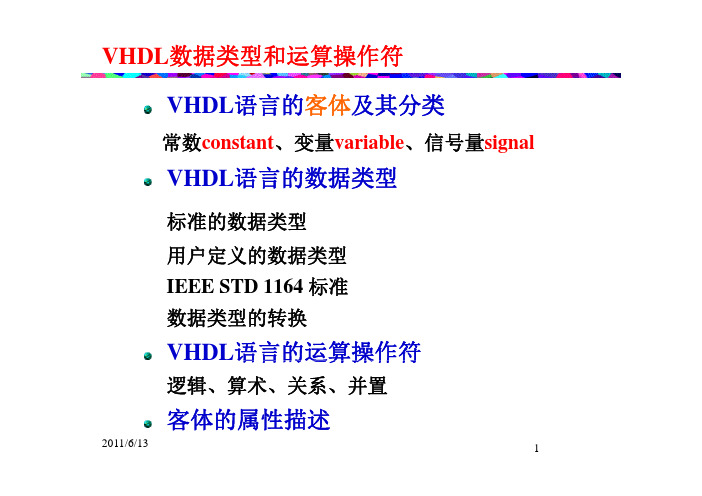

VHDL语言的客体及其分类

常数constant、变量variable、信号量signal

VHDL语言的数据类型

标准的数据类型

用户定义的数据类型

IEEE STD 1164 标准 数据类型的转换

VHDL语言的运算操作符

逻辑、算术、关系、并置

客体的属性描述

2011/6/13

32

(信号的代入)

Signal B : Std_logic; (信号的定义)

B <= ‘Z’;

(信号的代入)

B <= A(0);

VHDL对象 数据类型和运算符

种取值: 位(BIT)数据类型有 种取值:‘0’和‘1’。 )数据类型有2种取值 和 。 例如:这两种数据类型的信号可作如下声明: 例如:这两种数据类型的信号可作如下声明: SIGNAL x: BIT; --将x声明为位 声明为位(BIT)数据 将 声明为位 数据 类型的信号 SIGNAL y: BIT_VECTOR(3 DOWNTO 0); --将y声明为位矢量 将 声明为位矢量 SIGNAL z: BIT_VECTOR(0 TO 3); --将z声明为位矢量 将 声明为位矢量 (BIT_VECTOR)数据类型的信号 位宽 位,最右 数据类型的信号,位宽 数据类型的信号 位宽4位 最右 边的一位是最高位(MSB) 边的一位是最高位

信号与变量的区别

1、使用方式 、 2、作用范围 、 3、赋值符号 、 4、赋值后的变化 、

标准数据类型

STD库的 库的STANDARD包集预定义了位 库的 包集预定义了位 )、布尔 )、整数 (BIT)、布尔(BOOLEAN)、整数 )、布尔( )、 (INTEGER)和实数(REAL)数据类 )和实数( ) 型。 不需要USE语句显示调用 语句显示调用 不需要

整数( 整数(INTEGER) ) 整数与数学中整数的定义相似, 整数与数学中整数的定义相似,可以使用预定义运算 操作符,如加“ 操作符,如加“+”、减“-”、乘“×”、除“÷”进行 、 进行 算术运算。 语言中, 算术运算。在VHDL语言中,整数的表示范围为- 语言中 整数的表示范围为- 2147483647~2147483647,即从-(231-1)到(231-1)。 ~ ,即从- 到 。 实数( 实数(REAL) ) 实数有正负数,书写时一定要有小数点。例如:- :-1.0, 实数有正负数,书写时一定要有小数点。例如:- ,+2.5, , -1.0E+38

EDA VHDL第三章 VHDL数据类型和运算操作符

illegal%name _illegalname 9illegal entity data_ _BUS Not-Ack

上一次课的内容

程序包、库和配置 VHDL四类语言要素:数据对象、词法规则与 标识符 本次课程内容:

数据类型、 运算操作符

扩展标识符

扩展标识符是VHDL‟93版增加的标识符书写规则: (1)用反斜杠来定界,免去了87标准基本标识符的一些限制。 (2) 可以数字打头,允许包含图形符号、空格符。 例如:\mode A, \$100\, \p%name\等。 (3)反斜杠之间的字符可以用关健字。 如:\buffer\, \entity\, \end\等。 (4) 标识符的界定符两个斜杠之间可用数字打头。 如: \100$\,\2chip\,\4screens\等。 (5) 允许多个下划线相连。例:\TWO_Computer_sh\等。 (6) 扩展标识符区分大小写。例如: \EDA\ 与\eda\不同。 (7) 扩展标识符与短标识符不同。 如:\COMPUTER\ 与Computer不同。

3.3.2 词法规则与标识符

1.词法规则 1) 注释 以--开头直到本行末尾(出现回 车或换行符)的文字

提高VHDL语言设计程序的可读性,

1.词法规则

2) 数字

表达方式:十进制,二进制、八进 制、十六进制等为基的数 ①十进制整数表示法 78_567(=78567) ②以基表示的数 格式: 基数符号#数值#指数部分

举例如下: VARIABLE result: std_logic:='0' ; VARIABLE x,y: integer; VARIABLE a:integer range 0 to 255 :=0 ;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VHDL对象:变量

例: Architecture behav of count is begin

process (clk) variable temp: integer range o to 255 := ‘0’; begin

if clk’event and clk=’1’ then temp := temp + 1;

例Hale Waihona Puke :architecture behav of counter is signal count: std_logic_vector (7 downto 0);

begin process (clk) begin if (clk’event and clk=’1’) then if en = ‘1’ then count <= data; else count <= count +1; end if; end if; end process; q<=count;

end if; end process; end behav;

-- 请写出对应的实体说明

VHDL对象:变量

变量:定义进程中或子程序中的变化量

格式: VARIABLE 变量名:数据类型 := 初始值;

例:variable tmp : std_logic := ‘0’;

用途:在PROCESS,FUNCTION,ROCEDURE 中使用,用于描述算法和方便程序中的数值运 算,是一种局部量。

例: constant VCC : real := 5.0; constant delay : time := 10ns; constant fbus : bit_vector := “0101”;

用途:在ENTITY,ARCHITECTURE,PACKAGE, PROCESS,PROCEDURE,FUNCTION中保持静态数据, 以改善程序的可读性,并使修改程序容易。

2.3 VHDL对象、数据类型和运算 符

1、VHDL数据对象

(1)常量 (2)变量 (3)信号 (4)信号与端口的比较 (5)信号与变量的比较

2、VHDL数据类型

(1)标准数据类型 (2)用户定义的数据类型 (3)数据类型转换

3、VHDL运算符

VHDL对象:常量

对象: 程序中可被赋值的载体(信号,变量,常量) 常量:定义在设计描述中不变化的值 格式:CONSTANT 常数名:数据类型 := 表达式;

VHDL对象:变量与信号的比较

4.对应硬件结构不同。 信号对应实际电路的某个节点或信号线;变量是 一个抽象值,它不与任何实际电路连线对应。

注意:变量不与任何实际电路连线对应,不代表变量赋 值行为不产生与之对应的硬件结构。变量赋值语句既然 是可综合的,就一定会对硬件结构产生影响。

5.应用场合不同。 在实际应用中,信号的行为更接近硬件的实际情 况,因此更多地使用信号进行电路内部数据传 递,只在描述一些用信号很难描述的算法时才用 到变量。

此处换成sum<=sum+i可以吗?

FOR i IN 1 To 9 LOOP

格式: SIGNAL 信号名:数据类型 := 初始值;

例:signal y: integer range 0 to 15;

VHDL对象:信号

例1:

architecture behav of example is constant xdata: integer :=2; signal y: integer range 0 to 15;

begin process (s) variable tmp: integer := 0; begin if s =’0’ then tmp := 3; else tmp := 7; end if; y <= tmp + xdata; end process; q<=y ;

end behav;

VHDL对象:信号

VHDL对象:变量与信号的比较

• 变量典型应用场合举例

在LOOP语句中,若在一个循环体内需要对某一个数据进行多次操作, 则必须使用变量,因为对信号的多次赋值只有最后一次会生效。

Variable Sum:Integer RANGE 0 TO 127;

.

.

.

FOR i IN 1 To 9 LOOP

Sum:= Sum+i; END LOOP;

end if; q <= temp;

end process; end behav;

-- 请写出对应的实体说明

VHDL对象:信号

信号: 在ENTITY, ARCHITECTURE和 PACKAGE中用于定义内部连线,在元件间起互 连联作用;或作为一种数据容器,以保留历史值 或当前值。用来描述实体内部节点。

VHDL对象:常量

例: architecture behav of example is begin process (rst, clk, en) constant zero : std_logic_vector (7 dwonto 0) := “00000000”; begin

if clk’event and clk=‘1’ then if (rst = ‘1’) then q <= zero; elsif (en = ‘1’) then q <= data; else q <= q; end if;

end behav;

VHDL对象:信号与端口比较

VHDL对象:信号与端口比较

1.信号和端口都描述了电路中实际存在的节点。信 号描述的是实体内部的节点,而端口描述实体与 外界的接口。

2.信号理解为“实体内部不限定数据流动方向的端 口”。

3.端口理解为“限定数据流动方向的信号”。

4.信号赋值具有延时。

VHDL对象:变量与信号的比较

1.声明形式与赋值符号不同。

2.有效域不同。 信号在结构体内、进程外定义,变量在进程内定 义。信号有效域为整个结构体,可在不同进程中 传递数值;变量的有效域是定义该变量的进程。

3.赋值操作的执行不同。 变量赋值是立即生效,在执行下一条语句是,该 变量的值为上一句新赋的值;信号赋值具有延时 性,信号的赋值语句即使被执行也不会使信号立 即发生代入,下一条语句执行时,仍使用原来的 信号值(信号是在进程挂起时发生代入)。