SPI基础SPI总线技术基本原理.pptx

SPI协议介绍ppt课件

4

内部结构图

SPI总线

5

传输模式

根据时钟极性(CPOL)及相位(CPHA)不同可 以组合成4种工作模式:SPI0,SPI1,SP2, SP3.

(1)SPI0:CPOL=0,CPHA=0 (2)SPI1:CPOL=0,CPHA=1 (3)SPI2:CPOL=1,CPHA=0 (4)SPI3:CPOL=1,CPHA=1

6

传输模式

• 时钟极性(CPOL)定义了时钟空闲状态电平, 对传输协议没有重大影响。

• CPOL=0:时钟空闲状态为低电平。 • CPOL=1:时钟空闲状态为高电平。

7

传输模式

• 时钟相位(CPHA)定义数据的采样时间。 • CPHA=0:在时钟的第一个跳变沿(上升沿或

下降沿)进行数据采样。 • CPHA=1:在时钟的第二个跳变沿(上升沿或

SPI协议应用

1

主要内容

• SPI总线介绍 • 传输模式 • 时序分析 • SPI特点总结

2

Sபைடு நூலகம்I总线介绍

• SPI接口是Motorola首先提出的全双工三线 同步串行外围接口,采用主从模式架构, 支持多从设备应用,一般只支持单主设备。

• 时钟由主设备控制,数据在时钟脉冲下按 位传输,高位在前。

下降沿)进行数据采样。

8

传输模式

9

传输模式

10

传输模式

11

传输模式对比

12

时序分析

13

特点

• 优点: (1)接口简单,利于硬件设计与实现。 (2)时钟速度快,且没有系统开销。 (3)相对抗干扰能力强,传输稳定。

14

特点

缺点: (1)缺乏流控制机制,无论主器件还是从器

SPI总线组成及其工作原理

SPI总线组成及其工作原理SPI(Serial Peripheral Interface)是一种同步串行通信总线,常用于连接微控制器与外部设备,如传感器、存储器、外设等。

SPI总线由四条信号线组成,包括SCLK(串行时钟线),MOSI(主设备输出从设备输入线),MISO(主设备输入从设备输出线)和SS(片选信号线)。

以下将详细介绍SPI总线的工作原理和其组成部分。

SPI总线采用主从架构,由一个主设备(如微控制器)和一个或多个从设备(如传感器、存储器等)组成。

主设备通过SCLK产生时钟信号来驱动整个通信过程。

主设备通过MOSI线发送数据到从设备,从设备通过MISO线传输数据给主设备。

每个从设备都有一个片选信号线(SS),用于使能该从设备。

当主设备需要与一些从设备通信时,将对应的片选信号线拉低,使该从设备处于选中状态。

1.SCLK(串行时钟线):SCLK是SPI通信中的时钟信号,由主设备通过该线产生并驱动。

SCLK信号的频率可以由主设备控制,通常可以在MHz级别。

SCLK的上升沿和下降沿都用于同步数据传输。

数据在SCLK的上升沿或下降沿的边沿进行读写操作。

2.MOSI(主设备输出从设备输入线):MOSI是主设备输出从设备输入的数据线。

主设备通过MOSI将数据传输给从设备。

数据在每个SCLK周期的上升沿或下降沿被写入。

3.MISO(主设备输入从设备输出线):MISO是主设备输入从设备输出的数据线。

从设备通过MISO将数据传输给主设备。

数据在每个SCLK周期的上升沿或下降沿被读取。

4.SS(片选信号线):每个从设备都有一个对应的SS信号线。

当主设备需要与一些从设备通信时,将该从设备的SS信号线拉低,使该从设备处于选中状态。

当通信结束后,SS信号线会被拉高,表示该从设备不再被选中。

1.主设备通过控制SS信号线,选中一些从设备开始通信。

2.主设备通过SCLK产生时钟信号,并通过MOSI线发送数据给从设备。

3.从设备在SCLK的上升沿或下降沿将数据写入MISO线,传输给主设备。

SPI总线

SPI总线

综述:SPI(Serial Peripheral interface):高速同步串行口。

是一种标准的四线同步

双向串行总线。

Motorola首先在其MC68HCXX系列处理器上定义的在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间。

SPI 接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

速率:目前应用中的数据速率可达几Mbps。

通信原理:SPI接口共有4根线:设备选择线SS、时钟线SCLK、串行输出

数据线MISO、传行输入数据线MOSI。

SPI由主机的片选信号SS以低电平选中从机,通过主机控制时钟SCLK同步传输数据。

扩展时只要增加主机的片选信号线如图2所示。

图2

下图为SPI结构图,通过移位寄存器左移输出数据,右移输入数据。

SPI的时序模式:由时钟极性选择位CPOL和时钟相位选择位控制CPHA。

CPOL用于选择空闲状态电平,CPHA选择数据接收端的采样时刻。

具体时序如图3。

图3

SPI接口必须根据具体情况设置匹配的传续时序模式,时序只有匹配,数据传输才能正常进行,如果设置的不匹配,可能导致数据接收方和发送方在同一时钟沿作用,导致数据传输失败。

I2CVSSPI。

SPI总线介绍PPT课件

写保护寄存器

命令字

D7 D6 D5 D4 D3 D2 D1 D0

8EH或8FH

WP 0 0 0 ,0 0 0 0

17

第17页/共30页

RAM单元 0单元 1单元 2单元

3 4 ........ 31单元

命令字 C0H或C1H C2H或C3H C4H或C5H C6H或C7H. C8H或C9H. .............. FCH或FDH

寻址: MOSI:When master, out line; when slave, in line MISO:When master, in line; when slave, out line

3

第3页/共30页

SPI从机的内部结构

SPI接口实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产 生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。 上升沿发送,下降沿接收。(有的器件是上升沿接收,下降沿发送)

•

MOV A,#00H

•

MOV @R0,A

•

SETB SCLK

•

NOP

• LOOP2: CLR SCLK;下降沿输出

•

MOV A,@R0

•

MOV C,I/O

•

RRC A

•

MOV @R0,A

•

SETB SCLK

•

DJNE R1,LOOP2

•

24

RET

第24页/共30页

多字节读模式

将时钟日历寄存器的秒、分、时、日、星期、月、年以及写保护寄存器的内容分别存入单片机的6FH~ 68H单元

1

第1页/共30页

SPI从机的内部结构 • SPI从机从主机获得时钟和片选信号,因此cs和sclk都

spi总线工作原理

spi总线工作原理

SPI(Serial Peripheral Interface)总线是一种同步串行通信协议,它主要用于在微控制器或其他数字集成电路之间传输数据。

SPI总线由一个主设备(Master)和一个或多个从设备(Slave)组成。

主设备通过与从设备之间发送和接收数据的方式来与其进行通信。

SPI总线的工作原理如下:

1. 首先,主设备选择要与之通信的从设备。

这是通过在片选引脚上拉低电平来实现的。

其他从设备的片选引脚应保持高电平。

2. 接着,主设备通过时钟引脚(SCK)生成时钟信号,此时数据传输开始。

3. 主设备通过主输出(MOSI)引脚发送数据,从设备通过主输

入(MISO)引脚接收数据。

在每个时钟周期中,主设备和从设

备在SCK上的上升沿或下降沿进行数据交换。

4. 数据传输时,主设备先发送一个起始位(通常是高电平)并将其传输到从设备。

5. 接下来,主设备和从设备同时发送并接收数据,每一个时钟周期传输一个位。

数据传输的顺序是从最高位(MSB)到最

低位(LSB)。

6. 当所有数据位都传输完毕后,主设备通过拉高片选引脚结束

与从设备的通信。

7. 在通信结束后,主设备可以选择与其他从设备进行通信,或者在下一个时钟周期中重新选择与之前的从设备进行通信。

SPI总线的工作原理简单而直观。

它具有高速、可简化电路设计等优点,因此在很多嵌入式系统中得到了广泛应用。

SPI总线的工作方式及原理详解

SPI总线的工作方式及原理详解SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

SPI总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于CPU与各种外围器件进行全双工、同步串行通讯。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

SPI总线有四种工作方式(SP0,SP1,SP2,SP3),其中使用的最为广泛的是SPI0和SPI3方式。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设音时钟相位和极性应该一致。

SPI时序详解---SPI接口在模式0下输出第一位数据的时刻SPI接口有四种不同的数据传输时序,取决于CPOL和CPHL这两位的组合。

图1中表现了这四种时序,时序与CPOL、CPHL的关系也可以从图中看出。

图1CPOL是用来决定SCK时钟信号空闲时的电平,CPOL=0,空闲电平为低电平,CPOL=1时,空闲电平为高电平。

SPI通信协议(SPI总线)学习

SPI通信协议(SPI总线)学习

SPI(Serial Peripheral Interface)是一种同步的、全双工的通信总线,常用于连接微

控制器和外围设备。

SPI总线的通信协议相对简单,有四根信号线组成:SCLK(时钟

信号)、MOSI(主机输出从机输入信号)、MISO(主机输入从机输出信号)和SS (片选信号)。

SPI总线的工作方式如下:

1. 选择从机:主机通过将片选信号(SS)置低来选择要通信的从机。

通常每个从机都

有独立的片选线。

2. 时钟信号:主机通过时钟信号(SCLK)提供同步时钟给从机,控制数据传输的时钟周期。

3. 主机输出从机输入:主机将要发送给从机的数据通过主机输出从机输入信号(MOSI)发送给从机。

数据按照时钟的上升沿或下降沿传输。

4. 主机输入从机输出:从机将要发送给主机的数据通过主机输入从机输出信号(MISO)传输给主机。

数据按照时钟的上升沿或下降沿传输。

5. 数据传输顺序:数据传输是基于时钟信号的,每个时钟周期传输一个位。

主机和从

机按照特定的数据传输格式进行通信,可以是先传输最高有效位(MSB)或最低有效

位(LSB)。

6. 数据传输模式:SPI总线支持多种数据传输模式,如模式0、模式1、模式2和模式3,不同模式下时钟信号和数据传输的相位和极性不同。

7. 传输完成:主机通过将片选信号(SS)置高来结束通信。

SPI总线的优点是简单、高速、低成本,适用于连接多种外设,如传感器、存储器、显示器等。

然而,SPI总线并没有提供错误检测和纠正机制,需要通过其他方式保证数据的可靠性。

SPI原理与应用.ppt

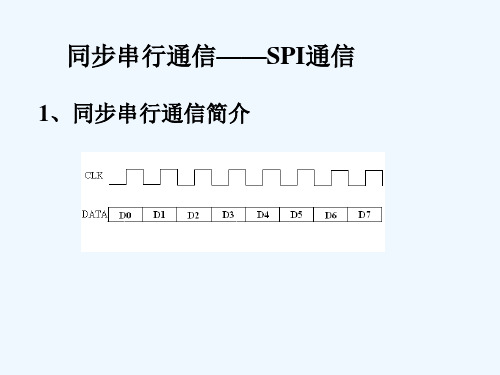

同步串行通信——SPI通信

1、同步串行通信简介

2、 硬件SPI接口与I/O模拟SPI比较

速度:硬件接口快很多 编程:硬件接口是设置和查询寄存器,模 拟是一位一位送 实时性:硬件接口可以设置中断,模拟只能查 询

3、 硬件连接

应用——与DA芯片AD5300接口

根据这个时序图,我们就可以得到,SPCR中CPOL为0,CPHA为1

delay(10); SPSR=0; SPDR=temp1; do { status=SPSR; }while(!(status&=0X80)); SPSR=0; delay(10); PORTA|=BIT(PA1);

do

{ status=SPSR; }while(!(status&=0X80));

D/A转换器的基本原理及分类 T型电阻网络D/A转换器 :

I VREF

I7

I7 R I6 2R 1 0

I6 R I5 2R 1 0

I5 R I4 2R 1 0

I4 R I3 2R 1 0

I3 R I2 2R 1 0

I2 R I1 2R 1 0

I1 R I0 2R 1 0

I0

2R 1 Rfb IO1 IO2

2R

0

+

VO

D7

D6

D5

D4

D3

D2

D1

D0

输出电压 的大小与数字量是指输入数字量的最低有效位(LSB)发生变化时,所对应 的输出模拟量(电压或电流)的变化量。它反映了输出模拟量的最 小变化值。 分辨率与输入数字量的位数有确定的关系,可以表示成FS / 2 n 。 FS表示满量程输入值,n为二进制位数。对于5V的满量程,采用8 位的DAC时,分辨率为5V/256=19.5mV;当采用12位的DAC时,分辨 率则为5V/4096=1.22mV。显然,位数越多分辨率就越高。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

THANKS !

SPI总线介绍

• SPI总线最初有Motorola公司提出,出现在其 68K系列单片机中,由于其简单实用,又不涉及 专利问题,因而很多厂家的IC都支持该接口;

• 目前SPI接口的外设种类很多,如EEPROM、 ADC、DCA、实时时钟、液晶模块、SD卡、无 线通信模块等等;

SPI总线的组成

• SPI是一种全双工3线同步串行通信接口,采用主从通 信模式,支持多slave架构;

• CPOL=0:空闲状态SCLK为低电平; • CPOL=1:空闲状态SCLK为高电平

• 时钟相位选择位:CPHA

• CPHA=0:第一个时钟边沿进行数据采样 • CPHA=1:第二个时钟边沿进行数据采样

SPI总线的多机通信

SPI通信的特点

• SPI为环形通信方式,接收、发送同时进行, 接收、发送使用同一个函数;只是函数调用 者关注的焦点不同;

• 同步时钟由主机产生,在时钟移位脉冲下,数据按 位传输MOSI、MISO、 SCLK、/SS;

SPI信号线介绍

• 从设备选择线/SS:有Master设备控制,用于选择(激活)某个SPI从设备,低 电平有效;只有当/SS为低时,相应的SPI设备才处于工作状态;

的MOSI相连,双方的MISO也应该接在一起,这一点和UART不同;

SPI信号线介绍

• 当然有些厂家(例如MicroChip公司)是按照SDI和SDO的方式命名 的,是站在器件的角度命名,这种情况下一方的SDI要接另一方 的SDO,反之亦然;

SPI通信时序模式

• SPI总线共有四种时序模式: • 极性选择位:CPOL

• 同步时钟信号SCLK:用于同步主从设备的数据传输,由Master设备控制, 主/从设备按照SCLK的步调发送或者接收数据;

SPI信号线介绍

• SPI的串行数据线有两条,分别承担Master到Slave和Slave到Master的数据传输; • MOSI:Master out,Slave in • MISO:Master in, Slave out • 比如MOSI,数据从Master到slave,因而在电路板上主芯片的MOSI和从芯片

总线技术

团队:唐建东 孙光 曾启明 张秀君

电子信息专 业课程

项目化实施 课程

SPI总线技术基本原理

特点 应用 信号

SPI的特点

• SPI应用特点:SPI相对于I2C速度要快很多:I2C两种标准: 100K和400K时钟,而SPI口则可以高达数10M的通信速率

• I2C的常用场合:EEPROM、温度传感器、GPIO扩展;SPI: LCD模块、无线通信模块、SD卡等等,还有外扩的Flash芯片等 等。