基于FPGA的线阵CCD驱动时序电路设计

基于FPGA的线阵CCD的驱动程序的设计

南京理工大学毕业设计说明书(论文)作者: XX 学号: 080403227系:电子工程与光电技术系专业: 电子科学与技术题目: 基于FPGA的线阵CCD驱动教授指导者:(姓名) (专业技术职务)评阅者:(姓名) (专业技术职务)2012 年 5 月南京理工大学紫金学院毕业设计(论文)评语学生姓名:班级、学号:080403227题目:基于F P G A的线阵C C D驱动综合成绩:毕业设计(论文)评语毕业设计说明书(论文)中文摘要毕业设计说明书(论文)外文摘要目次1 引言 (1)1.1国内外研究现状及发展趋势 (1)1.2课题研究的背景和意义 (2)1.3本设计的研究及设计内容 (3)2 CCD (4)2.1CCD简介 (4)2.2CCD基本特点 (5)2.3CCD工作原理 (7)2.4TCD1703C的主要特性 (12)3 FPGA/CPLD (20)3.1FPGA简介 (20)3.2FPGA和CPLD的区别 (21)3.3FPGA和CPLD的特点 (22)4 基于FPGA的线阵CCD的驱动 (23)4.1线阵CCD的结构和工作原理 (23)4.2基于FPGA芯片的时序电路的设计与实现 (24)4.3CCD驱动时序的V ERILOG HDL描述与实现 (25)5 基于QuartusII的仿真 (32)6 实际硬件调试 (35)结论 (41)致谢 (42)参考文献 (43)附录A 程序代码 (44)1 引言电荷耦合器件(Charge Coupled Devices, CCD)是20世纪70年代初发展起来的新型半导体集成光电器件。

近30年以来,CCD器件在图像传感和非接触测量领域的发展迅速。

CCD可把外界待测物体的图像信号转换成电信号,即把入射到CCD光敏面上的按空间位置分布的光强信息,转换为按时间顺序串行输出的视频信号,视频信号可通过软件处理再现原物体的图像。

由于CCD具有自扫描、高分辨、高灵敏、重量轻、体积小、像素位置准确、耗电少、寿命长、可靠性好、信号处理方便、易于与计算机接口等优点,致使CCD光电尺寸测量的使用范围比现有的机械式,光学式,电磁式测量仪优越的多。

FPGA控制下面阵CCD时序发生器设计及硬件实现

FPGA控制下面阵CCD时序发生器设计及硬件实现CCD是利用光电转换原理把图像信号转换为电信号,即把一幅按空间域分布的光学图像,转换成为一串按时间域分布的视频信号的半导体元器件。

因其具有体积小、重量轻、功耗低、灵敏度高、工作稳定、寿命长、自扫描和便于同计算机接口等优点,被广泛应用于图像传感和非接触式测量。

CCD应用的关键问题之一,是驱动时序发生器设计。

它直接关系到CCD的信号处理能力、转换效率和信噪比等光电转换特征。

针对Sony公司面阵CCD ICX098BQ的工作原理和驱动时序的要求,给出了驱动时序发生器的具体设计,使用VHDL语言对驱动时序发生器的实现方案进行了硬件描述,采用Quartus II 8.0对所设计的时序发生器进行了功能仿真,在该驱动时序发生器作用下,对Sony公司ICX98BQ 面阵CCD产生的输出信号波形进行了验证。

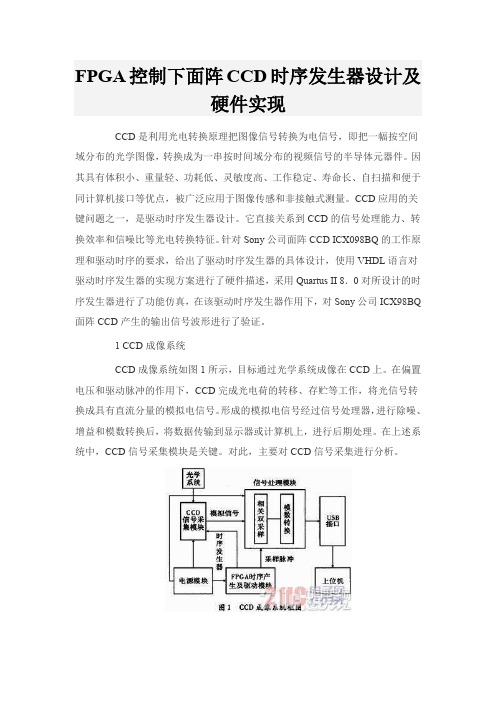

1 CCD成像系统CCD成像系统如图1所示,目标通过光学系统成像在CCD上。

在偏置电压和驱动脉冲的作用下,CCD完成光电荷的转移、存贮等工作,将光信号转换成具有直流分量的模拟电信号。

形成的模拟电信号经过信号处理器,进行除噪、增益和模数转换后,将数据传输到显示器或计算机上,进行后期处理。

在上述系统中,CCD信号采集模块是关键。

对此,主要对CCD信号采集进行分析。

2 面阵CCD图像传感器驱动时序分析2.1 Sony ICX098BQ型面阵CCDICX098BQ是Sony公司生产的一款1/4英寸(0.635 cm),具有可变电子快门的行间转移型彩色面阵CCD芯片,芯片结构如图2所示。

该芯片灵敏度高,暗电流小,具有较好的抗弥散功能。

ICX098BQ芯片由感光阵列、垂直移位寄存器、水平移位寄存器和输出放大器4个主要部分组成。

要使该CCD芯片正常工作,需要8路驱动时钟来驱动。

分别为4路垂直转移时钟Vφ1、Vφ2A、Vφ2B、Vφ3,控制垂直移位寄存器中的电荷信号向水平移位寄存器移动,其中当Vφ2A和Vφ2B为+15 V高电平时作为读出转移时钟,将感光阵列的信号电荷转移到垂直移位寄存器中;两路水平转移时钟Hφ1、Hφ2,控制水平移位寄存器中的电荷信号向前迁移;复位门时钟RG,使水平移位寄存器中的电荷信号顺利输出,其频率为10 MHz,直接决定CCD电荷信号的水平输出频率并控制曝光量的电子快门时钟φSUB。

(整理)基于FPGA的面阵CCD驱动电路的设计.

基于FPGA的面阵CCD驱动电路的设计作者:时间:2010-05-05 来源:电子产品世界0 引言CCD(Charge Coupled Devices)电荷耦合器件是20世纪70年代初发展起来的新型半导体集成光电器件。

近30年来,CCD器件及其应用技术的研究取得飞速进展,特别是在图像传感和非接触测量领域的发展尤为迅速,它具有噪声低、光谱响应宽、精度和灵敏度高、可靠性好等优点。

CCD 成像系统主要由光学系统、驱动电路、信号处理电路和图像处理电路组成。

本文主要介绍CCD传感器驱动电路的设计,包括驱动时序产生电路、电源变换电路和驱动器电路。

其中,驱动时序产生电路向CCD传感器提供正常工作所需要的各种时序脉冲;电源变换电路向CCD提供正常工作时所需的各种直流偏置电压;驱动器电路用来提高驱动时序的驱动能力。

l CCD驱动时序电路的要求及实现1.1 CCD图像传感器TH7888ACCD图像传感器采用ATMEL公司的TH7888A。

它是一种高性能的帧转移面阵CCD器件,提供单路和双路两种输出方式,输出数据速率可达40 MHz,每秒30帧图像。

TH7888A具有较低的暗电流及像元读出噪声,可用电子快门来调节曝光时间,性能优异。

TH7888A由感光区,存储区和水平移位寄存器构成,有效像元数为1 024×1 024个。

CCD的一个工作周期可分为两个阶段:光积分阶段和电荷转移阶段。

光积分阶段进行感光阵列的电荷积累,存储区到转移寄存器的电荷转移(行逆程)以及转移寄存器向输出放大器的电荷输出(行正程);转移阶段主要进行帧转移,即将感光区的光积分电荷转移至存储区。

要完成如上功能就要给CCD提供严格的驱动时序时钟。

TH7888A的各驱动时序关系如图1所示。

图1中,φPA为帧时钟,高电平时为光积分阶段,低电平时为电荷转移阶段。

φP1~φP4为帧转移脉冲,在光积分阶段时不变,在电荷转移阶段时同行转移控制信号φM1~φM4一起完成整帧的转移。

基于FPGA的线阵型CCD驱动电路设计

基于FPGA的线阵型CCD驱动电路设计∗程瑶;周娜;王荣秀【摘要】CCD驱动电路的设计是实现CCD各种设计功能的关键性因素,只有对其驱动信号设计的严格把关,才会进一步保证CCD器件后续工作的开展。

分析线阵CCD器件TCD1703C的驱动时序要求,采用QuartusⅡ软件,选用Verilog HDL语言设计了各路驱动时序信号。

将程序设计下载到FPGA器件中,通过逻辑分析仪对输出信号进行了波形监测,验证了线阵CCD的驱动时序设计的可行性。

将产生的驱动时序信号接入CCD器件,不同光照入射的条件下,CCD在驱动信号的驱动下,正常工作并输出了相应的视频信号。

%The design of driving circuits is a crucial factor to realize the various design features.Only with the strict driving signals desiging,the CCD devices can perform the further work. TheTCD1703C driver timing requirements for linear array CCD device were analyzed. And the driving signals were designed by usingQuartusⅡsoftware and Verilog HDL. The program was downloaded to the FPGA device,and the output signals’ waveforms were monitored by the logic analyzer. So the feasibility of the time sequence design of linear array CCD was verified. Finally, connecting the driving signals to the CCD device,the CCD was driven by the driving signals,and the corresponding video signal was output under the different illumination conditions.【期刊名称】《电子器件》【年(卷),期】2017(040)001【总页数】5页(P82-86)【关键词】CCD;驱动电路;FPGA;QuartusⅡ;Verilog HDL【作者】程瑶;周娜;王荣秀【作者单位】重庆理工大学机械工程学院,重庆400050;重庆理工大学机械工程学院,重庆400050;重庆工商大学,重庆400067【正文语种】中文【中图分类】TN386.5CCD图像传感器是利用光电转换原理将图像信号转变为电信号,在各领域都得到了广泛的应用,备受人们的广泛关注[1]。

线阵CCD驱动时序及信号采集系统的设计

线阵CCD驱动时序及信号采集系统的设计

章琦;陈惠明;毛玉兵;白岚

【期刊名称】《仪表技术与传感器》

【年(卷),期】2010(000)002

【摘要】文中设计介绍了一种基于FPGA和ARM的线阵CCD传感器驱动时序和信号采集的实现方法.该系统通过分析TCD1707D线阵CCD的驱动时序,采用Verilog HDL硬件描述语言设计出驱动脉冲电路.CCD正常工作后,产生的模拟信号经过预处理和高速A/D转换送入FPGA的基本宏功能模块FIFO(先进先出数据缓存器),通过异步缓存实现ARM处理器对采集信号的主控及后续应用.线阵CCD驱动时序及信号采集系统,是基于CCD传感器图像处理系统的重要组成部分,经过上位测试平台验证,能够提供准确的数字图像信号.

【总页数】3页(P75-77)

【作者】章琦;陈惠明;毛玉兵;白岚

【作者单位】南京林业大学机械电子工程学院,江苏南京210037;南京林业大学机械电子工程学院,江苏南京210037;南京林业大学机械电子工程学院,江苏南京210037;南京林业大学森林资源与环境学院,江苏南京210037

【正文语种】中文

【中图分类】TP212.1

【相关文献】

1.基于网络的线阵CCD信号采集系统的设计 [J], 何云龙;彭章君;李众立

2.线阵CCD的高速信号采集与USB数据传输系统设计 [J], 陈骥;郭超

3.基于CPLD的线阵CCD信号采集系统设计 [J], 董勇;瑚琦;高鹏飞

4.用基于DSP的线阵CCD实现二维图像信号采集的系统设计 [J], 田岩涛;常丹华;潘普丰;张彦

5.基于ARM7的线阵CCD信号采集系统设计 [J], 陈力;邹洁;刘永智;龙再川

因版权原因,仅展示原文概要,查看原文内容请购买。

基于Verilog的线阵CCD驱动时序设计

荷全部转移输出。信号的输出 部分包括检测 二极 管、复位场效应管和输出放大器等电路, 为了使信号

脉宽都为 175ns, 这里 实际上用到了状态机的设计 思想, RS_ CP _40M _co unt er 相当于一个 状态寄存

741

光学 技 术

第 36 卷

器。由于对 CCD 芯片设计有严格的时序要求, 所以 在 FP GA 设计时要考虑时钟网络的选取问题, 这里 统一选取 BA NK3 区域的 通用 IO 管脚, 选取 110 脚、108 脚、112 脚、107 脚和 106 脚, 这样对 时钟的 一致性比较有利。

*

74 0

收稿日期: 2010 01 31; 收到修改稿日期: 2010 04 26

E mai l: s kyeyb ook @ 163. com

作者简介: 付天舒( 1977 ) , 男, 讲师, 硕士研究生, 从事非线性信号分析研究。

第5期

司的 Cyclone 系列的 EP2C8Q208C8N 芯片, 其逻 辑单元( L E ) 8256 个, 这款芯片的内部资源比较丰 富, 方便以后设计产品时系统的扩展[ 4, 5] , 本设计的 主要目的是让设计方案有好的移植性, 所以在芯片 选型时, 只要基本逻辑单元数量能满足需要就可以,

第 36 卷 第5 期 2010年9月

光 学技 术

OP T ICA L T ECH N IQU E

Vo l. 36 No . 5 Sep. 2010

文章编号: 1002 1582( 2010) 05 0740 04

基于 Verilog 的线阵 CCD 驱动时序设计 *

付天舒1, 2 , 赵春晖1

( 1. 哈尔滨工程大学 信息与通信工程学院, 哈尔滨 150001) ( 2. 东北石油大学 电子科学 学院, 黑龙江 大庆 163318)

基于FPGA的全帧型面阵CCD驱动时序设计

第32卷增刊2006年8月光学技术O尸下7(1A L T E C H N I Q U EV01.32Sup pl.A u gust2006文章编号:1002—1582(2006)S-0313—04基于FPG A的全帧型面阵C C D驱动时序设计‘常磊,李国宁,金龙旭(中国科学院长春光学精密机械与物玛研究所,吉林长春130033)摘要:在介绍全帧型面阵CC D的结构和特点的基础上,分析了陔类型C C D的驱动信号和时序,并针对C CD442A 型CC D设计出了一种基于现场可编程门阵列(FPG A)的全帧型面阵C C D驱动时序。

采用集成开发环境和自上而下的模块化设计方法,实现了硬件没计的软件化,提高了开发效率。

关键词:全帧;面阵C C D;驱动时序;F PG A;仿真中图分类号:TN386.5文献标识码:AD e si gn on dr i vi ng ge ner at or ba se d on FPG A t e chnol ogyf O r C C D f ui I f r am e ar ea i m age s ens orC H A N G Lei,L l G uo.ni ng,d i n Long—X U(C h angch un I ns t i t ut e of O p t i c s,F i n e M ec ha ni cs a nd P h ysi cs,C hi nes e A cade m y of Sci ence s,C hangc hun130033,C hi na)A bs t r a ct:The s t r uct ur e a nd t he s peci f i cat i on of C C D ful l f r am e a l-o_.a i m age s ens or ar e i n t r odu ced,and t he dr i vi n g s i gnal s and.schedul es of t his O T D ar e st ud i ed.A dr i vi ng ge ner a t or bas ed o n FPG A t e chnol ogy f or C C q3442i s be e n s ucces sf ul l y de.s i gn e d.T he ci rcui t des i gned by t he so f t w ar e i s r eal ized ba sed o n t he i nt egr at ed devel op m ent e n vi r on m e n t a nd t he m odul ar i zat i on des i gn m et h od f r om t op t o bot t om.T he devel op m ent ef f i ciency i s enhanced.K e y w or ds:f u l l f r am e;ar odt i naage C C D;dr i vi ng s che dul e;F PG A;s i m ul at i on1引言C C D(char ge coupl ed devi c es)电荷耦合器件是20世纪70年代初发展起来的新型半导体集成光电器件…。

基于FPGA的帧转移面阵CCD驱动电路设计

基于FPGA的帧转移面阵CCD驱动电路设计程鹏飞,顾明剑,王模昌(中科院上海技术物理研究所,上海 200083)摘要:针对e2v公司的CCD67 Back Illuminated NIMO型CCD,对其驱动能力进行详细的分析;选用LM117T和LM317T设计CCD所需的偏置电压;DS0026来完成设计CCD驱动器;Altera公司的可编程逻辑器件EPF10K30RI240-4来设计CCD的驱动时序。

实验结果表明,设计的CCD驱动电路可以满足CCD 的各项驱动要求。

关键词:驱动电路;偏置电压;CCD驱动器;现场可编程门阵列(FPGA)中图分类号:文献标识码:A 文章编号:1001-8891(2006)09-0519-04A Design of Array CCD of Frame Transfer Driving Circuit Based on FPGA TechniqueCHENG Peng-fei,GU Ming-jian,WANG Mo-chang(Shanghai Institute of Thechnical Physics, Chinese Academy of Sciences, Shanghai 200083,China)Abstract:According to CCD67 Back Illuminated NIMO produced by e2v company, the driving capability of CCD was detailed analyzed. Bias voltages of CCD are designed by LM117T and LM317T; CCD drivers are designed with DS0026; the programmable logical device of the EPF10K30RI240-4 of Company Altera isused for the design of CCD driving time order . Experiments show that the design of CCD driving circuit can meet every demand of CCD.KeyWords:driving circuit;bias voltage;CCD driver;FPGA引言近几十年来, 随着航天技术的发展,CCD相机在高精度测量、空间遥感和对地观测等领域,得到了广泛的应用。

基于FPGA的线阵CCD驱动器设计

本科毕业设计论文题目基于FPGA的线阵CCD驱动器设计专业名称学生姓名指导教师毕业时间摘要该篇毕业设计涉及的器件主要有TDICCD8091及FPGA EP1C12Q240,开发平台为Quartes II。

介绍一种基于FPGA设计线阵CCD器件和TDICCD8091芯片复杂驱动电路和整个CCD的电子系统控制逻辑时序的方法,并给出时序仿真波形。

CCD,是英文(Charge Coupled Device) 即电荷耦合器件的缩写,它是一种特殊半导体器件,是一种新型的固体成像器件。

它既具有光电转换的功能,又具有信号电荷的存储、转移和读出的功能。

CCD应用技术是光、机、电和计算机相结合的高新技术。

在FPGA开发环境下,系统地介绍了TDICCD的基本工作原理、特性及应用。

并以TDI8091芯片的CCD驱动时序的设计介绍了在Quartes II开发环境下,利用VHDL硬件描述语言输入方式来设计数字逻辑电路的过程和方法。

总之,CCD应用技术有很好的发展前景。

关键字:CCD,TDICCD8091芯片,FPGA,VHDLABSTRACTThe article involved in the graduation line array device including CCD,TDICCD8091chips and VHDL design. Introduction of a design based on FPGA devices andTDICCD8091 linear CCD and theCCD driving circuit complexity of electronic timing system controllogic,and gives the timing simulation wavetorm.CCD (Charge Coupled Device) is a kind of special semiconductor device, which is a new kind of solid like device. After having light electricity conversion, the signal electric charge saved and transfer again with the function that had done. Applied technique in CCD is high and new technique that contain light, machine, give or get an electric shock to combine together with the computer.Environment in the FPGA,the system introduces the basic working principle TDICCD,characteristics and appliaction .AND to TDI8091 chip CCD driving circuit design introduced in Quartes development software ,the use of VHDL hardware description language input to the process of designing digial logic circuits and methods .In conclusion ,CCD technoligy has a very good application prospects.KEY WORDS: ccd,tdiccd8091chip,fpga,vhdl第一章前言1.1TDI-CCD简介TDICCD是一种具有面阵结构线阵输出的新型CCD,较普通的线阵CCD而言.它具有多重级数延时积分的功能。

基于FPGA的CCD驱动设计

基于FPGA的CCD驱动设计电荷耦合器件(CCD)作为新兴的固体成像器件即图像传感器,具有体积小,重量轻,分辨力高,噪声低,自扫描,工作速度快,灵敏度高,可靠性好等优点,受到人们的高度重视,广泛应用于图像传感、景物识别、非接触无损检测、文件扫描等领域。

CCD 驱动电路的实现是CCD 应用技术的关键问题。

以往大多是采用普通数字芯片实现驱动电路,CCD 外围电路复杂,为了克服以上方法的缺点,利用VHDL 硬件描述语言.运用FPGA 技术完成驱动时序电路的实现。

该方法开发周期短,并且驱动信号稳定、可靠。

系统功能模块完成后可以先通过计算机进行仿真,再实际投入使用,降低了使用风险性。

1 硬件设计CCD的硬件驱动电路系统的核心器件是SPARTAN 系列芯片XC3S50;CCD 采用Atmel 公司的CCDTH7888A 图像传感器;CCD 驱动脉冲由XC3S50 提供,脉冲信号产生后由驱动模块对脉冲电压进行变换使其符合TH7888A 的驱动电压要求。

CCD 像素输出电压经过A/D 转换模块处理电路VSP2272 芯片的处理得到数字信号,最后为了方便传输和方便后续模块对数字信号的处理将数字信号由TTL 电平转换成LVDS 电平进行输出,整个系统如图1 所示。

1.1 TH7888A 简介CCD 图像传感器采用THOMSON 公司生产的TH7888A。

它是一种高性能的帧转移面阵CCD 器件,采用四相脉冲驱动工作,并提供电子快门的功能;同时,它具有2 种输出的模式:单路输出和双路输出。

其主要的性能参数如下:光敏区和存储区均为1024×1024像素;速度可以达到30 images/s 以上;像元尺寸为14 mm×14mm;感光区面积为14.34 mm×14.34 mm;光谱波长范围在400~700 nm 之间;像元输出频率为20 MHz。

1.2 XC3SC50 简介XC3S50 属于XILINX 公司SPARTAN3 系列的FPGA(现场可编程逻辑门阵列),是一种高性能器件,其特点是:器件运用90。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的线阵CCD驱动时序电路设计

1 引言

电荷耦合器CCD具有尺寸小、精度高、功耗低、寿命长、测量精度高等优点,在图像传感和非接触测量领域得到了广泛应用。

由于CCD芯片的转换效率、信噪比等光电特性只有在合适的时序驱动下才能达到器件工艺设计所要求的最佳值,以及稳定的输出信号,因此驱动时序的设计是应用的关键问题之一。

通用CCD驱动设计有4种实现方式:EPROM驱动法;IC驱动法;单片机驱动法以及可编程逻辑器件(PLD)驱动法。

基于FPGA设计的驱动电路是可再编程的,与传统的方法相比,其优点是集成度高、速度快、可靠性好。

若要改变驱动电路的时序,增减某些功能,仅需要对器件重新编程即可,在不改变任何硬件的情况下,即可实现驱动电路的更新换代。

2 CD 1501D CCD工作参数及时序分析

2.1 TCDl50lD CCD工作参数。