系统集成电路大作业

2022年集成电路专题讲座课后作业

返回继续教育系统首页我的课程服务指南集成电路专题讲座总分:100及格分数:60考试剩余时间:1时56分37秒单选题(共7题,每题5分)2、现阶段已商业化的SiC产品主要集中在()电压等级,3300V以上电压等级器件尚处于工程样品阶段。

A、650V-4700VC、650V-2700VD、650V-1700VD6、MCU芯片是()。

A、驱动类芯片C、计算类芯片D、电源类芯片B7、砷化镓的器件的缺点是功率较低,低于()。

A、50WC、150WD、200WA判断题(共7题,每题5分)1、1963年,日本电气股份有限公司(NEC)获得了仙童半导体公司的技术授权。

正确2、FPGA设计完成后,无法改动硬件资源,灵活性受限。

错误3、传统存储器通过结构优化、材料升级等也可形成新型存储器。

正确4、目前最先进的SOC设计还远远未达到制造工艺和材料物理属性的极限限制。

错误5、1989-1992年,日本超越美国,成为全球最大的半导体生产国。

正确6、未来5年将是第三代半导体产业发展的关键期,全球资本加速进入第三代半导体材料、器件领域,产能大幅度提升,企业并购频发,正处于产业爆发前的“抢跑”阶段。

正确7、异构集成是指将单独制造的组件集成到更高级别组装,总体上提供更强的功耗和改进的操作特征。

交卷返回继续教育系统首页我的课程服务指南集成电路专题讲座总分:100及格分数:60考试结果相关信息:未合格,您的总分为:30单选题(共7题,每题5分)3、连接芯片设计工作和IT基础架构的重要环节是?()答案:C、EDA技术支持正确答案:B、CAD服务4、SRAM的响应通常可以做到()级别。

答案:D、毫秒正确答案:B、纳秒5、()是数字经济最有价值的资源,作为数字经济全新的、关键的生产要素,贯穿于数字经济发展的全部流程,将引发生产要素多领域、多维度、系统性的突破。

答案:A、算力正确答案:B、数据1、()是全球MEMS行业最大的一个应用领域。

答案:A、工业正确答案:D、消费电子多选题(共6题,每题5分)1、碳化硅下游主要应用场景有()。

专用集成电路设计大作业

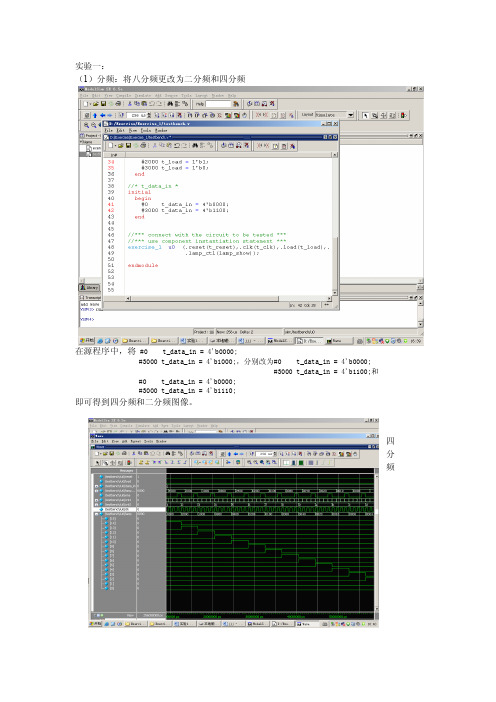

实验一:(1)分频:将八分频更改为二分频和四分频在源程序中,将#0t_data_in=4'b0000;#3000t_data_in=4'b1000;,分别改为#0t_data_in=4'b0000;#3000t_data_in=4'b1100;和#0t_data_in=4'b0000;#3000t_data_in=4'b1110;即可得到四分频和二分频图像。

四分频二分频(2)反序:改变电路使彩灯变成逆时针旋转方式:源程序改动将源程序4'b0000:lamp=16'b0000_0000_0000_0001;4'b0001:lamp=16'b0000_0000_0000_0010;4'b0010:lamp=16'b0000_0000_0000_0100;4'b0011:lamp=16'b0000_0000_0000_1000;4'b0100:lamp=16'b0000_0000_0001_0000;4'b0101:lamp=16'b0000_0000_0010_0000;4'b0110:lamp=16'b0000_0000_0100_0000;4'b0111:lamp=16'b0000_0000_1000_0000;4'b1000:lamp=16'b0000_0001_0000_0000;4'b1001:lamp=16'b0000_0010_0000_0000;4'b1010:lamp=16'b0000_0100_0000_0000;4'b1011:lamp=16'b0000_1000_0000_0000;4'b1100:lamp=16'b0001_0000_0000_0000;4'b1101:lamp=16'b0010_0000_0000_0000;4'b1110:lamp=16'b0100_0000_0000_0000;4'b1111:lamp=16'b1000_0000_0000_0000;default:lamp=16'b0000_0000_0000_0000;首尾相对应语句依次调换位置,即可得到新的源程序,执行后可观测到新的亮灯顺序为反序。

1+X集成电路理论练习题含参考答案

1+X集成电路理论练习题含参考答案一、单选题(共40题,每题1分,共40分)1、在电子产品测试中需保证测试环境稳定,其中使用环境稳定是指()。

A、使用人员操作得当B、硬件的工作参数稳定C、软件的工作参数稳定D、模拟真实用户使用时的场景正确答案:D2、以全自动探针台为例,关于上片的步骤,下列所述正确的是:( )。

A、打开盖子→花篮放置→花篮下降→花篮到位→花篮固定→合上盖子B、打开盖子→花篮放置→花篮到位→花篮下降→花篮固定→合上盖子C、打开盖子→花篮放置→花篮下降→花篮固定→花篮到位→合上盖子D、打开盖子→花篮放置→花篮固定→花篮下降→花篮到位→合上盖子正确答案:D答案解析:以全自动探针台为例,上片的步骤为:打开盖子→花篮放置→花篮固定→花篮下降→花篮到位→合上盖子。

3、转塔式分选机设备进行编带后,进入( )环节。

A、上料B、测试C、外观检查D、真空包装正确答案:C答案解析:转塔式分选机设备芯片检测工艺的操作步骤一般为:上料→测试→编带→外观检查→真空包装。

4、通常情况下,一个内盒中装入的DIP管装芯片( )颗。

A、3000B、1000C、5000D、2000正确答案:D答案解析:一般情况下,一个内盒中装入的DIP管装芯片2000颗。

5、元器件的引线直径与印刷焊盘孔径应有()的合理间隙。

A、0.1~0.4mmB、0.2~0.3mmC、0.1~0.3mmD、0.2~0.4mm正确答案:D6、在电子电路方案设计中最简单的显示平台是()。

A、OLEDB、LCDC、LEDD、数码管正确答案:C7、平移式分选机进行料盘上料时,在上料架旁的红色指示灯亮的含义是( )。

A、上料机构故障B、上料架上有料盘C、上料架上有空料盘D、上料架上没有料盘正确答案:B答案解析:平移式分选机进行料盘上料时,上料架上是否有料盘可以通过上料架旁的传感器进行检测。

当传感器指示灯为红色时,表明上料架上还有料盘,可以继续进行上料,当传感器指示灯为绿色时,表明上料架上无料盘,停止上料。

模拟CMOS集成电路设计大作业

模拟CMOS集成电路设计大作业设计题:假定μn C ox =110 μA/V 2, μp C ox =50 μA/V 2 ,λn =0.04V -1, λp =0.04V -1(有效沟道长度为1μm 时),λn =0.02V -1, λp =0.02V -1(有效沟道长度为2μm 时),λn =0.01V -1, λp =0.01V -1(有效沟道长度为4μm 时),γ=0.2,V THN =| V THP | =0.7V 。

设计如下图的放大器,满足如下要求,其中负载电容C L = 5pF 。

A v > 5000V/V , VDD = 5V , GB ≥ 5MHz ,SR > 10V/µs ,60° 相位裕度, Vout 摆幅在0.5~4.5V 范围, ICMR 为1.5~4.5V , Pdis s ≤ 2mW1.请说明详细的设计过程,包括公式表达式(假定Cox = 0.35fF/µm 2,栅源电容按ox gs C L W C 33367.0=计算);2.给出进行交流仿真和瞬态仿真的spice 仿真的网表,并给出仿真波形和结果以及必要的讨论和说明。

3.如果要求A v至少提高为原来的2倍,其它要求不变,如何修改电路(注意讨论对其它性能参数的影响)?4.如果要求增益带宽积GB提高为原来的2倍,其它要求不变,如何修改电路(注意讨论对其它性能参数的影响)?注意事项:1.计算得到的极点频率为角频率。

2.尺寸最后应选取整数,工艺精度的限制。

3.尾电流增加,A v增加还是减小?一.设计过程:0. 确定正确的电路偏置,保证所有晶体管处于饱和区。

为保证良好的电流镜,并确保M4处于饱和区。

(Sx=Wx/Lx )由 I6=I7 得57462S S S S =1.根据需要的PM =60deg 求Cc (假定w z >10GB )c c L c 22.0>2.由已知的Cc 并根据转换速率的要求(或功耗要求)选择ISS (I5)的范围;3.由计算得到的电流偏置值(I5 /2),设计W3/L3( W4/L4 )满足上ICMR(或输出摆幅)要求,即饱和区条件;4.验证M3处镜像极点是否大于10GB;5.设计W1/L1(W2/L2 )满足GB的要求;6.设计W5/L5满足下ICMR(或输出摆幅)要求;7.根据Wp2>2.2GB 计算得到gm6;并且根据偏置条件VSG4=VSG6计算得到M6的尺寸;8.根据尺寸和gm6计算I6,并验证Vout,max是否满足要求;9.计算M7的尺寸。

超大规模集成电路第九次作业秋-段成华

超大规模集成电路第九次作业2016秋-段成华-CAL-FENGHAI.-(YICAI)-Company One1Assignment 91. Design an 8-bit up and down synchronous counter in VHDL with the following features:(1)The same ports are used for signals to be inputted andoutputted. The ports are bi-directionally buffered (three-state).(2)The counter is with an asynchronous reset that assigns aspecific initial value for counting.(3)The counter is with a synchronous data load control input fora new value of counting and an enable control input forallowing the up and down counting. The load control input hasa priority over the enable control input. This implies thatwhen the load operation is in process the counter operation is prohibited.(4)Some data types, such as STD_LOGIC, UNSIGNED, SIGNED andINTEGER, may be used.Synthesize the design. Create a set of reasonable input waveforms for your design and complete both behavioral and post-place&route simulations with internal signals and/or variables included in waveform or list windows.Solution:代码如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity count_8_bidir isPort (clk : in STD_LOGIC;rst : in STD_LOGIC;load : in STD_LOGIC;enable : in STD_LOGIC;cnt : inout STD_LOGIC_VECTOR (7 downto 0));end count_8_bidir;architecture Behavioral of count_8_bidir issignal cnt_in: STD_LOGIC_VECTOR (7 downto 0);signal cnt_out: STD_LOGIC_VECTOR (7 downto 0);beginpro0:process(oe,cnt_out,cnt)beginif(load='1')thencnt <= (others=>'Z');cnt_in <= cnt;elsecnt <= cnt_out;end if;end process;pro1:process(clk,rst)beginif(rst='1')thencnt_out <= (others=>'0');elsif rising_edge(clk)thenif(load='1')thencnt_out <= cnt_in;elsif(enable='1')thencnt_out <=cnt_out + 1;elsecnt_out <= cnt_out - 1;end if;end if;end process;end Behavioral;解释代码:这里有两个进程,进程0时是用来控制三态门控制的双向端口。

哈工大cmos模拟集成电路大作业

东线高速公路陵水立交改建工程圆管涵工程施工一、工程概况东线高速公路K190+899。

103陵水立交位于陵水县城西侧、在建的东环铁路陵水车站东侧,北距香水湾和南距文罗互通立交的距离分别为8。

3km和7。

8km.被交道路为国道海榆东线,高速公路上跨。

陵水立交现状为简易型立交,变速车道、匝道技术指标低,不满足现行规范要求,本项目的实施是针对该情况将现状陵水立交改建为半苜蓿叶式互通立交。

二、沿线地形、地质及水文自然地理特征1、地质水文:互通区地貌单元属海成Ⅳ级阶地,微地貌单元进一步划分为坡地和地沟.地下水主要接受大气降水及地下水侧向补给,总体向下游排泄。

勘察期间实测混合地下水位埋深为0。

00-2.5m,根据区域水文地质资料及附近水井调查,地下水位年变幅在0。

5—1。

0m。

本次勘察揭露的地层,表层为第四系全新统冲击土及第四系中更新统北海组海相沉积土,下伏晚白垩纪花岗闪长岩及其残积土。

2、气象:项目所在地属热带季风岛屿性气候,气候温和,雨量充沛,年平均气温24℃,夏季长达9个月,春秋不分,长3个月,无冬天。

夏季高温高湿,台风活动频繁,降水充沛,12-2月为春秋季,降水稀少,全年无霜日,日照充足,太阳辐射强.三、施工准备:施工前应先根据设计要求,对圆管涵进行定位放线,放出圆管涵具体位置,合理安排平面布置,应充分考虑施工期间的车辆通行情况和管线的施工方向之间的互相干扰。

根据规范要求,在充分了解工程的实际情况和选择合理经济的沟槽横断面。

并充分考虑冬季和雨期的施工措施,编制施工组织设计报监理审批,着重以下几点:(1)挖、填方的土方平衡计算,做出合理安排,减少重复运输。

(2)进行施工现场的排水设计,并考虑排水和周边构筑物的影响。

(3)考虑具体投入的设备、数量、品种、人员等。

(4)土方开挖后弃土的堆放、运输以及可利用土的临时堆放点的布置等.四、钢筋砼圆管涵施工管涵施工完毕后,砌体砂浆或砼强度达到规定要求时方可进行回填,涵洞顶以上及涵身两侧在不小于两倍孔径范围内的填土须分层对称夯实,相对密度达到96%,回填材料严格按设计要求,每层厚度不超过15cm。

网络系统集成与优化-大作业

网络系统集成与优化大作业

网络系统集成是各种网络技术应用在信息系统构建的具体表现形式,涵盖了网络技术应用的各个方面,在数字化、信息化中承担着基础性和关键性的重要作用。

请根据你对网络系统集成的认识和理解,以及你所掌握的网络技术知识和技能,以图文并茂的形式,系统阐述网络系统集成的实施过程和方法。

具体要求如下:

1、阐述网络系统集成的目的、任务和实施过程。

(30分,可采取分条列举和绘制流程图相结合的形式。

)

2、结合你技术专长和具体案例,完成网络系统集成某一过程或者某一功能模块的需求分析、详细设计和测试。

(50分,要求案例尽可能联系实际、真实具体,内容翔实,结构完整。

)

3、网络系统集成项目完成后,随着新应用、新技术、新问题的出现,系统面临着优化的问题。

请阐述系统优化时应注意哪些问题,可以采取哪些策略,可以使用哪些工具和技术进行优化。

(20分,此问题为开放性问题,要求阐述观点明确,论证有说服力,实施有可行性。

)

4、其它要求:

●独立完成作业

●11月18日前提交电子稿和打印稿

●格式规范、内容充实、语言表达准确。

《电子控制系统中的集成电路作业设计方案-2023-2024学年高中通用技术地质版》

《电子控制系统中的集成电路》作业设计方案第一课时一、设计背景和意义当今社会,电子控制系统已经无处不在,几乎贯穿生活的方方面面。

而集成电路作为电子控制系统的核心组成部分,具有高度集成、稳定性好、功耗低等优点,被广泛应用于各种电子设备中。

因此,掌握集成电路的设计原理和技术方法对于提升电子控制系统的性能具有重要意义。

二、设计目标本次作业设计旨在通过理论学习和实践操作,让学生深入了解集成电路的工作原理、设计方法和应用场景,提高其在电子控制系统领域的设计能力和实践技能。

三、设计内容1. 学习目标:(1)了解集成电路的基本概念和分类;(2)掌握集成电路的设计原理和设计流程;(3)学习常见集成电路的应用场景和设计案例。

2. 设计步骤:(1)理论学习:通过课堂讲解、教材阅读和相关资料查阅,学习集成电路的基本概念、功能和工作原理,了解集成电路的分类和特点;(2)设计方案:根据所学知识,设计一个包含集成电路的电子控制系统方案,包括硬件组成、软件编程等内容;(3)实验操作:搭建电子控制系统的实验平台,进行集成电路的测试和调试,验证设计方案的可行性和稳定性;(4)数据分析:分析实验结果,总结经验教训,完善设计方案,提出改进建议;(5)报告撰写:撰写实验报告,总结设计过程和成果,展示实验成果和心得体会。

四、设计要求1. 设计思路清晰,操作规范,结果准确可靠;2. 实验数据真实可靠,结论合理有效;3. 设计报告内容完整,结构清晰,文字表达流畅;4. 鼓励创新设计,提倡合作交流,展示设计成果。

五、评分标准1. 设计方案:30%2. 实验操作:30%3. 数据分析:20%4. 报告撰写:20%六、参考资料1. 《集成电路设计与应用》2. 《电子控制系统原理与设计》3. 相关学术论文和资料七、总结通过本次作业设计,学生将能够深入了解集成电路的设计原理和应用,掌握电子控制系统的设计方法和实践技能,提升综合能力和动手能力,为将来从事电子工程领域的研究和实践奠定基础。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

系统集成与应用实验设计报告16路模拟信号发生器班级:小组成员:指导教师:目录一、设计任务和要求分析 (2)二、整体方案设计选择 (2)三、理论计算 (6)四、电路设计及仿真 (7)五、实验总结 (11)六、附录 (12)一、设计任务与要求分析1.1设计任务用C8051F020单片机完成16路信号源的输出,并通过单片机内部A/D转换器进行输出信号源的反馈采样,最后通过异步串行接口(UART)将采样结果输出。

利用C8051单片机将波形量化数据放置于内部ROM,通过内部D/A产生信号以及I/O 端口控制多路模拟开关,同时生成16路信号源,注意信号源调理电路中采保部分的选值,并给出理论计算结果。

反馈回采部分采用单片机的12位高精度A/D 转换器,采样频率自定(要求给出理论计算值),并通过UART接口将采样值送出按9600bps的波特率发出(接收对象可以是计算机或其它)。

1.2 任务要求分析我们通过集体讨论与分析,确定了如下的设计流程:图1.系统流程图在进行具体的实验设计之后,我们进行了电路简化,放大滤波通过一个运算放大器来实现,不仅使电路得到了简化,而且也节省了资源。

二、整体方案设计选择2.1 单片机部分单片机选用C8051F020,是完全集成的混合信号系统级MUC芯片具有64个数字I/O引脚;具有12位100kps的8通道ADC,带PGA和多路模拟开关;具有2个12位DAC,具有可编程数据更新方式;64K可在系统编程的FLASH存储器;4352字节的片内RAM;可寻址64K字节地址空间的数据存储器接口:2个UART串行接口。

基于以上优良特性,故选用该单片机。

单片机具有上电复位、掉电复位、外部复位、软件强制复位等多种复位方式。

在应用中外部复位方式得到广泛应用。

外部/RST引脚提供使用外部电路使单片机强制复位的手段。

在外部/RST引脚加一个低电平有效信号,将使单片机复位,最好提供一个外部上拉,或对RST引脚去耦以防止噪声引起复位。

图2 单片机外部电路2.2 电源部分设计电源的选定好与坏对于系统设计来说至关重要,一个好的电源的设计标志着成功的一半。

在这个系统中我们需要用到一个正负5V的双电源,用于给运放LM358供电,尽管LM358可以采用单电源供电,但是输入信号的幅度比较小时,用单电源供电运算放大器的特性会变差,而我们的设计中,输入信号的变化范围较大,,用双电源比较合适。

同时还需要给模拟开关ADG406和构成采样保持电路的CA3140提供正5V的电源电压。

综上所述,我们通过用LM7805,LM7905组成一个正负5V的双电源电路提供正负5V的电源。

此外,C8051F020的供电电压为3.3V,所以我们还需要用LM1117(低压差三端稳压器)将5V电源转换为3.3V给C8051F020单片机供电。

图3. 7805设计参考资料图4. 7905设计参考资料2.3模拟开关部分在整个设计中,我们的多路模拟开关采用ADG406,单芯片CMOS 模拟多路复用器。

ADG406根据4位二进制地址线A0,A1,A2,A3所确定的地址,将16路输入之一切换至公共输出。

所有器件均提供EN 输入,用来使能或禁用器件。

禁用时,所有通道均关闭。

ADG406采用增强型LC2MOS 工艺设计,具有低功耗,高开关速度和低导通电阻特性,因而适合高速度数据采集系统和音频信号开关应用。

低功耗特性则适合电池供电系统。

接通时,各通道在两个方向的导电性能相同,输入信号范围可扩展至电源电压范围。

在断开的条件下,达到电源电压的信号电平被阻止。

所有通道均采用先开后合式开关,防止开关通道时发生瞬时短路。

设计本身具有低电荷注入特性,当切换数字输入时,可实现最小的瞬变。

我们采用ADG406进行采样时的16路信号的切换以及将16路信号输入单片机AD 时的16路信号切换。

图5.ADG406真值表以及转换时间2.4 信号调理部分设计2.4.1采样保持电路采样保持电路采用的是CA3140集成采样保持芯片。

它的输入阻抗高达1210 ,输入偏流约10PA,工作速度较高(SR=9V/us),常用于积分及保持电路等。

它既可以双电源供电(±2V~±18V),又可以单电源供电(4V~36V)。

其工作温度范围为-55℃~-125℃,使用CA3140的注意事项如下:(1)因其输入级为MOSFET,故安装焊接时应符合MOSFET的要求。

(2)CA3140的最大允许差模电压为±8V,故一般应接保护电路,以免因电压过高而击穿,其输入回路电流应小于1mA,因此需在输入及反馈回路中接限流电阻,其值一般不小于3.9KΩ。

(3)其输出负载电阻应大于2kΩ,否则将使负向输出动态范围变小。

2.4.2放大滤波器部分由于C8051F020的AD转换器输出电压为2.4V,且在实际线路输出过程中会受到噪声干扰,所以需要设计放大滤波电路。

我们选用LM358芯片进行放大滤波,不仅可以简化电路,并且成本较低。

三、理论计算3.1 DAC 输出频率通过手册可知,C8051F020内部DAC 最高输出频率为100kHz ,模拟开关最快切换时间为180ns ,采样保持电路的采样时间约为4.5ns ,计算如下:180+4.5=184.5ns所以DA 的采样周期必须比184.5ns 大,这里我们取DA 的输出周期为184.5*3=553.5ns 。

即频率约为:190000hz ,但是却超过了C8051F020内部DAC 最高输出频率为100kHz 。

所以只要低于190000hz 就可以了,为了以后的设计方便,也为了能够在采集一个周期中尽可能多的点,我们取DAC 输出频率为1600Hz. 此时每一路模拟开关的输出频率为100Hz 。

3.2 ADC 回采频率计算依据题目ADC 回采后经串口发送,串口波特率为9600,所以ADC 回采频率受到串口波特率制约,所以取ADC 回采频率与串口波特率一致:96001200b 8ps = 所以ADC 采集每一路模拟信号的频率为1.2kHz 。

3.3 采样保持电容计算采样保持电容大小选取受到切换速度的制约,与模拟开关、输出放大器的性能都有关系,具体计算如下:41s 32i =.8s= 2.880sR C R C ττ--≤⨯≥⨯切换时间110轮换时间1计算得: 79.4710p 0.11F C F μ-⨯<<结果取0.01uf 的电容。

3.4 滤波器的设计计算由于C8051F020的AD 转换器输出电压为2.4V ,而其内部的DA 转换器的输入电压可以达到4.8V ,且在实际线路输出过程中会受到噪声干扰,所以我们采用放大倍数为2倍的低通滤波器。

我们设计的滤波器是无限增益多路型低通滤波器,滤波器的参数分别如下:12325.65,32.92,51.30R k R k R k =Ω=Ω=Ω,120.1,0.015C F C F μμ==所以,增益312p R K R =-=-,固有频率02628.93w C ==,阻尼系数为:011231111()/ 1.413w C R R R α=++=。

所以截至频率为0/2100w Hz π=。

四、电路设计及仿真4.1 电源设计及仿真图6.双电源设计电路图图7.双电源仿真结果图4.2 放大滤波设计及仿真设计及仿真由于C8051F020的AD 转换器输出电压为2.4V ,而其内部的DA 转换器的输入电压可以达到4.8V ,且在实际线路输出过程中会受到噪声干扰,所以我们采用放大倍数为2倍的低通滤波器。

我们设计的滤波器是无限增益多路型低通滤波器,滤波器的参数分别如下:12325.65,32.92,51.30R k R k R k =Ω=Ω=Ω,120.1,0.015C F C F μμ==所以,增益312p R K R =-=-,固有频率02628.93w C ==,阻尼系数为:011231111()/1.413w C R R R α=++=。

所以截至频率为0/2100w Hz π=。

图8.低通滤波及放大电路图9.低通滤波及放大电路仿真图4.3采用保持电路的设计图10.采样保持电路原理图4.4模拟开关电路设计图11.模拟开关电路原理图4.5抗干扰设计图12.耦合电容设计图13.地隔离的设计4.6 整体电路设计图14.整体电路原理图4.7 pcb设计图15.pcb版图五、实验总结这次课程设计我们先从C8051F020芯片的引脚功能和工作原理入手。

将里面所涉及到的功能用我所学的系统集成以及模数电、测控电路的知识进行运用。

在实现电路的稳压功能时,用到了7805和7905,LM1117这三种芯片。

在设计电路的过程中,我们发现芯片的选择是非常重要的一个环节,芯片的参数以及功能和成本都是我们需要考虑的问题。

同时这次课程设计让我们小组成员进一步巩固了对Multisim软件仿真和AD 的使用和操作,在设计中遇到了很多问题,我们通过上网查资料以及同学和老师的帮助,大都得到了解决。

除此之外,小组成员也感受到了合作的力量,积极分工,在做好自己的工作的同时,协助其他成员。

在此,感谢老师的悉心指导和他同学的无私帮助!附录:程序源码:#include <c8051f020.h> // SFR declarations//-----------------------------------------------------------------------------// 16-bit SFR Definitions for 'F02x//-----------------------------------------------------------------------------sfr16 RCAP4 = 0xE4; // Timer4 capture/reloadsfr16 TMR4 = 0xF4; // Timer4sfr16 DAC0 = 0xd2; // DAC0 datasfr16 DAC1 = 0xd5; // DAC1 data//-----------------------------------------------------------------------------// Global Constants//-----------------------------------------------------------------------------#define SYSCLK 22118400 // Internal oscillator frequency in Hz#define SAMPLE_RATE_DAC 100000L // DAC sampling rate in Hz#define PHASE_PRECISION 65536 // range of phase accumulator#define FREQUENCY 1000 // Frequency of output waveform in Hz// <PHASE_ADD> is the change in phase between DAC samples; It is used in// the set_DACs routine.unsignedint PHASE_ADD = FREQUENCY * PHASE_PRECISION / SAMPLE_RATE_DAC;////////////自加////////////////unsigned long AD;//AD转换的值unsigned char temp_l;unsigned char temp_h;bit ReceiveBit; /*接收标志位*/unsigned char temp;////////////////////////////int code SINE_TABLE[256] = {0x0000, 0x0324, 0x0647, 0x096a, 0x0c8b, 0x0fab, 0x12c8, 0x15e2,0x18f8, 0x1c0b, 0x1f19, 0x2223, 0x2528, 0x2826, 0x2b1f, 0x2e11,0x30fb, 0x33de, 0x36ba, 0x398c, 0x3c56, 0x3f17, 0x41ce, 0x447a,0x471c, 0x49b4, 0x4c3f, 0x4ebf, 0x5133, 0x539b, 0x55f5, 0x5842,0x5a82, 0x5cb4, 0x5ed7, 0x60ec, 0x62f2, 0x64e8, 0x66cf, 0x68a6,0x6a6d, 0x6c24, 0x6dca, 0x6f5f, 0x70e2, 0x7255, 0x73b5, 0x7504,0x7641, 0x776c, 0x7884, 0x798a, 0x7a7d, 0x7b5d, 0x7c29, 0x7ce3,0x7d8a, 0x7e1d, 0x7e9d, 0x7f09, 0x7f62, 0x7fa7, 0x7fd8, 0x7ff6,0x7fff, 0x7ff6, 0x7fd8, 0x7fa7, 0x7f62, 0x7f09, 0x7e9d, 0x7e1d,0x7d8a, 0x7ce3, 0x7c29, 0x7b5d, 0x7a7d, 0x798a, 0x7884, 0x776c,0x7641, 0x7504, 0x73b5, 0x7255, 0x70e2, 0x6f5f, 0x6dca, 0x6c24,0x6a6d, 0x68a6, 0x66cf, 0x64e8, 0x62f2, 0x60ec, 0x5ed7, 0x5cb4,0x5a82, 0x5842, 0x55f5, 0x539b, 0x5133, 0x4ebf, 0x4c3f, 0x49b4,0x471c, 0x447a, 0x41ce, 0x3f17, 0x3c56, 0x398c, 0x36ba, 0x33de,0x30fb, 0x2e11, 0x2b1f, 0x2826, 0x2528, 0x2223, 0x1f19, 0x1c0b,0x18f8, 0x15e2, 0x12c8, 0x0fab, 0x0c8b, 0x096a, 0x0647, 0x0324,0x0000, 0xfcdc, 0xf9b9, 0xf696, 0xf375, 0xf055, 0xed38, 0xea1e, 0xe708, 0xe3f5, 0xe0e7, 0xdddd, 0xdad8, 0xd7da, 0xd4e1, 0xd1ef, 0xcf05, 0xcc22, 0xc946, 0xc674, 0xc3aa, 0xc0e9, 0xbe32, 0xbb86, 0xb8e4, 0xb64c, 0xb3c1, 0xb141, 0xaecd, 0xac65, 0xaa0b, 0xa7be, 0xa57e, 0xa34c, 0xa129, 0x9f14, 0x9d0e, 0x9b18, 0x9931, 0x975a, 0x9593, 0x93dc, 0x9236, 0x90a1, 0x8f1e, 0x8dab, 0x8c4b, 0x8afc, 0x89bf, 0x8894, 0x877c, 0x8676, 0x8583, 0x84a3, 0x83d7, 0x831d, 0x8276, 0x81e3, 0x8163, 0x80f7, 0x809e, 0x8059, 0x8028, 0x800a, 0x8000, 0x800a, 0x8028, 0x8059, 0x809e, 0x80f7, 0x8163, 0x81e3, 0x8276, 0x831d, 0x83d7, 0x84a3, 0x8583, 0x8676, 0x877c, 0x8894, 0x89bf, 0x8afc, 0x8c4b, 0x8dab, 0x8f1e, 0x90a1, 0x9236, 0x93dc, 0x9593, 0x975a, 0x9931, 0x9b18, 0x9d0e, 0x9f14, 0xa129, 0xa34c, 0xa57e, 0xa7be, 0xaa0b, 0xac65, 0xaecd, 0xb141, 0xb3c1, 0xb64c, 0xb8e4, 0xbb86, 0xbe32, 0xc0e9, 0xc3aa, 0xc674, 0xc946, 0xcc22, 0xcf05, 0xd1ef, 0xd4e1, 0xd7da, 0xdad8, 0xdddd, 0xe0e7, 0xe3f5, 0xe708, 0xea1e, 0xed38, 0xf055, 0xf375, 0xf696, 0xf9b9, 0xfcdc, };//-----------------------------------------------------------------------------// Function Prototypes//-----------------------------------------------------------------------------void main(void);voidOSCILLATOR_Init(void);void DAC0_Init (void);void DAC1_Init (void);void TIMER4_Init(int counts);voidSet_DACs(void);//////////////自加///////////////voidPORT_Init (void);void Timer3_Init (int counts);voidADC_Init(void);void UART0_Init (void);voiddelayms(unsigned int z);//////////////////////////////-----------------------------------------------------------------------------// MAIN Routine//-----------------------------------------------------------------------------void main (void){unsigned char temp1=0xff,temp2=0xff;unsignedintad_now;WDTCN = 0xde; // Disable watchdog timerWDTCN = 0xad;OSCILLATOR_Init (); // Initialize oscillatorDAC0_Init (); // Initialize DAC0PORT_Init ();Timer3_Init (SYSCLK / 1200 );ADC_Init();UART0_Init();AMX0SL =0x00; //选择通道AIN0TIMER4_Init(SYSCLK/SAMPLE_RATE_DAC);// Initialize Timer4 to overflow// <SAMPLE_RATE_DAC> times per// secondEA = 1; // Enable global interrupts ES0 =1;//串口中断使能while(1){temp1=0xff;temp2=0xff;ad_now=AD;temp1&=ad_now;temp2&=(ad_now>>8);SBUF0=temp1;while(!TI0);TI0=0;SBUF0=temp2;while(!TI0);TI0=0;SBUF0=0x0d;while(!TI0);TI0=0;SBUF0=0x0a;while(!TI0);TI0=0;delayms(200);}}////////////////自加//////////////////voiddelayms(unsigned int z){unsignedintx,y;for(x=0;x<z;x++)for(y=0;y<121;y++);}voidPORT_Init (void){XBR2 = 0x40; /*使能交叉开关*/P2MDOUT =0xff;// XBR0 = 0x04; /*使能UART0*/// XBR1 = 0x00;// //XBR2 = 0x40; /*使能交叉开关和弱上拉*/ // P0MDOUT |= 0x01; /*使能TX0作为推挽输出*/ // P1MDOUT |= 0x40; /*时能P1.6 (LED)作为推挽输出*/// P3MDOUT |= 0xdf;XBR0 = 0x04; /*使能UART0*/}//函数功能: 定时器3初始化//入口参数: int countsvoid Timer3_Init (int counts){TMR3CN = 0x00;TMR3RLL = -counts; //初始化重载值TMR3L = 0xffff; //设置自动重载值TMR3CN |= 0x04;}//函数功能: ADC0初始化voidADC_Init(void){ADC0CN |=0x84; /*ADC0使能,定时器3溢出使能模/数转换*/REF0CN |=0x03; /*内部电压基准提供从VREF脚输出,ADC0电压基准取自VREF0*/ADC0CF |=0x50; /*转换周期和增益为1*/AMX0CF |=0x00; /*单端输入*/EIE2 |=0x02; /*ADC0转换结束中断*/}//函数功能: AD中断服务程序void ADC_ISR (void) interrupt 15{AD0INT=0; //清A/D中断标志temp_l=ADC0L;temp_h=ADC0H;AD=temp_h*256+temp_l;}void UART0_Init (void){SCON0=0x50; //串口方式1TMOD=0X20; //选用定时器1作为波特率发生器TH1=0xF4;TL1=0xF4;PCON=0x80; //波特率为9600TR1=1; //定时器启动}void UART0_ISR (void) interrupt 4{// if(TI0) //是发送中断还是接收中断// {// SBUF0=AD;// while(!TI0);// TI0=0;// }}////////////////////////////////////-----------------------------------------------------------------------------// Interrupt Service Routines//-----------------------------------------------------------------------------//-----------------------------------------------------------------------------// TIMER4_ISR -- Wave Generator//-----------------------------------------------------------------------------//// This ISR is called on Timer4 overflows. Timer4 is set to auto-reload mode // and is used to schedule the DAC output sample rate in this example.// Note that the value that is written to DAC1 during this ISR call is// actually transferred to DAC1 at the next Timer4 overflow.////-----------------------------------------------------------------------------void TIMER4_ISR (void) interrupt 16{static unsigned char ch_i;ch_i++;if(ch_i==16){ch_i=0;Set_DACs();}P2=ch_i;T4CON &= ~0x80; // Clear Timer4 overflow flag}//-----------------------------------------------------------------------------// Initialization Routines//-----------------------------------------------------------------------------//-----------------------------------------------------------------------------// OSCILLATOR_Init//-----------------------------------------------------------------------------//// Return Value : None// Parameters : None//// This routine initializes the system clock to use an 22.1184MHz crystal// as its clock source.////-----------------------------------------------------------------------------voidOSCILLATOR_Init (void){inti; // Delay counterOSCXCN = 0x67; // Start external oscillator with// 22.1184MHz crystalfor (i=0; i< 256; i++) ; // Wait for osc. to start upwhile (!(OSCXCN & 0x80)) ; // Wait for crystal osc. to settleOSCICN = 0x88; // Select external oscillator as SYSCLK// source and enable missing clock// detector}//-----------------------------------------------------------------------------// DAC0_Init//-----------------------------------------------------------------------------//// Return Value : None// Parameters : None//// Configure DAC0 to update on Timer4 overflows and enable the the VREF buffer.////-----------------------------------------------------------------------------void DAC0_Init(void){DAC0CN = 0x94; // Enable DAC0 in left-justified mode// managed by Timer4 overflowsREF0CN |= 0x03; // Enable the internal VREF (2.4v) and// the Bias Generator }//-----------------------------------------------------------------------------// TIMER4_Init//-----------------------------------------------------------------------------//// Return Value : None// Parameters :// 1) int counts - calculated Timer overflow rate// range is positive range of integer: 0 to 32767//// Configure Timer4 to auto-reload at interval specified by <counts> using// SYSCLK as its time base.////-----------------------------------------------------------------------------void TIMER4_Init (int counts){T4CON = 0x00; // Stop Timer4; Clear overflow flag (TF4);// Set to Auto-Reload ModeCKCON |= 0x40; // Timer4 counts SYSCLKsRCAP4 = -counts; // Set reload valueTMR4 = RCAP4; // Initialzie Timer4 to reload valueEIE2 |= 0x04; // Enable Timer4 interruptsT4CON |= 0x04; // Start Timer4}//-----------------------------------------------------------------------------// Set_DACs//-----------------------------------------------------------------------------//// Return Value : None// Parameters : None//// Calculates the update values for the two DACs using SINE_TABLE. The DACs // will actually be updated upon the next Timer4 interrupt. Until that time,// the DACs will hold their current value.////-----------------------------------------------------------------------------voidSet_DACs(void){static unsigned phase_acc = 0; // Holds phase accumulatorintSIN_temp; // Temporary 16-bit variablesunsigned char index; // Index into SINE tablephase_acc += PHASE_ADD; // Increment phase accumulator index = phase_acc>> 8;SIN_temp = SINE_TABLE[index]; // Read the table value// Add a DC bias to change the the rails from a bipolar (-32768 to 32767) // to unipolar (0 to 65535)// Note: the XOR with 0x8000 translates the bipolar quantity into// a unipolar quantity.DAC0 = SIN_temp ^ 0x8000;}//-----------------------------------------------------------------------------// End Of File。