7448简介及数码管简介

7448数码管译码器逻辑符号

7448数码管译码器逻辑符号7448数码管是一种BCD-七段译码器,它接收4位二进制代码并输出对应的七段LED表示数字。

它是数字电子电路中常见的一种集成电路,常用于数码显示器和计数器等应用。

在本文中,我们将深入探讨7448数码管译码器的逻辑符号,以及其在数字电子电路中的重要作用。

1. 7448数码管译码器的基本原理7448数码管译码器是一种具有4个输入线和7个输出线的集成电路。

它将输入的4位二进制代码转换为对应的七段LED的亮灭状态,从而显示出相应的数字。

其基本逻辑符号如下:A(输入)B(输入)C(输入)D(输入)a(输出)b(输出)c(输出)d(输出)e(输出)f(输出)g(输出)G2A(输入)G2B(输入)LT(输入)其中,A、B、C、D是输入端,表示输入的四位二进制代码;a、b、c、d、e、f、g是输出端,表示七段LED的亮灭情况;G2A、G2B、LT是特殊输入端,用于控制显示方式。

2. 7448数码管译码器的工作原理当输入了一个4位二进制代码时,7448数码管译码器会根据该代码的含义,输出相应的七段LED的亮灭状态,从而显示出对应的数字。

当输入0000时,数码管显示的数字为0;当输入0001时,数码管显示的数字为1;依此类推,直到输入1111时,数码管显示的数字为F。

其工作原理如下:对于不同的输入二进制代码,7448数码管译码器会根据预先设定的真值表,输出相应的七段LED的亮灭状态。

这样,我们可以通过改变输入的二进制代码,来控制数码管显示的数字。

这种工作原理非常简单而直观,因此在数字电子电路中得到了广泛的应用。

3. 7448数码管译码器的重要作用7448数码管译码器作为一种重要的数字电子电路,具有以下几个重要的作用:3.1 数码显示器7448数码管译码器通常被用于数码显示器中,用来控制数码管显示的数字。

通过输入不同的四位二进制代码,我们可以控制数码管显示出任意数字,从而实现数字的显示功能。

(完整word版)7448简介及数码管简介

2.4 7448译码器7448是7段显示译码器,输出高电平有效的译码器。

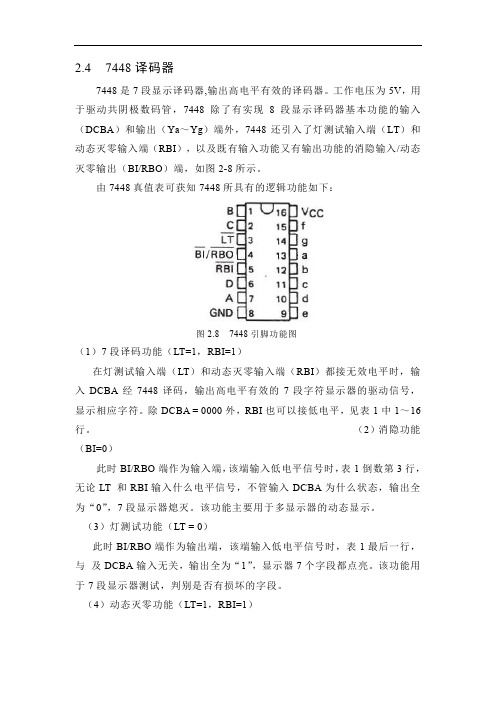

工作电压为5V,用于驱动共阴极数码管,7448除了有实现8段显示译码器基本功能的输入(DCBA)和输出(Ya~Yg)端外,7448还引入了灯测试输入端(LT)和动态灭零输入端(RBI),以及既有输入功能又有输出功能的消隐输入/动态灭零输出(BI/RBO)端,如图2-8所示。

由7448真值表可获知7448所具有的逻辑功能如下:图2.8 7448引脚功能图(1)7段译码功能(LT=1,RBI=1)在灯测试输入端(LT)和动态灭零输入端(RBI)都接无效电平时,输入DCBA经7448译码,输出高电平有效的7段字符显示器的驱动信号,显示相应字符。

除DCBA = 0000外,RBI也可以接低电平,见表1中1~16行。

(2)消隐功能(BI=0)此时BI/RBO端作为输入端,该端输入低电平信号时,表1倒数第3行,无论LT 和RBI输入什么电平信号,不管输入DCBA为什么状态,输出全为“0”,7段显示器熄灭。

该功能主要用于多显示器的动态显示。

(3)灯测试功能(LT = 0)此时BI/RBO端作为输出端,该端输入低电平信号时,表1最后一行,与及DCBA输入无关,输出全为“1”,显示器7个字段都点亮。

该功能用于7段显示器测试,判别是否有损坏的字段。

(4)动态灭零功能(LT=1,RBI=1)此时BI/RBO端也作为输出端,LT 端输入高电平信号,RBI 端输入低电平信号,若时DCBA = 0000,表1倒数第2行,输出全为“0”,显示器熄灭,不显示这个零。

DCB A≠0,则对显示无影响。

该功能主要用于多个7段显示器同时显示时熄灭高位的零。

(5)7448/SN7448译码器0-9真值表如表2.2所示:表2.2 7448/SN7448译码器0-9真值表数码管是一种半导体发光器件,其基本单元是发光二极管。

2.5.1产品分类数码管按段数分为七段数码管和八段数码管,八段数码管比七段数码管多一个发光二极管单元(多一个小数点显示);按能显示多少个“8”可分为1位、2位、4位等等数码管。

7448数码管译码器逻辑符号

7448数码管译码器逻辑符号7448数码管译码器是一种常用的数字逻辑集成电路,它能够将二进制代码转换为七段数码管上显示的相应数字和字母字符。

这种译码器具有广泛的应用,可以在计算机、通信、仪器仪表等领域中发挥重要作用。

7448数码管译码器的输入是一个4位的二进制代码,输出是对应的七段数码管上的显示字符。

它可以译码的输入范围是从0000到1111,对应的输出范围是从0到F(十六进制)。

下面我们来详细介绍7448数码管译码器的逻辑符号和工作原理。

7448数码管译码器的逻辑符号如下所示:```___D3 -| |- VccD2 -| |D1 -| |- aD0 -| |- bCPL -| |- cPL -| |- dGND -|___|- ef```其中,D0、D1、D2和D3是译码器的输入引脚,它们对应四位二进制代码的每一位。

a、b、c、d、e、f和g是译码器的输出引脚,它们对应七段数码管的每一段。

7448数码管译码器的工作原理如下:1. 根据输入的四位二进制代码,译码器将会识别出输入所对应的数字或字母字符。

2. 根据输入代码和译码表,译码器将会输出对应的七段数码管显示字符的控制信号。

3. 根据输出的控制信号,数码管将会点亮对应的段,从而显示出相应的数字或字母字符。

7448数码管译码器内部采用了译码表来实现将输入代码转换为显示字符的功能。

下面是一个简化的译码表示例:```________|__a___ |f| |b || g | ||_____|__||__g__| |e| |c || d | ||_____|__|```译码表中的每一行代表一个十六进制数字或字母字符。

每一列代表七段数码管的一个段,其中a、b、c、d、e、f和g对应译码器的输出引脚。

通过查表的方式,译码器可以准确选择正确的输出段,从而显示出正确的数字或字母字符。

7448数码管译码器的逻辑功能是通过门电路和触发器电路实现的。

它内部包含了多个与门、多个非门和多个触发器。

七段显示译码器7448功能引脚图及应用电路

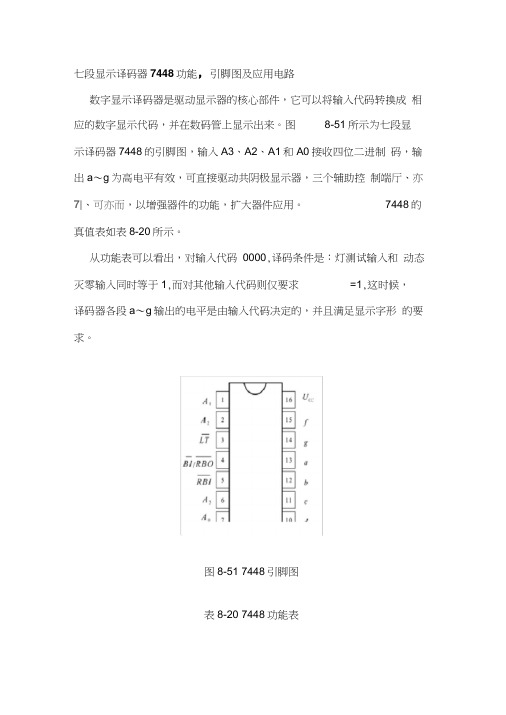

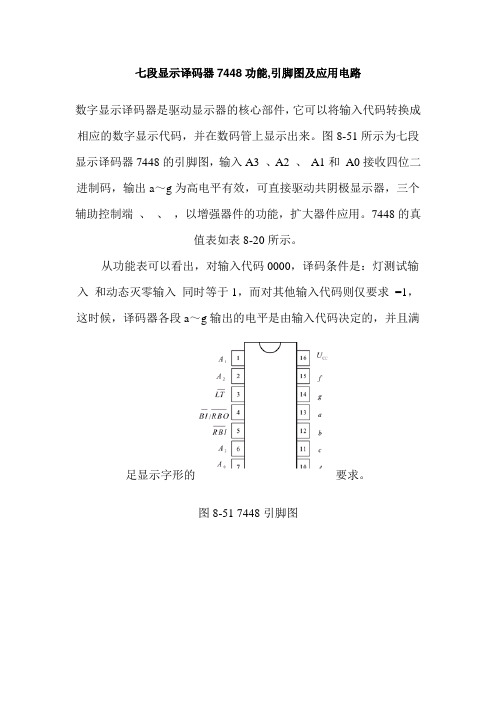

七段显示译码器7448功能,引脚图及应用电路数字显示译码器是驱动显示器的核心部件,它可以将输入代码转换成相应的数字显示代码,并在数码管上显示出来。

图8-51所示为七段显示译码器7448的引脚图,输入A3、A2、A1和A0接收四位二进制码,输出a〜g为高电平有效,可直接驱动共阴极显示器,三个辅助控制端厅、亦7|、可亦而,以增强器件的功能,扩大器件应用。

7448的真值表如表8-20所示。

从功能表可以看出,对输入代码0000,译码条件是:灯测试输入和动态灭零输入同时等于1,而对其他输入代码则仅要求=1,这时候,译码器各段a〜g输出的电平是由输入代码决定的,并且满足显示字形的要求。

图8-51 7448引脚图表8-20 7448功能表十轆数输入输出17A A A他。

住b d/s 01100u0I L11111011K00011011000021K00101110110131K D0111111100141K Q10010110011 1乂010]11011011«1011010011111710111111]0000>110001111111191*1001111110111011D1d100A1101111K101110n11001121K11D010i0D0]113111D111001011H1K111010001111151111]1D000000消隐:X00000000垃X X X K动态灭零1V00D000Q00000 0丈M艾11111111灯测试输入厅I低电平有效。

当厅=0时,无论其他输入端是什么状态,所有输出a〜g均为1,显示字形&该输入端常用于检查7448本身及显示器的好坏。

动态灭零输入亟低电平有效。

当厅=1,画川,且输入代码_ 1时,输出a〜g均为低电平,即与0000码相应的字形0 不显示,故称灭零”利用盯=1与画=0,可以实现某一位数码的消隐”时,厨亦而,其他情况下阪帀而=1。

7446 7447 数码管驱动芯片中文资料

7446/7447 数码管驱动芯片

目录

总体概述 (1)

引脚介绍 (1)

推荐使用条件 (2)

真值表 (3)

芯片应用总结: (4)

芯片应用注意事项: (5)

总体概述

7446和7447具有低电平有效输出,旨在直接驱动共阳极LED或白炽灯指示器。

芯片具有消隐功能、灭零功能以及数码管测试功能。

当输入端输入的二进制数在0-9时,可以数码管可以显示0-9,当输入端输入的二进制数在A-F时,数码管将显示不同的符号(非数字)。

芯片7446和芯片7447的基本逻辑功能相同,不同之处见“推荐使用条件”章节中表1和表2中标注红色底纹部分。

当BI/RBO节点处于高逻辑电平时,可以通过LT引脚测试数码管所有段的好坏。

芯片包含覆盖消隐输入引脚(BI),该引脚可用于控制灯强度(通过脉冲)或抑制输出。

引脚介绍

7446与7447的外观如图1所示。

该芯片共16个引脚。

其中16

1。

七段显示译码器7448

七段显示译码器7448功能,引脚图及应用电路数字显示译码器是驱动显示器的核心部件,它可以将输入代码转换成相应的数字显示代码,并在数码管上显示出来。

图8-51所示为七段显示译码器7448的引脚图,输入A3 、A2 、A1和A0接收四位二进制码,输出a~g为高电平有效,可直接驱动共阴极显示器,三个辅助控制端、、,以增强器件的功能,扩大器件应用。

7448的真值表如表8-20所示。

从功能表可以看出,对输入代码0000,译码条件是:灯测试输入和动态灭零输入同时等于1,而对其他输入代码则仅要求=1,这时候,译码器各段a~g输出的电平是由输入代码决定的,并且满足显示字形的要求。

图8-51 7448引脚图表8-20 7448功能表灯测试输入低电平有效。

当= 0时,无论其他输入端是什么状态,所有输出a~g均为1,显示字形8。

该输入端常用于检查7448本身及显示器的好坏。

动态灭零输入低电平有效。

当=1,,且输入代码时,输出a ~g均为低电平,即与0000码相应的字形0不显示,故称“灭零”。

利用=1与= 0,可以实现某一位数码的“消隐”。

灭灯输入/动态灭零输出是特殊控制端,既可作输入,又可作输出。

当作输入使用,且= 0时,无论其他输入端是什么电平,所有输出a~g均为0,字形熄灭。

作为输出使用时,受和控制,只有当,,且输入代码时,,其他情况下。

该端主要用于显示多位数字时多个译码器之间的连接。

【例8-13】七段显示器构成两位数字译码显示电路如图8-52所示。

当输入8421BCD码时,试分析两个显示器分别显示的数码范围。

图8-52 两位数字译码显示电路解:图8-52所示的电路中,两片7448的均接高电平。

由于7448(1)的,所以,当它的输入代码为0000时,满足灭零条件,显示器(1)无字形显示。

7448(2)的,所以,当它的输入代码为0000时,仍能正常显示,显示器(2)显示0。

而对其他输入代码,由于,译码器都可以输出相应的电平驱动显示器。

数码管简介[推荐阅读]

![数码管简介[推荐阅读]](https://img.taocdn.com/s3/m/1c94560cae45b307e87101f69e3143323868f578.png)

数码管简介[推荐阅读]第一篇:数码管简介(注:此文档内容均复制:数码管_百科名片,仅供下载方便。

)数码管百科名片数码管是一种半导体发光器件,其基本单元是发光二极管。

一产品分类数码管按段数分为七段数码管和八段数码管,八段数码管比七段数码管多一个发光二极管单元(多一个小数点显示);按能显示多少个“8”可分为1位、2位、4位等等数码管。

按发光二极管单元连接方式分为共阳极数码管和共阴极数码管。

共阳数码管是指将所有发光二极管的阳极接到一起形成公共阳极(COM)的数码管。

共阳数码管在应用时应将公共极COM接到+5V,当某一字段发光二极管的阴极为低电平时,相应字段就点亮。

当某一字段的阴极为高电平时,相应字段就不亮。

共阴数码管是指将所有发光二极管的阴极接到一起形成公共阴极(COM)的数码管。

共阴数码管在应用时应将公共极COM接到地线GND上,当某一字段发光二极管的阳极为高电平时,相应字段就点亮。

当某一字段的阳极为低电平时,相应字段就不亮。

二驱动方式数码管要正常显示,就要用驱动电路来驱动数码管的各个段码,从而显示出我们要的数字,因此根据数码管的驱动方式的不同,可以分为静态式和动态式两类。

1)静态显示驱动的I/O端口进行驱动,或者使用如BCD码二-十进制译码器译码进行驱动。

静态驱动的优点是编程简单,显示亮度高,缺点是占用I/O端口多,如驱动5个数码管静态显示则需要5×8=40根I/O端口来驱动,要知道一个89S51单片机可用的I/O端口才32个呢:),实际应用时必须增加译码驱动器进行驱动,增加了硬件电路的复杂性。

2)动态显示驱动数码管动态显示接口是单片机中应用最为广泛的一种显示方式之一,动态驱动是将所有数码管的8个显示笔划“a,b,c,d,e,f,g,dp”的同名端连在一起,另外为每个数码管的公共极COM增加位选通控制电路,位选通由各自独立的I/O线控制,当单片机输出字形码时,所有数码管都接收到相同的字形码,但究竟是那个数码管会显示出字形,取决于单片机对位选通COM端电路的控制,所以我们只要将需要显示的数码管的选通控制打开,该位就显示出字形,没有选通的数码管就不会亮。

TDA7448中文资料

1/13TDA7448December 2002This is preliminary information on a new product now in development. Details are subject to change without notice.s 6 CHANNEL INPUTS s 6 CHANNEL OUTPUTSs VOLUME ATTENUATION RANGE OF 0 TO -79dBs VOLUME CONTROL IN 1.0dB STEPS s 6 CHANNEL INDEPENDENT CONTROL sALL FUNCTION ARE PROGRAMMABLE VIA SERIAL BUSDESCRIPTIOThe TDA7448 is a 6 channel volume controller for quality audio applications in Multi-Channels Audio SystemsThanks to the used BIPOLAR/CMOS Technology,Low Distortion, Low Noise and DC stepping are ob-tained.PRODUCT PREVIEW6 CHANNEL VOLUME CONTROLLERTDA7448ABSOLUTE MAXIMUM RATINGSSymbol Parameter Value Unit V S Operating Supply Voltage10.5V T amb Operating Ambient Temperature-10 to 85°C T stg Storage Temperature Range-55 to 150°CTHERMAL DATASymbol Parameter Value Unit R th j-pin thermal Resistance junction-pins150°C/WQUICK REFERENCE DATASymbol Parameter Min.Typ.Max.Unit V S Supply Voltage 4.75910V V CL Max Input Signal Handling2Vrms THD Total Harmonic Distortion V = 1Vrms f =1KHz0.010.1% S/N Signal to Noise Ratio Vout = 1Vrms100dB S C Channel Separation f = 1KHz90dB Volume Control (1dB step)-790dBMute Attenuation90dB 2/13TDA7448 ELECTRICAL CHARACTERISTCS(refer to the test circuit T amb = 25°C, V S = 9V, R L = 10KΩ, R G = 600Ω, unless otherwise specified)Symbol Parameter Test Condition Min. Typ.Max.Unit SUPPLYV S Supply Voltage 4.75910VI S Supply Current7mASVR Ripple Rejection80dB INPUT STAGER IN Input Resistance355065KΩV CL Clipping Level THD = 0.3%2 2.5Vrms S IN Input Separation The selected input is grounded90dBthrough a 2.2µ capacitorVOLUME CONTROLC RANGE Control Range79dBA VMAX Max. Attenuation79dBA STEP Step Resolution0.51 1.5dBE A Attenuation Set Error A V = 0 to -24dB-101dBA V = -24 to -79dB-2.00 2.0dBE T Tracking Error A V = 0 to -24dB-101dBA V = -24 to -79dB-202dBV DC DC Step adyacent attenuation steps-303mVA mute Mute Attenuation90db AUDIO OUTPUTSV CLIP Clipping Level THD = 0.3%2 2.5Vrms R L Output Load Resistance2KΩV DC DC Voltage Level 4.5V GENERAL1015µVE NO Output Noise BW = 20Hz to 20KHzAll gains = 0dB, FlatS/N Signal to Noise Ratio All gains = 0dB; V O = 1Vrms100dB S C Channel Separation left/Right8090dB THD Distortion A V = 0; V I = 1Vrms0.010.1% BUS INPUTV Il Input Low Voltage1V V IH Input High Voltage 2.5VI IN Input Current V IN = 0.4V-55µAV O Output Voltage SDAI O = 1.6mA0.40.8VAchnowledge3/13TDA74484/13Figure 1. Test circuitAPPLICATION SUGGESTIONSThe volume control range is 0 to -79dB, by 1dB step resolution.The very high resolution allows the implementation of systems free from any noise acoustical effect.CREFThe suggested 10µF reference capacitor (CREF)value can be reduced to 4.7µF if the application re-quires faster power ON.Figure 2. THD vs. frequencyFigure 3. THD vs. R LOADFigure 4. Channel separation vs. frequencyTDA7448I2C BUS INTERFACEData transmission from microprocessor to the TDA7448 and vice versa takes place through the 2 wires I2C BUS in-terface, consisting of the two lines SDA and SCL (pull-up resistors to positive supply voltage must be connected).Data ValidityAs shown in fig. 1, the data on the SDA line must be stable during the high period of the clock. The HIGH and LOW state of the data line can only change when the clock signal on the SCL line is LOW.Start and Stop ConditionsAs shown in fig. 2 a start condition is a HIGH to LOW transition of the SDA line while SCL is HIGH. The stop condition is a LOW to HIGH transition of the SDA line while SCL is HIGH.Byte FormatEvery byte transferred on the SDA line must contain 8 bits. Each byte must be followed by an acknowledge bit. The MSB is transferred first.AcknowledgeThe master (µP) puts a resistive HIGH level on the SDA line during the acknowledge clock pulse (see fig. 5). The peripheral (audio processor) that acknowledges has to pull-down (LOW) the SDA line during this clock pulse.The audio processor which has been addressed has to generate an acknowledge after the reception of each byte, otherwise the SDA line remains at the HIGH level during the ninth clock pulse time. In this case the master transmitter can generate the STOP information in order to abort the transfer.Transmission without AcknowledgeAvoiding to detect the acknowledge of the audio processor, the µP can use a simpler transmission: simply it waits one clock without checking the slave acknowledging, and sends the new data.This approach of course is less protected from misworking.2225/13TDA74486/13SOFTWARE SPECIFICATION Interface ProtocolThe interface protocol comprises:s A start condition (S)s A chip address byte, containing the TDA7448 address s A subaddress bytess A sequence of data (N byte + acknowledge)sA stop condition (P))ACK = Acknowledge;S = Start;P = Stop; A = Address; B = Auto IncrementEXAMPLESNo Incremental BusThe TDA7448 receives a start condition, the correct chip address, a subaddress with the B = 0 (no incremental bus), N-data (all these data concern the subaddress selected), a stop condition.Incremental BusThe TDA7448 receivea start conditions, the correct chip address, a subaddress with the B = 1 (incremental bus):now it is in a loop condition with an autoincrease of the subaddress whereas SUBADDRESS from "XXX1000"to "XXX1111" of DATA are ignored.The DATA 1 concern the subaddress sent, and the DATA 2 concern the subaddress sent plus one in the loop etc, and at the end it receivers the stop condition.DATA BYTESAddress= 88 (HEX) (10001000): ADDR open; 8A (HEX) (10001010): connect to supply FUNCTION SELECTION: subaddressB=1: INCREMENTAL BUS; ACTIVE B=0: NO INCREMENTAL BUS X= DON’T CAREMSB LSB SUBADDRESSD7D6D5D4D3D2D1D0X X X B 0000SPEAKER A TTENUATION OUT 1X X X B 0001SPEAKER A TTENUATION OUT 2X X X B 0010SPEAKER ATTENUATION OUT 3X X X B 0011SPEAKER A TTENUATION OUT 4X X X B 0100SPEAKER A TTENUATION OUT 5X X X B 0101SPEAKER A TTENUATION OUT 6X X X B 0110NOT USED”XXXB111NOT USEDTDA7448 In Incremental Bus Mode, the three “not used” functions must be addressed in any case. For example to refresh “ Speaker Attenuation 3 = 0dB and Speaker Attenuation 6 = -40 dB”; the following bytes must be sent:SUBADDRESS XXX10010SPEAKER A TTENUATION OUT 1XXXXXXXXSPEAKER A TTENUATION OUT 2XXXXXXXXSPEAKER A TTENUATION OUT 300000000SPEAKER A TTENUATION OUT 4XXXXXXXXSPEAKER A TTENUATION OUT 5XXXXXXXXSPEAKER A TTENUATION OUT 600101111SPEAKER ATTENUATION SELECTIONMSB LSBSPEAKER ATTENUATION D7D6D5D4D3D2D1D00000dB001-1dB010-2dB011-3dB100-4dB101-5dB110-6dB111-7dB00000-0dB00001-8dB00010-16dB00011-24dB00100-32dB00101-40dB00110-48dB00111-56dB01-64dB10-72dB11MUTEvalue = 0 to -79dB and MUTE7/13TDA74488/13Figure 8. PIN:20Figure 9. PINS: 5, 6, 7, 14, 15, 16Figure 10. PINS: 2, 3, 4, 17, 18, 19Figure 11. PINS: 10Figure 12. PINS: 9TDA7448 Figure 13. Test and Application Circuit9/13TDA744810/13Figure 14. Component Layout (65 x 72mm)Figure 15. PC Board (Component side)TDA7448 Figure 16. PC Board (Solder side)11/1312/13Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics©2002 STMicroelectronics - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.13/13。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.4 7448译码器

7448是7段显示译码器,输出高电平有效的译码器。

工作电压为5V,用于驱动共阴极数码管,7448除了有实现8段显示译码器基本功能的输入(DCBA)和输出(Ya~Yg)端外,7448还引入了灯测试输入端(LT)和动态灭零输入端(RBI),以及既有输入功能又有输出功能的消隐输入/动态灭零输出(BI/RBO)端,如图2-8所示。

由7448真值表可获知7448所具有的逻辑功能如下:

图2.8 7448引脚功能图

(1)7段译码功能(LT=1,RBI=1)

在灯测试输入端(LT)和动态灭零输入端(RBI)都接无效电平时,输入DCBA经7448译码,输出高电平有效的7段字符显示器的驱动信号,显示相应字符。

除DCBA = 0000外,RBI也可以接低电平,见表1中1~16行。

(2)消隐功能(BI=0)

此时BI/RBO端作为输入端,该端输入低电平信号时,表1倒数第3行,无论LT 和RBI输入什么电平信号,不管输入DCBA为什么状态,输出全为“0”,7段显示器熄灭。

该功能主要用于多显示器的动态显示。

(3)灯测试功能(LT = 0)

此时BI/RBO端作为输出端,该端输入低电平信号时,表1最后一行,与及DCBA输入无关,输出全为“1”,显示器7个字段都点亮。

该功能用于7段显示器测试,判别是否有损坏的字段。

(4)动态灭零功能(LT=1,RBI=1)

此时BI/RBO端也作为输出端,LT 端输入高电平信号,RBI 端输入低电平信号,若时DCBA = 0000,表1倒数第2行,输出全为“0”,显示器熄灭,不显示这个零。

DCB A≠0,则对显示无影响。

该功能主要用于多个7段显示器同时显示时熄灭高位的零。

(5)7448/SN7448译码器0-9真值表如表2.2所示:

表2.2 7448/SN7448译码器0-9真值表

数码管是一种半导体发光器件,其基本单元是发光二极管。

2.5.1产品分类

数码管按段数分为七段数码管和八段数码管,八段数码管比七段数码管多一个发光二极管单元(多一个小数点显示);按能显示多少个“8”可分为1位、2位、4位等等数码管。

按发光二极管单元连接方式分为共阳极数码管和共阴极数码管。

共阳极数码管是指将所有发光二极管的阳极接到一起形成公共阳极(COM)的数码管。

共阳极数码管在应用时应将公共极COM接到+5V,当某一字段发光二极管的阴极为低电平时,相应字段就点亮。

当某一字段的阴极为高电平时,相应字段就不亮。

共阴极数码管是指将所有发光二极管的阴极接到一

起形成公共阴极(COM)的数码管。

共阴极数码管在应用时应将公共极COM 接到地线GND上,当某一字段发光二极管的阳极为高电平时,相应字段就点亮。

当某一字段的阳极为低电平时,相应字段就不亮。

2.5.2 驱动方式

数码管要正常显示,就要用驱动电路来驱动数码管的各个段码,从而显示出我们要的数字,因此根据数码管的驱动方式的不同,可以分为静态式和动态式两类。

1) 静态显示驱动

静态驱动也称直流驱动。

静态驱动是指每个数码管的每一个段码都由一个单片的I/O端口进行驱动,或者使用如BCD码二-十进制译码器译码进行驱动。

静态驱动的优点是编程简单,显示亮度高,缺点是占用I/O端口多,如驱动5个数码管静态显示则需要5×8=40根I/O端口来驱动,要知道一个89S51单片机可用的I/O端口才32个,实际应用时必须增加译码驱动器进行驱动,增加了硬件电路的复杂性。

图2.9 LED静态驱动电路

2) 动态显示驱动

数码管动态显示接口是单片机中应用最为广泛的一种显示方式之一,动态驱动是将所有数码管的8个显示笔划"a,b,c,d,e,f,g,dp"的同名端连在一起,另外为每个数码管的公共极COM增加位选通控制电路,位选通由各

自独立的I/O线控制,当单片机输出字形码时,所有数码管都接收到相同的字形码,但究竟是那个数码管会显示出字形,取决于单片机对位选通COM 端电路的控制,所以我们只要将需要显示的数码管的选通控制打开,该位就显示出字形,没有选通的数码管就不会亮。

通过分时轮流控制各个数码管的COM端,就使各个数码管轮流受控显示,这就是动态驱动。

在轮流显示过程中,每位数码管的点亮时间为1~2ms,由于人的视觉暂留现象及发光二极管的余辉效应,尽管实际上各位数码管并非同时点亮,但只要扫描的速度足够快,给人的印象就是一组稳定的显示数据,不会有闪烁感,动态显示的效果和静态显示是一样的,能够节省大量的I/O端口,而且功耗更低。

图2.10 LED动态驱动电路

本设计选用的数码管为05621B型号的双位共阴极数码管,输入信号为7448译码器输出的二进制信号。

数码管实物及其引脚图如

图2.11 数码管实物图

图2.12 数码管引脚图

3) LED显示驱动芯片

随着单片机技术的发展,许多公司都推出了专用LED显示驱动芯片,如Microchip公司的A Y0438、Maxim公司的MAX7219等都是其中的典型代表。

MAX7219是Maxim公司推出的8位LED串行显示驱动器,它采用3线串口传送数据,占用资源少且硬件简单,只需一个外部电阻即可方便地调节LED的亮度;可灵活地选择显示器的个数( 1~8个, 级联可成倍增加);可进行译码或不译码显示;内含硬件动态扫描控制,可设置低功耗停机方式。

MAX7219引脚功能和工作原理:MAX7219采用24脚双列直插式封装,其引脚如图3所示。

SEGA~SEGG和DP分别为LED七段驱动器线和小数点线,供给显示器源电流;DIG0~DIG7为8位数字驱动线,输出位选信号,从每位LED共阴极吸入电流。

图2.13 MAX7219 引脚功能

DIN是串行数据输入端。

在CLK 的上升沿,一位数据被加载到内部16位移位寄存器中,CLK最高频率可达10MHz,在输入时钟的每个上升沿均有一位数据由DIN端移入到内部寄存器中;LOAD用来装载数据,在LOAD 的上升沿,16位串行数据被锁存到数据或控制寄存器中,LOAD必须在第16个时钟上升沿的同时或之后、在下一个时钟上升沿之前变高, 否则数据将被丢失。

每组数据为16 位二进制数据包,其格式如表1所示。

其中D15~D12位不用,D11~D8位为内部5个控制寄存器和8个LED 显示数据寄存器的地址,D7~D0位为5个控制寄存器和8个LED数码管待显示的数据,因为控制寄存器与显示数据寄存器独立编址,所以可以通过程序对每个寄存器进行操作。

一般情况下,程序先送控制命令,后向显示寄存器送数据,每16 位为一组,从高位地址字节最高位开始送,直到低位数据字节最后一位。

MAX7219内部有14个可寻址的控制字寄存器,各

寄存器的功能及地址如图2.14所示。

图2-3-1

图2.14串行数据格式

其中,地址×0H 为空操作寄存器,允许数据从输入到输出直接通过,可用于设备串接。

地址×1H~×8H为显示RAM区,分别对应DIG0~DIG7引脚的8 位LED显示数据。

地址×9H为译码模式寄存器,其8 位二进制数分别控制着8个LED显示器的译码模式,逻辑高电平时选择硬件译码(BCD - B码译码),译码器选择数据寄存器中的低4位(D3~D0)进行BCD- B码译码,×0H~×9H对应BCD码字符0~9,而×AH~×FH分别对应B码字符-、E、H、L、P及消隐,D4~D6无效,D7单独控制小数点;译码模式寄存器为逻辑低电平时选择软件译码,数据D6~D0分别对应LED显示器的A~G段,D7对应小数点DP。

地址×AH为显示亮度寄存器,通过对该寄存器的D0~D3位写入不同的数值可实现对LED显示亮度的控制,从00H到0FH共16级可调。

地址×BH为扫描界限寄存器,其D0~D3位数值设定为00H~07H,表示显示器动态扫描个数为1~8。

地址×CH为停机寄存器,当其D0位为0时,MAX7219处于停机状态,扫描振荡器停振,所有显示器消隐,寄存器数据保持不变;当D0为1时,正常工作。

地址×FH为显示测试寄存器,当其D0位为0时,正常工作;当D0为1时处于测试状态,全部LED显示器的所有字段都以最大亮度接通显示。