清华大学 数字大规模集成电路 麦宋平 课件L03_互连线_50506280

清华大学微电子系工硕课题介绍

课题介绍微电子与纳电子学系2013级工程硕士双选专用清华大学微电子与纳电子学系2013年12月有招生需求导师名单-------------------------------------------------------白国强(设计室)蔡坚、王谦(器件室)陈虹(设计室)陈炜(器件室)池保勇(设计室)邓宁(器件室)方华军(器件室)付军(集成室)姜汉钧(设计室)李福乐(设计室)李树国(设计室)李翔宇(设计室)李宇根(设计室)李兆麟(信研院)梁仁荣(集成室)刘雷波(CAD室)刘振宇(信研院)麦宋平(深研院)潘立阳(集成室)钱鹤(CAD室)任天令、杨轶(器件室)王敬(集成室)王晓红(器件室)王燕(CAD室)王喆垚(器件室)王志华、王自强(设计室)魏少军(CAD室)乌力吉(设计室)吴华强(工艺平台)伍冬(集成室)伍晓明(工艺平台)谢丹(器件室)谢翔(设计室)许军(集成室)叶佐昌(CAD室)尹首一(CAD室)岳瑞峰(器件室)张春(设计室)张进宇(CAD室)张雷(CAD室)刘泽文(器件室)何虎(设计室)北京朗波芯微技术有限公司课题介绍白国强一、招生老师联系信息E-mail: baigq@电话:62794391(O),136********办公室:主楼9区104二、招生人数:2-3名三、课题介绍课题一:(1)课题名称:面向低资源移动终端应用的新型公钥密码算法的集成电路实现技术研究。

(2)课题来源:国家自然科学基金重点项目“面向低资源移动终端的高效新型公钥密码芯片的理论与关键技术研究”。

(3)课题简介:受移动终端(如手机)硬件资源十分有限的限制,现有公钥密码算法,包括RSA算法和ECC算法很难直接应用于移动终端。

为解决这一问题,近年来多变量公钥密码学受到广泛关注,成为研究热点之一。

本课题研究内容是“面向低资源移动终端的高效新型公钥密码芯片的理论与关键技术研究”项目中的一部分内容,将以集成电路方式设计、实现基于多变量的新型公钥密码芯片。

超大规模集成电路技术基础课件

Part

03

超大规模集成电路制造工艺

制造流程

制造流程概述

超大规模集成电路的制造流程包 括晶圆制备、外延层生长、光刻 、刻蚀、离子注入、化学机械抛

光、检测与封装等步骤。

晶圆制备

晶圆制备是超大规模集成电路制造 的第一步,涉及到单晶硅锭的切割 和研磨,以获得所需厚度的晶圆。

外延层生长

外延层生长是指在单晶衬底上通过 化学气相沉积等方法生长出与衬底 晶体结构相同或相似的单晶层。

解决方案3

加强环保监管和提高环保意识:通过加强环保监管和提 高环保意识,推动超大规模集成电路制造行业的可持续 发展。

Part

04

超大规模集成电路封装与测试

封装技术

芯片封装

将集成电路芯片封装在管 壳内,以保护芯片免受环 境影响和机械损伤。

封装材料

常用的封装材料包括陶瓷 、金属和塑料等,每种材 料都有其独特的优点和适 用范围。

制造设备

超大规模集成电路制造中需要使用到各种复杂的设备和工具,如光刻机、刻蚀机 、离子注入机、化学机械抛光机等。

制造中的挑战与解决方案

挑战1

高精度制造技术的挑战:随着集成电路规模的不断缩小 ,制造精度和工艺控制的要求也越来越高,需要不断改 进制造工艺和研发新的制造技术。

挑战2

制造成本的不断增加:随着技术不断进步,超大规模集 成电路的制造成本也在不断增加,需要寻求更经济、高 效的制造方法和工艺。

封装形式

根据集成电路的类型和应 用需求,有多种封装形式 可供选择,如DIP、SOP 、QFP等。

测试方法与设备

测试方法

包括功能测试、性能测试、可靠 性测试等,以确保集成电路的性

能和质量。

测试设备

数电新5章大规模数字集成电路优秀课件

二进制码

B3 B2 B1 B0 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111

集成电子技术基础教程

常用大规模数字集成电路

半导体存储器 微处理器 大规模可编程逻辑器件 大规模专用数字集成电路 (ASIC)

数电新5章大规模数字集成电路优

秀课件

1

集成电子技术基础教程

2.5.1随机存取存储器(RAM)

存储大量二进制信息的器件

❖软磁盘 ❖硬磁盘 ❖磁带机 ❖光盘 ❖半导体存储器

列地址译码器

An-1

行

An-2

地 址

译

码

A0

器

…… …… ……

…… …… I/O及读写控制

数据输入/输出 片选

I/O控制

存储体

j列 i行

存储单元

存储单元(1位) j列

i行

存储单元(多位,4位)

数电新5章大规模数字集成电路优

秀课件

5

集成电子技术基础教程

存储体或RAM的容量

❖存储单元的个数*每个存储单元中数据的位数

❖例如,一个10位地址的RAM,共有210个存储单元,若 每个存储单元存放一位二进制信息,则该RAM的容量就 是210(字)×1(位)=1024字位,通常称1K字位。

I/O缓冲

❖I/O缓冲起数据锁存作用,一般采用三态输出结构。 因此,它可与外面的数据总线相连接,方便实现信息 交换和传递

数电新5章大规模数字集成电路优

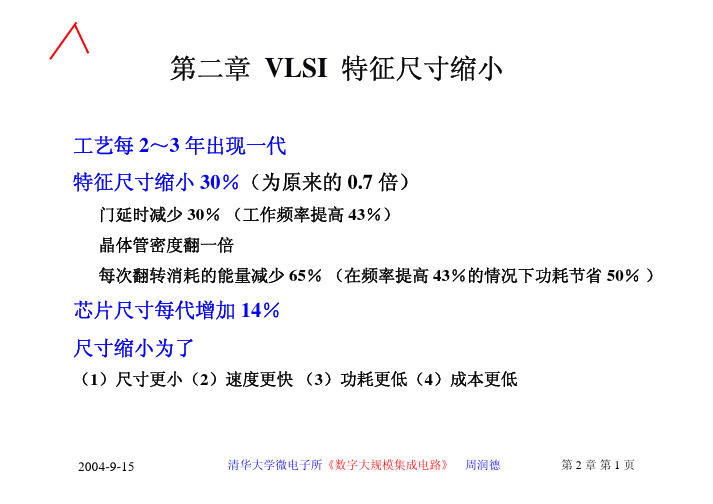

清华大学数字大规模集成电路02-VLSI特征尺寸缩小

每芯片上元件数的增长趋势t p decreases by 13%/year 50% every 5 years!工艺特征尺寸缩小(3)门延时的减小趋势第一节器件的尺寸缩小W, L 缩小:VLSI 技术的基础恒场律(全比例缩小):理想模型,尺寸和电压按同一比例缩小恒压律至今仍是最普遍的模型,仅尺寸缩小,电压保存不变一般化对今天最实用,尺寸和电压按不同比例缩小(一)恒场律(CE 律)(1)原理:1.所有尺寸(纵,横,垂直)均÷S2.器件的(电源)电压÷S3.衬底浓度×S延时(ns )沟道长度MOS 沟道长度(um )电源与阈值电压(V )栅氧厚度(n m )栅氧电源阈值降低电源电压与阈值电压器件特征尺寸缩小(长沟道器件)器件特征尺寸缩小(速度饱和器件)( 3 ) CE 律的优点与缺点:优点:1. 集成密度提高了倍2. 电路优值减小了倍未改善: 功率密度未改善问题: 1. 电流密度增加倍2.小使抗干扰差, 次开启漏电流增加3. 电源电压标准改变带来不便4. 源漏耗尽层宽度不按比例缩小S 2S 3S V TH(二) 恒压律:( 1 ) 原理:V DD1. 保持常数2. 所有尺寸( , , )W L t OX S÷S23. 衬底浓度提高倍( 3 ) 恒压律的优点与缺点:问题: 1. 电流密度增加倍2. 功耗增加倍3. 功率密度增加倍4. 沟道内电场增加倍5. 衬底浓度的增加使PN 结寄生电容增加, 速度下降S 3S S 3S S 2S 优点: 1. 电源电压不变2. 集成密度提高倍3. 电路优值减小倍( 2 ) 一般化尺寸缩小(电源电压不随尺寸缩小比例降低)时的限制因素:1。

受限于长期使用的可靠性2。

受限于载流子的极限速度3。

受限于功耗(1)功耗和功率密度(2)漏电(3)可靠性(击穿、热电子)(4)工艺偏差(5)成本(6)集成度、速度、功耗之间的综合考虑什么原因会使尺寸缩小规律不再成立?何时这些规律不再成立?尺寸缩小的步伐是否会逐渐减慢?第二节互连线的尺寸缩小互连线对性能与功耗的影响越来越大互连线的电阻互连线的电容互连线长度的统计分布连线分布密度连线长度第三节面向高性能和低功耗的CMOS 器件尺寸缩小(一)根据器件尺寸,在“性能”和“可靠性”之间折中选择电源电压。

《集成电路》课件

从二维芯片堆叠到三维集成,通过垂直连接多个芯片,实现更高效 的电路互联。

市场发展趋势

物联网与5G技术的推动

随着物联网和5G通信技术的普及,集成电路市 场将迎来爆发式增长。

汽车电子的崛起

汽车智能化趋势下,汽车电子市场将成为集成 电路的重要应用领域。

人工智能与云计算的驱动

人工智能和云计算的发展将推动高性能Fra bibliotek成电路的需求增长。

随着物联网、5G、汽车电子、人工 智能等领域的快速发展,集成电路行 业面临巨大的市场机遇。

THANKS

感谢观看

《集成电路》课件

目录

• 集成电路概述 • 集成电路的制造工艺 • 集成电路的分类与特点 • 集成电路的设计与仿真 • 集成电路的可靠性分析 • 集成电路的发展趋势与挑战

01

集成电路概述

集成电路的定义

集成电路是将多个电子元件集成在一块衬底上,完成一定的电路或系统功能的微型电子部件 。

它采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起 ,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需 电路功能的微型结构。

可靠性评估

根据测试数据,评估集成 电路的可靠性等级和性能 指标。

提高可靠性的措施

优化设计

在设计阶段充分考虑环境因素和实际 使用需求,提高集成电路的鲁棒性。

封装保护

采用适当的封装材料和结构,降低环 境因素对集成电路的影响。

材料选择

选用高质量的原材料和先进的制程技 术,以提高集成电路的性能和稳定性 。

Synopsys

提供逻辑综合、物理综合 、布局布线等IC设计工具 。

Mentor Graphics

清华大学《数字集成电路设计》周润德 第1章(课件)绪论

2004-9-15

清华大学微电子所《数字大规模集成电路》 周润德

第1章第3页

评分规则(Grading Policy)

(1)作业: 20%

第 4 周起,每周一次,一周完成,上课时交,迟交无效

(2)期中考试:20%

100

P6 Pentium ® proc

10

8086 286

486

386

8085

1

8080

8008

4004

0.1 1971

1974

1978 1985 年

1992

最先进微处理器的功耗持续增长

2000

资料来源: Intel

2004-9-15

清华大学微电子所《数字大规模集成电路》 周润德

第 1 章 第 21 页

2004-9-15

清华大学微电子所《数字大规模集成电路》 周润德

第 1 章 第 17 页

微处理器单个芯片尺寸的增长趋势

100

单个芯片尺寸 (mm)

P6

10

486 Pentium ® proc 386

8080

286 8086

8085

8008

4004

资料来源: Intel

1 1970

1980

1990 年

每1.96年翻一倍!

Pentium® III

Pentium® II

Pentium® Pro

Pentium® i486

i386

80286

10

1 1975

8086

1980

1985 1990

1995

2000

资料来源: Intel

【PPT】超大规模集成电路互连技术(VLSIInterconnects)

看完有什么感想? 请留言参与讨论! 转自:Bar-Ilan University 如侵权请联系:litho_world@

集成电路互连技术就是将同一芯片内各个独立的元器件通过一定的方式连接成具有一定功能的电路模块的技术

【 PPT】超大规模集成电路互连技术( VLSIInterconnects)

编者按:集成电路互连技术就是将同一芯片内各个独立的元器件通过一定的方式,连接成具有一定功能的电路模块的技术。对 于互连金属材料的要求主要包括:具有较小的电阻率、易于沉积和刻蚀以及具有良好的抗电迁移特性。早期(0.18µm之前) 互连技术采用Al材料,之后逐渐采用பைடு நூலகம்u材料。

集成电路互连总线ICppt正式完整版

串行的8位双向数据传输位速率在标准模式下可达 100kbps,快速模式下可达400kbps,高速模式下可达 3.4Mbps

连接到相同总线的IC数量只受到总线最大电容(400pf) 的限制。但如果在总线中加上82B715总线远程驱动器可 以把总线电容限制扩展十倍,传输距离可增加到15m

➢ I2C总线的典型电路 下图给出一个由MCU作为主机,通过I2C总线带3个从

机的单主机I2C总线系统。这是最常用、最典型的I2C总线 连接方式

I2C总线的典型连接

1.3 I2C总线数据通信协议概要

➢ I2C总线上数据的有效性 I2C总线以串行方式传输数据,从数据字节的最高位开

始传送,每个数位在SCL上都有一个时钟脉冲相对应。在一 个时钟周期内,当时钟线高电平时,数据线上必须保持稳定 的逻辑电平状态,高电平为数据1,低电平为数据0。当时钟 信号为低电平时,才允许数据线上的电平状态变化

个开始信号

图1:开始、重新开始和停止信号

应答信号(A):接收数据的IC在接收到8位数据后,向发送数据的IC 发出的特定的低电平脉冲。每一个数据字节后面都要跟一位应答信号, 表示已收到数据

I2C总线的应答信号

➢ I2C总线上数据传输格式

一般情况下,一个标准的I2C通信由四部分组成:开始信号、从机地址 传输、数据传输和结束信号。I2C总线上传送的每一个字节均为8位,首 先发送的数据位为最高位,每传送一个字节后都必须跟随一个应答位, 每次通信的数据字节数是没有限制的;在全部数据传送结束后,由主机 发送停止信号,结束通信

I2C总线上数据的有效性

➢ I2C总线上的信号类型

编程时应以通信的开可靠始性为信原号则,(选择S合TA适R的TS)DA:保持如时间下来(确定图ICR1值)。 当SCL为高电平时,SDA由高电 I主2C机总(线主上控的器信)号:类平在型I2向C总低线中电,平提供跳时钟变信,号,产对总生线开时序始进行信控号制的。器件当总线空闲的时候(例如没有 如面果举2例个说或明者I22C个总以线主上波主动特机率试设和图S备在DA同在保一持时使时刻间用控计制总算总方线线法,,则时即钟同SD步A程和序使S用CL在都每个处主设于备高中集电成的平硬)件定,时器主来机确定通总线过时发钟 如果两者相同,则送该器开件认始为信被主号控器(寻S址T,A并R发T送)应建答信立号,通被信控器根据数据方向位(R/W)确定自身是作为发送器还是接收器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

22

讲课进度

一、引言 、引言 二、互连线的电容效应 线的 容效应 三、互连线的电阻效应 四、互连线模型 五、综述 六 总结 六、总结

23

三、互连线的电阻效应:电阻率和薄层电阻

互连线电阻的模型

均匀厚平板导电材料电阻

电流 电流 W L W`

常用导体的电阻率

L H W 矩形导体的电阻:

L`

薄层电阻(sheet resistance)R□(对于 给定工艺 H 通常是一个常数): 给定工艺,

Level1 SiO2

连线的水平尺寸与垂直尺寸不按相同比例缩小,连线间距 D 减小,连线厚度 H 基本维持不变,导致线间寄生电容增大 基本维持不变,导致线间寄生电容增大。

18

二、互连线的电容效应:线间电容

W/H

19

二、互连线的电容效应:线间电容

20

二、互连线的电容效应:对地和线间电容的比较

例:L=10cm,W=1um 的Al1线,求其对地电容和线间电容。

16

二、互连线的电容效应:互连线电容值 (0.25 m CMOS)

场氧 多晶 AL1 AL2 AL3 AL4 AL5 88 54 30 40 13 25 8.9 18 6.5 14 5.2 12 41 47 15 27 9.4 19 6.8 15 5.4 12 57 54 17 29 10 20 7.0 15 5.4 12 36 45 15 27 8.9 18 6.6 14

边缘场 H W-H/2

Cwire C p p C ffringe g

W H / 2 di

t di

边缘场电容模型

2 di log g2t di / H 1

15

二、互连线的电容效应:互连线电容与W/H的关系

W < tdi时,总电容会趋于1 pF/cm

W/H 较大时,总电容接近 平行板电容模型; W/H 较小时(W/H < 1.5),边缘电容占总电容的 主要部分。

9

讲课进度

一、引言 、引言 二、互连线的电容效应 线的 容效应 三、互连线的电阻效应 四、互连线模型 五、综述 六 总结 六、总结

10

二、互连线的电容效应:负载电容的组成

负载电容 CL 组成分析

VDD M2 Vin Cgd12 Cdb2 Vout Cdb1 Cw Cg3 M3 扇出 Cg4 4 VDD M4 Vout2

38

四、互连线模型:集总 RC模型(Elmore延时)

定义:

共享路径电阻 Rik:根节点 r 至节点 k 和节点i这两条路径共享的电阻

如 Ri4=R1+R3,Ri2=R1 如:

39

四、互连线模型:集总 RC模型(Elmore延时)

每个节点初始被放电,时间 t = 0, 在节点 r 加 加一个阶跃输入 个阶跃输入,节点 节点 i 的 Elmore延时:

M1 驱动器 动 简化模型 简

连线电容

CL

11

二、互连线的电容效应:平行板电容模型

平行板电容模型(W >> tox)

C

L W H tox SiO2 substrate 电力线

ox

tox

WL

按比例缩小:

W、tox1/S L 1/SL

S C , wire

1/ S 1/ S L 1/ S L 1/ S

Vo ut cwi re Driver

Vin

R driver

V out

C lumped

Clumped=LCwire

Cwire:单位长度导线电容

驱动器(Driver):电压源+内阻

36

四、互连线模型:集总 RC模型(Elmore延时)

集总电容模型:不考虑电阻,导线看作等势体 集总 RC 模型:考虑导线电阻 导线分段,每段导线的导线电阻集总成 导线分段,每段导线的导线电阻集总成一个电阻 个电阻 R,电容 集总成一个电容 C 电路分析: 集总电容模型:单电阻单电容,用一个常微分方程描述 集总 RC 模型:多电阻多电容,用一组常微分方程 用SPICE模拟 Elmore延时公式计算

红色:上层 蓝色 下层 蓝色:下层 无阴影:平板电容 aF/um2 有阴影:边缘电容 有阴影 边缘电容 aF/um / 计算时需考虑2个边缘

有源区

多晶

AL1

AL2

AL3

AL4

AL5

41 49 15 27 9.1 19

35 45 14 27 38 52

17

二、互连线的电容效应:线间电容

线间电容

Level2

H>W

Intel 0.18微米工艺互连线

14

二、互连线的电容效应:边缘电容

边缘电容:连线侧壁与衬底间的电容

H 减小引起连线电阻增加,因此H 以一个小于 S(S 为 W 的缩放因子) 的因子减小 使得 W/H 变小,甚至 的因子减小,使得 变小 甚至 W/H < 1。此时,需要考虑边缘电容。 边缘场电容模型分解为两部分: (1)平行板电容 (2)边缘电容

37

四、互连线模型:集总 RC模型(Elmore延时)

电阻电容网络(RC树)

特点: 一个输入节点 个输入节点 r 电容都在节点和地之间 不存在电阻回路(树结构)

定义:

路径电阻 路径电 Rii :源节点 源节点 r 与电路的任何节点 i 之间存在惟一的电阻 之间存在惟 的电 路径,路径的总电阻称为路径电阻,如 R44=R1+R3+R4

1)多晶、扩散、阱的电阻率随着掺杂浓度和温度而变化 2)多晶,扩散区有较高的电阻,一般不用作互连线 3)多晶可以用作Latch或者Register的内部连线

26

三、互连线的电阻效应:工艺上减小电阻的办法

选择性的按比例缩小

水平尺寸(W、L)缩小,垂直尺寸(H)基本恒定 工艺变复杂,寄生电容增大

12

二、互连线的电容效应:边缘电容

随着尺寸缩小: 为保持电阻比较小,需要互连线 为保持电阻比较小 需要互连线 的截面积比较大,即(W × H) 比较大; 为获得较密布线,需W比较小。 随着工艺尺寸的缩小 随着工艺尺寸的缩小, W/H 在逐步下降

Intel 0.25微米工艺互连线

13

二、互连线的电容效应:边缘电容

中层的多晶硅连线

下层的扩散区连线

5

一、引言:互连线的种类

6

一、引言:互连线及其模型

此处的互连线都位于同一层

发送器

接收器

电路图

物理

7

一、引言:互连线的延时和耦合

考虑各种寄生参数的模型

仅考虑电容的模型

8

一、引言:互连寄生效应对电路的影响

寄生效应的类型: 电容性的寄生效应 电阻性的寄生效应 电感性的寄生效应 寄生效应的影响: 引入噪声,可靠性降低 影响性能:延时增加 功耗增加

总的对地电容(11pF)和线间电际设计当中如何计算电容 一般制造商会提供每层的面电容和周边电容。 般制造商会提供每层的面电容和周边电容

实际设计时,可以查表或查图。

考虑性能时,导线电容的计算:

考虑延迟或动态功耗时, 一般用最坏情况 考虑延迟或动态功耗时 般用最坏情况 (最大宽度 W ,最薄介质); 考虑竞争情况时用最小宽度W 及最厚介质; 要用制造后的实际尺寸。

34

四、互连线模型

理想导线 集总RC模型 分布rc线(Distributed rc-Line) 传输线

理想导线是没有电阻、电容或电感的简单 连接 是一个等势体。 连接,是 个等势体。

集总模型(Lumped Model)

35

四、互连线模型:集总模型

一种寄生效应起主要作用,或寄生元件间的相互作用很小,可以把各个 分量集总成单个电路元件进行分析 寄生效应可以用常微分方程描述 分量集总成单个电路元件进行分析。寄生效应可以用常微分方程描述。 导线电阻很小,开关频率较低,只考虑电容,并将分布电容集总为 单个电容 这种集总模型称为集总电容模型 单个电容。这种集总模型称为集总电容模型。

一阶时间常数:源节点 阶时间常数:源节点 r 与节点 i 之间延时的简单近似

Di R1C1 R1C 2 R1 R3 C 3 R1 R3 C 4 R1 R3 Ri C i

40

四、互连线模型: 集总RC 链(Elmore延时)

3

一、引言:互连线的重要性

随着工艺的进步,

器件尺寸缩小,器件本身的延时按比例减小。互连线 在尺寸缩小时其寄生效应同晶体管等有源器件并不相同。 事实上,随着芯片规模的增大(虽然工艺线宽在缩小, 但是芯片的整体尺寸在增大),全局互连线的平均长度 也在增大 从而导致了相应寄生效应的增大 也在增大,从而导致了相应寄生效应的增大; 电路规模增大,连线越来越复杂; ……

平行板电容: 平行板电容 边缘电容: 总对地电容 总对地电容: 线间电容:

(0.1106 m 2 ) 30aF / m 2 3 pF 2 (0.1106 m) 40aF / m 8 pF 11 pF F

Cgnd Cadj

(0.1106 m 2 ) 95aF / m 9.5 pF

数字大规模集成电路 —— 第3节 互连线 The Wire (第 4 章)

麦宋平 清华大学深圳研究生院 Mai.songping@ 2012年秋季学期

思考题

互连线对集成电路有什么影响?

2

本章提纲

一 引言 一、引言 二、互连线的电容效应 连线的电容效应 三、互连线的电阻效应 四、互连线模型 五、综述 综述 六 总结 六、总结

R

L

HW

R口

H

单位:/□

L R R口 W

24

三、互连线的电阻效应:多晶硅化物栅 MOSFET