lattice烧录线线序1

1126烧录流程

1126烧录流程

1126烧录流程是一个关键的技术流程,在电子行业中非常重要。

本

文将从流程概述、准备工作、烧录操作、验证测试等方面进行详细介绍。

流程概述:

1126烧录流程是指将程序代码烧录到芯片存储器中的一种技术流程,

该流程涉及到多个步骤,包括准备工作、烧录操作、验证测试等。

准备工作:

1.准备好需要烧录的芯片和烧录器设备。

2.确认程序代码的版本和需要烧录的目标地址。

3.打开烧录设备的电源,并将烧录器与电脑连接。

4.下载并安装烧录软件,在软件中选择需要烧录的目标芯片和程序代码。

烧录操作:

1.在烧录软件中设置好相关参数,包括设备连接方式、目标地址等。

2.将烧录器连接好并打开软件,开始进行烧录操作。

3.在烧录过程中,需要耐心等待,直到烧录成功。

验证测试:

1.烧录完成后,进行验证测试,确认程序是否正确烧录到芯片存储器中。

2.进行芯片测试,确认芯片的功能和性能是否符合要求。

3.进行系统测试,确认整个系统的性能和稳定性。

以上就是1126烧录流程的详细介绍,整个流程需要仔细操作,并且在

烧录过程中需要注意防止操作失误或设备故障。

在技术操作困难或不

确定的情况下,最好向相关专业人员咨询或寻求帮助。

Lattice USB下载设置

Lattice USB 下载线的设置方法

分两种情况

一、如果是ispVM System 17.6 以下的版本,请安装光盘中的最新版软件ispVM System 18.1,安装好软件后,连接USB下载器,系统会自动找到并安装USB下载器的驱动,你只需按提示就可以了。

二、如果是ispVM System 17.6以上的版本,没有安装过USB驱动,请按以下步骤进行安装。

1、打开ispVM;

2、按下图所示,装载USB 下载线的驱动程序,在弹出的对话框内点

完成安装;

3、安装完成后,按提示要求重新启动电脑;

4、将下载线的 VCC、TDO、TDI、TMS、GND、TCK与板上相应的管脚接好;

5、将 USB 端接入电脑的 USB 口内;

6、此时,电脑会显示找到USB 设备,显示出:

7、点下一步,会出现:

8、点仍然继续,

9、点完成;

10、按下图所示,进入下载线端口设置界面:

11、点按钮 ,会扫描到USB 下载线,

12、点OK。

13、再点 即可以扫描到器件。

以下以一块EC20 的板子为例:

14、点Scan 后,扫出器件,

15、双击上图的鼠标处,弹出下图列表,选择LFEC20E,

16、在弹出对话框内,

点 [Browse] 指定 JED 文档(XP,CPLD)或Bit 文档(EC/ECP)的路径, 在 [Device Access Option] 中选择下载的方式“JTAG 1532 Mode”, 在 [Operation] 中选择操作的类型“Fast Program”。

17、设置好后,点OK,再点工具栏上的 开始下载。

18、会显示出进度条:

19、成功后始可显示 。

2024年度LatticeispLEVER使用教程

丰富的仿真验证

支持功能仿真和时序仿真,可 对设计进行全面的验证和调试 。

全面的设计输入支持

支持原理图、Verilog/VHDL 硬件描述语言等多种设计输入 方式。

2024/3/23

灵活的布局布线

提供手动和自动布局布线功能 ,支持用户自定义布局和布线 策略。

广泛的IP核库

集成了多种常用的IP核,如计 数器、FIFO、UART等,方便 用户快速构建系统。

2024/3/23

元器件库导入与导出

支持导入和导出元器件库,方便不 同项目之间的共享和复用。

元器件搜索与筛选

提供强大的搜索和筛选功能,可快 速找到所需元器件。

21

06

仿真与验证功能应用

2024/3/23

22

仿真设置与运行

01

创建仿真工程

在LatticeispLEVER中,首先需 要创建一个新的仿真工程,指

定工程名称和存储路径。

02

添加设计文件

将待仿真的设计文件(如 VHDL、Verilog代码文件)添

加到工程中。

03

配置仿真参数

根据设计需求,配置仿真参数 ,如仿真时间、输入激励等。

04

运行仿真

设置好仿真参数后,可以运行 仿真,观察设计的行为和功能

。

2024/3/23

23

波形显示与分析

2024/3/23

2024/3/23

丰富的元器件符号库

提供大量常用的元器件符号,方便用户快速 搭建电路。

原理图自动检查功能

可检查原理图的正确性,如元器件连接是否 正确、导线是否短路等。

19

PCB设计

PCB板层管理

支持多层PCB板设计,可自定义各层属性 和参数。

lattice烧录线线序1

下载线线序说明对于目前的欧型板和主控,信号分配器使用的都是Lattice烧录线,其中欧型板和信号分配器的接口定义是相同的,主控使用的是是8口双排接口,建议制作转换接口即可通用同一根信号线。

主控使用Lattice的程序下载线(以公司目前使用的烧录线为列,如下图)Lattice下载器:VSD-F2L4主控编程口的线序定义:引脚线序说明:引脚序号丝印线色备注1脚VCC红色 3.3V2脚TDO棕色3脚TDI橙色4脚NC黄色空脚5脚NC绿色空脚6脚TMS紫色7脚GND黑色8脚TCK白色或者是以下线序:引脚序号丝印线色备注1脚VCC红色 3.3V2脚TDO黄色3脚TDI紫色4脚NC橙色空脚5脚NC蓝色空脚6脚TMS棕色7脚GND灰色8脚TCK白色Programmer cable Color(Mode1):Leg NO.print Cable Color remarksPin1VCC Red 3.3VPin2TDO BrownPin3TDI OrangePin4NC yellow NGPin5NC Green NGPin6TMS purplePin7GND blackPin8TCK whiteProgrammer cable Color(Mode2):Leg NO.print Cable Color remarksPin1VCC Red 3.3VPin2TDO yellowPin3TDI purplePin4NC orange NGPin5NC Blue NGPin6TMS BrownPin7GND grayPin8TCK white分配器的程序下载接口定义说明(和主控一样,都是使用Lattice程序下载线,但接口的定义线序不同):引脚线序说明:引脚序号丝印线色备注1脚VCC红色 3.3V2脚GND黑色3脚TMS紫色4脚TDO棕色5脚TCK白色6脚TDI橙色对于小的Lattice烧录线,如下图这种,这里只给出线色及其定义,请根据实际应用对应上面的图进行制作:引脚线序说明:引脚序号丝印线色备注1脚VCC黄色 3.3V2脚TDO绿色3脚TDI紫色4脚NC橙色空脚5脚NC蓝色空脚6脚TMS棕色7脚GND灰色8脚TCK白色时钟。

LATTICE的I2C模式下载使用教程说明

LATTICE下载器HW-USBN-2B I2C下载使用说明教程By:翊全EN-WXLATTICE的I 2 C配置模式:要进行对I 2 C Port Devices的操作,首先得是支持I2C的器件。

目前可以支持的器件有:MachXO2/MachXO3/MachXO3D ;Platform Manager II ;L-ASC10 ;CrossLink LIF-MD6000;需要使用lattice的HW-USBN-2B和MTC2 plus才支持I2C配置器件。

I2C (Inter-IC)总线是一种简单的低带宽,短距离协议。

人们常常看到对系统外围设备的访问是间歇的。

在闭环系统中,这也是一个常用的通信解决方案,可实现电路板上最少的走线。

I2C(内部集成的电路)接口也称为两线接口,是最初由Philips开发的一种多主器件串行单端总线。

I2C广泛用于同一块电路板上器件之间的通信。

一.硬件连线LATTICE的I 2 C配置模式用到的信号如下:1.SDA:I 2 C总线数据线2.SCL:I 2 C总线时钟3.GND:连接到目标芯片的接地信号4.VCC(VREF):连接到目标芯片的VCC,提供芯片配置IO的电平参考电压。

注意:I2C总线的信号是漏极开路的,所以默认情况下是,信号线是低电平,需要加上拉电阻,使其默认是高电平。

I2C总线上建议不要挂太多的器件,建议只挂一个芯片,因为需要保证信号质量。

为了能够使用I2C总线进行在线下载(program),I2C_PORT必须要设置为ENABLE。

默认状态在Diamond设计软件中为I2C_PORT设置的设置是将I2C_PORT置于DISABLE状态。

你必须确保将I2C_PORT设置为ENABLE状态,以使I 2 C接口在用户模式下保持使能状态。

支持I2C编程的芯片,如果flash编程过一次,必须擦除程序才能用I2C编程。

且须flash编程以后再擦出,如果擦除次数多了,I2C也将不容易识别。

lattice下载线连接

好消息:本店即将独家推出LATTICE官方下载线2011最新版,产品正在调试中,支持器件更多,,支持工作电压更低,支持器件更多。

在新产品上市前,将原有产品价格调低,以回报新老客户。

6 月27号收到LATTICE官方最新的下载线,外形与原来版本一样,按照惯例,打开一套外壳看看,发现里面的电路改动较大,在增加保护电路的同时,下载部分电路也进行了相应改动,电路进行的调整,器件全部采用最新的低压版本器件,经测试可稳定支持1.5V版本的LATTICE器件,更低电压版本器件由于受调试条件限制,没有测试。

下载线主芯片也进行了升级,速度也市面上的下载线也要快,正在调试中,以期发现更多惊喜功能。

目前,市面上的LATTICE下载线一样,都是采用老版本固件和电路,为了大家早日使用上最新的LATTICE下载开发工具,特对老版本的LATTICE下载线进行促销,108元一套。

真正兼容Lattice全系列FPGA、CPLD的下载线,支持Vista操作系统,已出货三百余条。

超低价格,质量可靠,性能稳定,兼容性好,精美外壳,携带小巧方便,专业的技术水平,直接来自开发工程师的详细解答,可按您的需要定制飞线,可提供发票(但需要支付总额5%的税点),周到的售后服务,详细的使用说明书,最新的开发软件,教会使用为止。

产品规格:1. Lattice原厂设计,确保下载兼容性2. 无需单独安装驱动,直接支持ispLever6.x/7.x/classic版本,ispVM各种版本3. 支持lattice全系列FPGA,如SC/SCM/XP/XP2/EC/ECP2/ECP2M/MachXO系列等4. 支持lattice全系列CPLD, 如1000/2000/4000 系列等5. USB标准B型接口,使用标准USB连接线即可连接PC6. USB供电,无需外部供电支持7. 支持JTAG, internal FLASH,SPI FLASH等编程模式8. 10针排插线一条(可选择8PIN、10PIN单排等)。

LATTICE_非常详细的时序约束(中文教程)

©LATTICE SEMICONDUCTOR CORPORATIONPage 1Achieving Timing ClosureJohn LiAgenda•Timing closure的概念•Timing closure的步骤•采用合适的Coding Style •进行适当的综合约束•管脚锁定•实施Lattice constrains •Map•布局布线•控制place and route •Floorplanning the design©LATTICE SEMICONDUCTOR CORPORATIONPage 2Timing closure的概念•当前FPGA的设计规模越来越大,复杂程度日益增加,同时要求系统的Perfromace也越来越高。

•获得Timing目标越来越困难.•设计者必须采用各种技术提升系统性能以满足设计的Timing要求.©LATTICE SEMICONDUCTOR CORPORATIONPage 3Timing closure procedure• 1.采用合适的coding style • 2.进行适当的综合约束• 3.管脚锁定• 4.实施Lattice constrains • 5.Map• 5.布局布线•7.控制place and route •8.Floorplanning the design©LATTICE SEMICONDUCTOR CORPORATIONPage 4关于提升FPGA系统性能,工程师最容易想到的方法就是通过进行综合约束、布局布线约束、和其他的优化技术提升系统性能,当然这些都是设计过程中所必需的,但所有这些优化方法对于系统性能的提升都是有限的,系统的性能最终还是取决于工程师的设计(coding style),其中同步设计是最重要的一点. 下面讨论一些具体的coding 技术,合理的运用这些coding技术能够尽可能的减小两级寄存器之间的延时从而获得更高的系统速度.-通用的coding style--Hierarchical Coding---Team Based的设计:多个工程师可以同时参与到一个复杂设计中来。

Lattice CPLD程序烧写步骤说明

1:打开烧录软件,初次使用打开后即可连续烧录,后面无需此步骤。

2:将烧录线连接到板子上,切记:在烧录线未连接好之前不可上电烧录线红色线对应板子的电源管脚(丝印标有VCC)

3:板子上电。

4:点击工具栏上自动扫描按键。

初次使用点击即可,后面无需此步骤。

5:双击空白处后弹出窗口选择烧录软件:初次使用点击即可,后面无需此步骤。

如下图6:点击开始烧写

7:烧写成功后会显示PASS,如下图

8:断电

9:拔掉烧写线,换下一台。

切记:必须先断电才能拔掉烧写线

10:下一台开始即可跳过步骤1、4、5.。

Q-WRITER附件烧录器连线图片

1.1Holtek e-writer 连接方式:e-writer 接线图接线图中X 可以是A 或是B ,参考表-2,表-31.2Holtek HT -writer ,HT -MSR writer ,HT -M1writer 三个烧录器的接线相同,如下:全图接线图中X 可以是A 或是B ,参考表-2,表-3Pin2VssPin1VDDPin2VssPin4BIN2_XPin5BIN3_XPin9START_X此处跳线需要短接1.3e-writer plus以上为e-writer plus 连接线Pin1红色VDD Pin2绿色VSS Pin3蓝色NCPin4黑色Bin2OK 信号Pin5红色Bin3NG 信号Pin9绿色Start 信号Writer ID 设置001注意:如果将Pin3(蓝色)信号接到黄色的LED 指示灯上(接法如Pin4,Pin5),则将WriterID 设置为000,且设置BusySignal L OKSignal L NGSignal L ,这样会更稳定。

Pin1VDDPin2Vss Pin9START_X3.0松翰烧录器:对于sonix烧录器使用通用接口的连线和设置:连线如上图:Pin1(红色)3.3V此3.3v由烧录器的5.0V分压得到。

在V5.0与VSS间串三个1K的电阻,与5.0V相连接的1K电阻的另一端接此Pin1如上图Pin2(绿色)接VSSPin3(蓝色)接Busy LED处的470R电阻的一端如上图Pin4(黑色)接OK LED处的470R电阻的一端如上图Pin5(红色)接Fail LED处的470R电阻的一端如上图Pin9(绿色)接Key的一个脚如上图机台设置:WriterID0033.1应广科技PinX 分别指向机台DB9接头的相应针脚(颜色参考3.0所示)设置WriterID =003Pin5NGSignal中颖烧录器连接Pin9START_XPin4BIN2_XPin3BIN1_XPin1VDD Pin2Vss6.义隆烧录器Pin2VSSPin3BIN1_X连接线如下:接线图中X 可以是A 或是B ,参考表-2,表-3,以及表-4(拨码开关)机台设置:WriterID 006Pin1VDD Pin2VssPin3BIN1_XPin9START_X8.飞林烧录器(Feeling)连接如下图接线图中X 可以是A 或是B ,参考表-2,表-3,以及表-4(拨码开关)12.麦肯烧录器MDT writerPin1VDDPin2VssPin3BIN1_XPin4BIN2_XPin9START_X设置WrierID 为010即可(测试通过)Pin4OK 实际是接在了Fail 的指示灯上,由于OK 指示灯在烧录过程中一直是亮着的,所以将Fail 指示灯连接到OK 信号上。

烧录及测试指引D1-LA

1.0目的作为烧录和测试工位的作业指引.2.0适用范围适用于此型号的烧录及测试作业工位.3.0 参考文件/ 仪器设备配置3.1 参考文件Instructions to Test Linear 1 PCBA’sL1 Fixture Test Procedure-Additional Instructions3.2 仪器设备配置客供测试架,PCBA 固定架,客供烧录器及连接线,直流电源, 110VAC电源4.0 测试设备连接图1 图21. 烧录测试程序L1_G_TEST1.HEX 连接图 1. 烧录测试程序L1_G_19 07_17_08.HEX连接图(使用L1G programmer and L1G cable) (使用L1G 19 programmer and L1G 19 cable)110VAC(电缆线插头)注:在不进行烧录的时候,必需拔掉烧录器端的烧录插头,以免损耗烧录器的电池,电池欠压时需更换电池)5.0 测试设备参数设定DC电源 15V. 交流电源110V6.0 测试步聚6.1烧录测试程序L1_G_TEST1.HEX6.1.1打开DC 电源, 将输出设置15VDC ,限流1A.6.1.2按测试架连接方法中的图1将测架和PCBA 固定架连接起来.如图3所示将PCBA 放入固定架. 如图4所示将L1G 烧录器与PCBA 插针相连(注意方向)6.1.3 打开待测机15VDC 和110VAC 供电,确认测架上的指示灯点亮(图5)6.1.4 按压烧录器上的红色开关, 对待测机开始烧录。

烧录完成功后, 待测机的数码管上会显示P ,烧录器的绿色指 示灯闪烁4次。

若烧录后数码管不显示P 及烧录器的红灯闪烁, 则表示烧录失败,则待测机判定为不良,送修理维修。

(图 6)图3.图4说明:使用L1G 连接线 连接L1G 烧录器(SN:096966) 注:烧录器接通的一瞬间,绿色指示灯闪烁一次 图5.接通15VDC 电源后测架上的指示灯点亮6.2 测试6.2.1 关闭15VDC 和110VAC 电源, 拔掉烧录器的插头(包括待测机端的插头和烧录器端的插头)6.2.2 打开15VDC 和110VAC 电源, 被测机的数码管依次显示P ,4,8.8.,此时灯泡点亮,D10,D11,D12同时点亮(图7,8)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

下载线线序说明

对于目前的欧型板和主控,信号分配器使用的都是Lattice烧录线,其中欧型板和信号分配器的接口定义是相同的,主控使用的是是8口双排接口,建议制作转换接口即可通用同一根信号线。

主控使用Lattice的程序下载线(以公司目前使用的烧录线为列,如下图)

Lattice下载器:

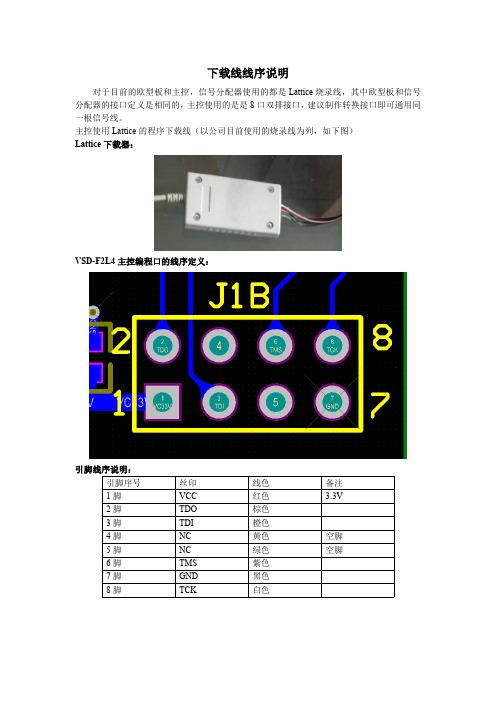

VSD-F2L4主控编程口的线序定义:

引脚线序说明:

引脚序号丝印线色备注

1脚VCC红色 3.3V

2脚TDO棕色

3脚TDI橙色

4脚NC黄色空脚

5脚NC绿色空脚

6脚TMS紫色

7脚GND黑色

8脚TCK白色

或者是以下线序:

引脚序号丝印线色备注

1脚VCC红色 3.3V

2脚TDO黄色

3脚TDI紫色

4脚NC橙色空脚

5脚NC蓝色空脚

6脚TMS棕色

7脚GND灰色

8脚TCK白色

Programmer cable Color(Mode1):

Leg NO.print Cable Color remarks

Pin1VCC Red 3.3V

Pin2TDO Brown

Pin3TDI Orange

Pin4NC yellow NG

Pin5NC Green NG

Pin6TMS purple

Pin7GND black

Pin8TCK white

Programmer cable Color(Mode2):

Leg NO.print Cable Color remarks

Pin1VCC Red 3.3V

Pin2TDO yellow

Pin3TDI purple

Pin4NC orange NG

Pin5NC Blue NG

Pin6TMS Brown

Pin7GND gray

Pin8TCK white

分配器的程序下载接口定义说明(和主控一样,都是使用Lattice程序下载线,但接口的定义线序不同):

引脚线序说明:

引脚序号丝印线色备注

1脚VCC红色 3.3V

2脚GND黑色

3脚TMS紫色

4脚TDO棕色

5脚TCK白色

6脚TDI橙色

对于小的Lattice烧录线,如下图这种,这里只给出线色及其定义,请根据实际应用对应上面的图进行制作:

引脚线序说明:

引脚序号丝印线色备注

1脚VCC黄色 3.3V

2脚TDO绿色

3脚TDI紫色

4脚NC橙色空脚

5脚NC蓝色空脚

6脚TMS棕色

7脚GND灰色

8脚TCK白色时钟。