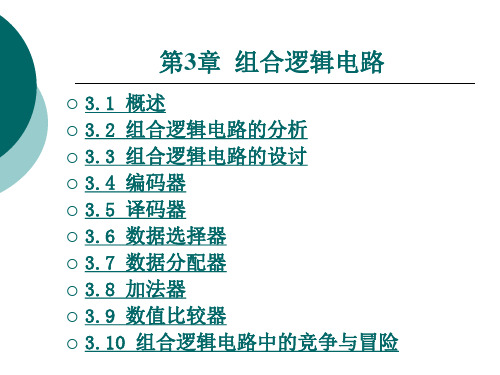

常用组合逻辑集成电路介绍

合集下载

范文4.3常用组合逻辑电路(3线—8线译码器138)

内容回忆

• 编码: 将输入的每个高/低电平信号变成一个对应的二 进制代码

最新.

1

选通输入端 S'

I '7

I '6

I '5

状态信号 I '4

输入端

I '3

〔低电平有效〕 I '2

I '1

I '0

YS'

YE' X

最新.

74HC148

Y ' S 选通输出端

Y '2 代码输出端 Y '1 Y '0 〔低电平有效〕 Y'EX 扩展端

最新.

16

例1:利用74HC138设计一个多输出的组合逻辑电 路,输出逻辑函数式为:

Z1 AC ' A'BC AB'C Z2 BC A'B'C Z3 A'B AB'C Z4 A'BC ' B'C ' ABC

最新.

17

解:先将要输出的逻辑函数化成最小项之和的形式, 即

Z1ACABCABCm3m4m5m6 Z2 BCABCm1m3m7 Z3 ABABCm2m3m5 Z4 ABCBCABC m0m2m4m7

S2'S3'0时

Yi'(S1mi)'

最新.

12

• 利用附加控制端进展扩展 • 例:用74HC138〔3线—8线译码器〕 • 构成 4线—16线译码器

最新.

13

D3=0

Zi' mi'

最新.

D3=1

14

二、二-十进制译码器 二-十进制译码器的逻辑功能是将输入的BCD代 码译成10个高、低电平输出信号。

• 编码: 将输入的每个高/低电平信号变成一个对应的二 进制代码

最新.

1

选通输入端 S'

I '7

I '6

I '5

状态信号 I '4

输入端

I '3

〔低电平有效〕 I '2

I '1

I '0

YS'

YE' X

最新.

74HC148

Y ' S 选通输出端

Y '2 代码输出端 Y '1 Y '0 〔低电平有效〕 Y'EX 扩展端

最新.

16

例1:利用74HC138设计一个多输出的组合逻辑电 路,输出逻辑函数式为:

Z1 AC ' A'BC AB'C Z2 BC A'B'C Z3 A'B AB'C Z4 A'BC ' B'C ' ABC

最新.

17

解:先将要输出的逻辑函数化成最小项之和的形式, 即

Z1ACABCABCm3m4m5m6 Z2 BCABCm1m3m7 Z3 ABABCm2m3m5 Z4 ABCBCABC m0m2m4m7

S2'S3'0时

Yi'(S1mi)'

最新.

12

• 利用附加控制端进展扩展 • 例:用74HC138〔3线—8线译码器〕 • 构成 4线—16线译码器

最新.

13

D3=0

Zi' mi'

最新.

D3=1

14

二、二-十进制译码器 二-十进制译码器的逻辑功能是将输入的BCD代 码译成10个高、低电平输出信号。

4.3常用组合逻辑电路(3线—8线译码器 138)

用二极管与门阵列组成的3 线-8线译码器

Y0 A2' A1' A0' m0 Y1 A2' A1' A0 m1 Y2 A2' A1 A0' m2 ... Y7 A2 A1 A0 m7

附加 控制端

集成译码器实例:74HC138

低电平 输出

S S1S 2S3 S1(S 2'S3')'

• 利用附加控制端进行扩展 例:用74HC138(3线—8线译码器) 构成 4线—16线译码器

D3=0

Z

' i

mi'

D3=1

二、二-十进制译码器 二-十进制译码器的逻辑功能是将输入的BCD代 码译成10个高、低电平输出信号。 如74HC42

Yi mi (i 0 ~ 9)

四、 用译码器设计组合逻辑电路

集成译码器实例:74HC138

附加 控制端

Yi' ( S mi )'

S 1时 Yi' mi'

低电平 输出

S 0时,输出为全1。

74HC138的功能表:

输

入

输

出

S1

S

' 2

S3'

A2

A1

A0

Y7' Y6' Y5' Y4' Y3' Y2' Y1' Y0'

0

X XXX1 1 1 1 1 1 1 1

将要实现的输出逻辑函数的最小项之和的形式两次 取反,即

Z1 ((m3 m4 m5 m6 )) (m3 m4 m5 m6 ) Z2 ((m1 m3 m7 )) (m1 m3 m7 ) Z3 ((m2 m3 m5 )) (m2 m3 m5 ) Z4 ((m0 m2 m4 m7 )) (m0 m2 m4 m7 )

组合逻辑电路

Y2 A2 A1 A0 m2 Y3 A2 A1A0 m3

Y6 A2 A1A0 m6 Y7 A2 A1A0 m7

3. 5. 2二进制译码器的应用

一、用译码器实现组合逻辑电路

因为n个输入变量的二进制泽码器的输出为其对应的2n个最小 项(或最小项的反),而任一逻辑函数均可表示为最小项表达 式(即标准与或式)的形式,故利用二进制泽码器和门电路可 实现单输出或多输出组合逻辑电路的设计。使用方法为:当泽 码器的输出为低电平有效时,选用与非门;当泽码器的输出为 高电平有效时,选用或门。

(4) 分析电路的逻辑功能。由真值表可以看出:当A, B输入状 态相同时,Y=0;当A同时,Y=1。故此电路具有异或门的逻 辑功能,所以该电路是由4B输入状态不个与非门构成的异或 逻辑电路。

上一页 下一页 返回

3.2 组合逻辑电路的分析

「例3.2.2]已知组合逻辑电路如图3.2.2所示,试分析该电路 的逻辑功能。

当输入A3=1时,低位片CT74LS138(1)因A3 =1而禁止泽码, 输出 Y0 ~ Y7 均为高电平1,高位片CT74LS138(2)工作,这时 输入A3A2A1A0 ,在1000~1111之间变化时, Y8 ~ Y15 对应的输 出端输出有效的低电平0。

中,I 7的优先级别最高,I6 次之,其余依此类推,I 0 的级别最 低。

上一页 下一页 返回

3. 4 编码器

也就是说,当 I7 =0时,其余输入信号不沦是0还是1都不起作 用,电路只对 I 7 进行编码,输出 Y2Y1Y0 = 000,此码为反码,其 原码为111,其余类推。可见,这8个输入信号优先级别的高 低次序依次为 I 7、I 6、I 5、I 4、I 3、I 2、I1、I 0

3. 5. 1二进制译码器 将输入二进制代码按其原意转换成对应特定信号输出的逻辑

数字集成电路-组合逻辑门设

g = 5/3

24 24

D 分支努力

IC

分支努力:

b Con path Coff path Con path

25 25

D 多级网络

IC

N

Delay pi gi fi i 1

每级努力:

hi = gifi

路径电气努力: F = Cout/Cin

路径逻辑努力: G = g1g2…gN

11 11

D 互补 CMOS门静态特性

IC

• 高噪声容限: VOH = Vdd,VOL = GND

• 没有静态功耗: 在稳态,上拉和下拉网络互斥,不

存在Vdd到 GND之间的通路。 • 相近的上升、下降沿延时:在适当的尺寸条件下) • 无比逻辑:逻辑功能与器件尺寸无关; • 低输出阻抗:稳态下,总存在一条到Vdd或者GND 的通路; • 高输入阻抗;稳态输入电流几乎为0 • 传播延迟是负载电容和晶体管电阻的函数

0 -0.5

100

200

300

400 A= 10, B=1

57

时间 [ps]

NMOS = 0.5m/0.25 m

PMOS = 0.75m/0.25 m

CL = 100 fF

15 15

D 晶体管尺寸

IC

Rp

Rp

2A

B2

Rn

CL

2B

2 Rn

Cint

A

Rp 4B

4

Rp

Cint

A

Rn 1

A

Rn

CL

B1

确定尺寸,使得延迟近似等于最小尺寸对称反相器

在任何时刻,门输出是该电路实现的Boolean 函数的值。(忽略开关转换的瞬态效应)

与此相对,动态电路的工作是依靠把信号值暂 时存放在高阻节点电容上。

24 24

D 分支努力

IC

分支努力:

b Con path Coff path Con path

25 25

D 多级网络

IC

N

Delay pi gi fi i 1

每级努力:

hi = gifi

路径电气努力: F = Cout/Cin

路径逻辑努力: G = g1g2…gN

11 11

D 互补 CMOS门静态特性

IC

• 高噪声容限: VOH = Vdd,VOL = GND

• 没有静态功耗: 在稳态,上拉和下拉网络互斥,不

存在Vdd到 GND之间的通路。 • 相近的上升、下降沿延时:在适当的尺寸条件下) • 无比逻辑:逻辑功能与器件尺寸无关; • 低输出阻抗:稳态下,总存在一条到Vdd或者GND 的通路; • 高输入阻抗;稳态输入电流几乎为0 • 传播延迟是负载电容和晶体管电阻的函数

0 -0.5

100

200

300

400 A= 10, B=1

57

时间 [ps]

NMOS = 0.5m/0.25 m

PMOS = 0.75m/0.25 m

CL = 100 fF

15 15

D 晶体管尺寸

IC

Rp

Rp

2A

B2

Rn

CL

2B

2 Rn

Cint

A

Rp 4B

4

Rp

Cint

A

Rn 1

A

Rn

CL

B1

确定尺寸,使得延迟近似等于最小尺寸对称反相器

在任何时刻,门输出是该电路实现的Boolean 函数的值。(忽略开关转换的瞬态效应)

与此相对,动态电路的工作是依靠把信号值暂 时存放在高阻节点电容上。

数电04典型的组合逻辑集成电路

Y3 EAB

Yi Emi

mi是A、B旳第i个最小项

例:当E=0时,

若AB=10→m2=1,其他mi=0,此时,Y 2 0

*24

2、集成电路译码器

(1 )二进制译码器

(a) 74HC139集成译码器

1/2 74x139

E

E Y0

Y0

Y1

Y1

A0

A0 Y2

A1

A1

Y3

Y2 Y3

功能表

输入

输出

E A1 A0 Y0 Y1 Y2 Y3 H ××H H H H

H H × × × × × ××H H H H L

H L H × × × × ××H H L H L

H L L H × ×× ××H L H H L

H L L L H × × ××H L L H L

H L L L L H ×××L HHH L

H L L L L L H ××L H L H L

H L L L L L LH×L LHH L

1

1

1

1

三级门电路: 一级反相器 一级四输入与门 一级二输入或门

&

≥1 Y1

&

&

≥1 Y0

&

逻辑图

P101

图4-5-2

*

8

Y 1 I 0 I 1I 2 I 3 I 0 I 1I 2I 3 I0 I1 I2 I3 10 0 0

Y1 Y0 00

Y 0 I 0I 1I 2I 3 I 0I 1I 2I 3 2 0 1 0 0 0 1 30 0 1 0 1 0

编码器能按预先设定旳优先级别,只对其中优先权

最高旳一种进行编码。

*4

ALU

A3 A2 A1 A0加B3B2 B1B0 A加B

结论:当M=L、 Cn=1、 S3S2S1S0=1001时, ALU完成的功能是:

F=A加B

例3:当M=H、S3S2S1S0=1011时,ALU完成什么功能? 解:

①Xi、Yi与Ai、Bi的关系如何?

P A B S A B S A B i

四位加法器 Cn 0 1 2 3 Cn+4

F0 F1 F2 F3

(2)M=H

G13~G16输出均为1,位间不发生关系。

F0~F3为: Fi 1 Pi Gi 1 X i Y i X i Y i

X0 Y0 X1 Y1 X2 Y2 X3 X3

F0

F1

F2

F3

ALU是以Xi、Yi 为输入的异或非门。

组间:

GⅢ

C12 = G12 + P12G11 + P12P11G10 + P12P11P10G9 + P12P11P10P9CⅡ

PⅢ

所以 CⅢ = GⅢ + PⅢ CⅡ

4)第4组进位逻辑式

组内: C13 = G13 + P13CⅢ C14 = G14 + P14G13 + P14P13CⅢ C15 = G15 + P15G14 + P15P14G13 + P15P14P13CⅢ

例2:当M=L、Cn=1、S3S2S1S0=1001时,ALU完成什么功能?

解:

Pi Ai Bi S 2 Ai Bi S 3 Ai Bi

①Pi=? Gi=?

G A B i Ai Bi S0 Bi S1

•

i

i

P ②Xi=?

i X i Yi

结论:当M=L、 Cn=1、 S3S2S1S0=1001时, ALU完成的功能是:

F=A加B

例3:当M=H、S3S2S1S0=1011时,ALU完成什么功能? 解:

①Xi、Yi与Ai、Bi的关系如何?

P A B S A B S A B i

四位加法器 Cn 0 1 2 3 Cn+4

F0 F1 F2 F3

(2)M=H

G13~G16输出均为1,位间不发生关系。

F0~F3为: Fi 1 Pi Gi 1 X i Y i X i Y i

X0 Y0 X1 Y1 X2 Y2 X3 X3

F0

F1

F2

F3

ALU是以Xi、Yi 为输入的异或非门。

组间:

GⅢ

C12 = G12 + P12G11 + P12P11G10 + P12P11P10G9 + P12P11P10P9CⅡ

PⅢ

所以 CⅢ = GⅢ + PⅢ CⅡ

4)第4组进位逻辑式

组内: C13 = G13 + P13CⅢ C14 = G14 + P14G13 + P14P13CⅢ C15 = G15 + P15G14 + P15P14G13 + P15P14P13CⅢ

例2:当M=L、Cn=1、S3S2S1S0=1001时,ALU完成什么功能?

解:

Pi Ai Bi S 2 Ai Bi S 3 Ai Bi

①Pi=? Gi=?

G A B i Ai Bi S0 Bi S1

•

i

i

P ②Xi=?

i X i Yi

(最新整理)常用组合逻辑集成电路介绍

识别多个编码请求信号的优先级别,并进行相应编码的逻 辑部件称为优先编码器。

2021/7/26

10

(2)优先编码器线(4─2 线优先编码器)(设计)

输入编码信号高电平有效,输出为二进制代码

输入编码信号优先级从高到低为 I3 ~ I0

输入为编码信号I3~ I0 输出为Y1 Y0

(1)列出功能表

输入

输出

EI2

1

I7 I6 I5 I4 I3 I2 I1 I0

EI

C允D许4532(II)

EO2 EO

0

GS

Y2 Y1 Y0

I7 I6 I5 I4 I3 I2 I1 I0

EI1 EI C禁D4止532(I) EO

GS

Y2 Y1 Y0

EO1

0

GS2 1

000 111

GS1 0 0 0 0

≥1 G3

≥1 G2

≥1 G1

Yn-

n位二进 制码输

出

2021/7/26

1

3

3、)编码器的分类:普通编码器和优先编码器。

普通编码器:任何时候只允许输入一个有效编码信号,否则 输出就会发生混乱。

优先编码器:允许同时输入两个以上的有效编码信号。当同 时输入几个有效编码信号时,优先编码器能按预先设定的优 先级别,只对其中优先权最高的一个进行编码。

YEE 135067242

3

逻辑图

个

编

A0

1

1

码

输

A1

1

1

入

A2

1

1

端

3

个

E3

1

控 制

E2

1

&

端

E1

2021/7/26

10

(2)优先编码器线(4─2 线优先编码器)(设计)

输入编码信号高电平有效,输出为二进制代码

输入编码信号优先级从高到低为 I3 ~ I0

输入为编码信号I3~ I0 输出为Y1 Y0

(1)列出功能表

输入

输出

EI2

1

I7 I6 I5 I4 I3 I2 I1 I0

EI

C允D许4532(II)

EO2 EO

0

GS

Y2 Y1 Y0

I7 I6 I5 I4 I3 I2 I1 I0

EI1 EI C禁D4止532(I) EO

GS

Y2 Y1 Y0

EO1

0

GS2 1

000 111

GS1 0 0 0 0

≥1 G3

≥1 G2

≥1 G1

Yn-

n位二进 制码输

出

2021/7/26

1

3

3、)编码器的分类:普通编码器和优先编码器。

普通编码器:任何时候只允许输入一个有效编码信号,否则 输出就会发生混乱。

优先编码器:允许同时输入两个以上的有效编码信号。当同 时输入几个有效编码信号时,优先编码器能按预先设定的优 先级别,只对其中优先权最高的一个进行编码。

YEE 135067242

3

逻辑图

个

编

A0

1

1

码

输

A1

1

1

入

A2

1

1

端

3

个

E3

1

控 制

E2

1

&

端

E1

组合逻辑电路

4选1数据选择器74153的逻辑电路如图7.2.26所示。根据逻 辑电路写出逻辑表达式,当使能端 =0时,

7.2 常用组合逻辑电路

由式(7.2.11)可写出功能表,如表7.2.10 所示。

7.2 常用组合逻辑电路

由功能表可以看出:当使能 端 =1时,不论其他输入端的 状态如何,都不会有输出,F=0; 只有当 =0时,输出数据才决定 于地址输入A1A0的不同组合。数 据选择器相当于一个被地址码控 制的4选1多路开关。

7.2 常用组合逻辑电路

7.2 常用组合逻辑电路

7.2.5 数据选择器

1

数据选择器的功能与电路

数据选择器(multiplexer,MUX)又称多路开关或多路选 择器,它根据地址选择信号,从多路输入数据中选择一路送至输 出端,其作用与图7.2.25所示的单刀多掷开关相似。

7.2 常用组合逻辑电路

7.2 常用组合逻辑电路

7.2 常用组合逻辑电路

7.2 常用组合逻辑电路

7.2 常用组合逻辑电路

7.2.2 译码器

1

二进制编码器

将二进制代码的各种状态按照其原来的含义翻译过来,称为 二进制译码器。例如,二进制代码001可能代表数码管的一字形 灯丝,也可能代表1号机组等。

例7.2.4 试用译码器和门电路实现下列逻辑函数。 F=AB+BC+AC

7.2 常用组合逻辑电路

2

二—十进制编码器

用四位二进制代码来表示一 位十进制数字0、1、2、…、9,

BCD

方案很多,最常用的是8421码。 例如,对十进制数字9进行编

码时,数码盘拨到数字9,输入端 9=1,其余输入端均为0。这时输 出端D=1,C=0,B=0,A=1, 即DCBA=1001,也就是将十进 制数字9 1001。其他编码原理类同。

7.2 常用组合逻辑电路

由式(7.2.11)可写出功能表,如表7.2.10 所示。

7.2 常用组合逻辑电路

由功能表可以看出:当使能 端 =1时,不论其他输入端的 状态如何,都不会有输出,F=0; 只有当 =0时,输出数据才决定 于地址输入A1A0的不同组合。数 据选择器相当于一个被地址码控 制的4选1多路开关。

7.2 常用组合逻辑电路

7.2 常用组合逻辑电路

7.2.5 数据选择器

1

数据选择器的功能与电路

数据选择器(multiplexer,MUX)又称多路开关或多路选 择器,它根据地址选择信号,从多路输入数据中选择一路送至输 出端,其作用与图7.2.25所示的单刀多掷开关相似。

7.2 常用组合逻辑电路

7.2 常用组合逻辑电路

7.2 常用组合逻辑电路

7.2 常用组合逻辑电路

7.2 常用组合逻辑电路

7.2.2 译码器

1

二进制编码器

将二进制代码的各种状态按照其原来的含义翻译过来,称为 二进制译码器。例如,二进制代码001可能代表数码管的一字形 灯丝,也可能代表1号机组等。

例7.2.4 试用译码器和门电路实现下列逻辑函数。 F=AB+BC+AC

7.2 常用组合逻辑电路

2

二—十进制编码器

用四位二进制代码来表示一 位十进制数字0、1、2、…、9,

BCD

方案很多,最常用的是8421码。 例如,对十进制数字9进行编

码时,数码盘拨到数字9,输入端 9=1,其余输入端均为0。这时输 出端D=1,C=0,B=0,A=1, 即DCBA=1001,也就是将十进 制数字9 1001。其他编码原理类同。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3

Y1 = I 0 I1I 2 I 3 + I 0 I1I 2 I 3

Y1 = I 0 I1I 2 I 3 + I 0 I1I 2 I 3

Y0 = I0I1I2I

I0 1 ≥1 Y1 I1 1 &

3

+ I0I1I2I

&

3

I2

1

&

I3

1 &

≥1 Y0

该电路是否可以再简化?

(2.) 键盘输入8421BCD码编码器

1

1 1

1

1 1

1

1 0

1

0 1

0

1 1

1

1 1

1

1 1

1

1 1

1

1 1

1

1 1

0

0 0

1

0 0

0

1 1

0

1 0

1

1 1

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

0

1

1

该编码器为输入低电平有效

普通4 线─2线编码器电路存在问题?

& I0 1 ≥1 Y1 I1 1 &

当所有的输入都为1时,

输 EI L H I7 × L I6 × L I5 × L I4 × L 入 I3 × L I2 × L I1 × L I0 × L L L 输 Y1 L L 出 Y0 L L GS L L EO L H

H

H H

H

L L

×

H L

×

× H

×

× ×

×

× ×

×

× ×

×

L ×

×

× ×

L

L L

L

L H

L

H L

(2)优先编码器线(4─2 线优先编码器)(设计) 输入编码信号高电平有效,输出为二进制代码

输入编码信号优先级从高到低为 I3 ~ I0

输入为编码信号I3~ I0 (1)列出功能表 输 I0 1 × I1 0 1 入 I2 I3 0 0 0 0 输 Y1 0 0 出 Y0 0 1 输出为Y1 Y0

如BCD编码器:将10个编码输入信号分别编成10个4位 码输出。 如8线-3线编码器:将8个输入的信号分别编成8个3位二进 制数码输出; 二进制编码器的结构框图

I0 Y0 I1 二进制 Y1 编码器

I2 n 1

2n 个 输入

Yn1

n 位二进 制码输 出

3、)编码器的分类:普通编码器和优先编码器。 普通编码器:任何时候只允许输入一个有效编码信号,否则 输出就会发生混乱。 优先编码器:允许同时输入两个以上的有效编码信号。当同 时输入几个有效编码信号时,优先编码器能按预先设定的优 先级别,只对其中优先权最高的一个进行编码。

4.4

常用组合逻辑集成电路

4.1.1 编码器

1、)编码器 (Encoder)的概念与分类 编码:赋予二进制代码特定含义的过程称为编码。 如:8421BCD码中,用1000表示数字8 如:ASCII码中,用1000001表示字母A等

编码器:具有编码功能的逻辑电路。

2、)编码器的逻辑功能:

能将每一个编码输入信号变换为不同的二进制的代码输出。

H

L L

L

H H

H

H H

L

× ×

L

× ×

L

× L

H

L L

×

H L

×

× H

×

× ×

×

× ×

L

H H

H

L L

H

L H

L

L L

H

H H

H

H

×

L

L

L

L

L

L

L

L

L

L

L

H

L

×

H

H

H

H

H

L

H

L

H

H

H

用二片CD4532构成16线-4线优先编码器,其逻辑 图如下图所示,试分析其工作原理。

无编码输出

A15 A14A13 A12 A11A10 A9 A8 。 I 7 I 6 I 5 I 4 I 3 I 2 I1 I 0 EI GS CD4532(II) 禁止 EO Y2 Y1 Y0 A7 A6 A5 A4 A3 A2 A1 A0 I7 I6 I5 I4 I3 I2 I1 I0 EI GS GS1 CD4532(I) 禁止 EO Y2 Y1 Y0

I4 I5 I6 I7 EI Y2 Y1 GND

1 2 3 4 5 6 7 8

16 15 14 13 12 11 10 9

VCC EO GS I3 I2 I1 I0 Y0

I1

1

≥1 ≥1

CD4532电路图

I2

1 1 & & 1

Y0

≥1 ≥1 1 ≥1

I3 I4 I5 I6 I7

1 1

&

&

1

Y1

1 1 1

1、编码器的工作原理 (1) 普通编码器(4线─2线编码器)

(a)逻辑框图

I0 Y1 Y0

(2)逻辑功能表

I1 I2 I3

4 输 入

二 进 制 码 输 出

I0 1

I1 0

I2 0

I3 0

Y1 0

Y0

0

1

0

0

0

1 1

1

0 1

0

编码器的输入为高电平有效。

0

0

1

Y0 = I0I1I2I

3

+ I0I1I2I

Y1Y0 = ? Y1Y0 = 00?

无法产生有效编码输出。 普通编码器不能同时输 入两个已上的有效编码 信号

I2

1

&

I3

1 &

≥1 Y0

3. 优先编码器

优先编码器的提出: 普通编码器如果有两个 或更多输入信号有效, 将会出现输出混乱。 必须根据轻重缓急,规定好这些外设允许操作的先后次 序,即优先级别。 识别多个编码请求信号的优先级别,并进行相应编码的 逻辑部件称为优先编码器。

1 & 1 & 1

Y2

≥1 ≥1

≥1 ≥1

&

1 1

GS EO

I0 EI

1 1

EI=1,电路工作,无有效高电平输入, EI=1 ,电路工作,输入 I0 ~ EI=0 ,电路不工作, GS =I EO =0, 7分别有高电平输入时, 3. 集成电路优先编码器 CD 的逻辑功能表 A AI =111 , GS = 4532 0GS ,EO=1 A2 A1 A I1 的编码输出, =0 ,; EO =1。 2A 0 0为 0 2~ 17A 0 =000

VCC S0 0 1 2 S3 3 S4 4 S5 5 S6 6 S7 7 S8 8 9 S9 & A & B & C & S1 S2 1kΩ ×10

控制使能标志

& GS

≥1 D

输 出 代 码

逻辑图

2. 键盘输入8421BCD码编码器 (2)功能表

输 S0 1 1 1 1 1 1 S1 1 1 1 1 1 1 S2 1 1 1 1 1 1 S3 1 1 1 1 1 1 S4 1 1 1 1 1 1 S5 1 1 1 1 1 0 入 S6 1 1 1 1 0 1 S7 1 1 1 0 1 1 S8 S9 1 1 0 1 1 1 1 0 1 1 1 1 A 0 1 1 0 0 0 B 0 0 0 1 1 1 输 出 C 0 0 0 1 1 0 D 0 1 0 1 0 1 GS 0 1 1 1 1 1

(2)写出逻辑表达式

Y1 = I 2 I 3 + I 3 Y0 = I 1 I 2 I 3 + I 3

(3)画出逻辑电路(略)

× ×

1

0

1

1

1 高

0

1

× × × 低

2

集成电路编码器

优先编码器CD4532的示意框图、引脚图

I0 EO I1 GS I2 I3 I4 CD4532 I5 Y0 I6 Y1 I7 Y2 EI