实验六 图的应用及其实现

实验6 蒸汽压缩制冷

实验6 蒸汽压缩制冷(热泵)装置性能实验一、实验目的1. 了解蒸汽压缩制冷(热泵)装置。

学习运行操作的基本知识。

2. 测定制冷剂的制冷系数。

掌握热工测量的基本技能。

3. 分析制冷剂的能量平衡。

二、实验任务1. 测定水冷式单级蒸汽压缩制冷系统的制冷系数。

2. 了解壳管式换热器的性能,节流阀的调节方法和性能。

3. 了解热泵循环系统的流程和制热系数的概念。

三、实验原理该系统是由压缩机、冷凝器、节流阀和蒸发器组成,制冷机的作用是从低温物体中取出热量、并将它传给周围介质。

热力学第二定律指出:“不可能使热量由低温物体传向高温物体而不引起其他的变化”。

本实验用制冷装置,需要消耗机械功。

用工质进行制冷循环,从而获得低温。

蒸汽压缩制冷循环的经济性可用制冷系数ε来评价。

鉴于实际设备存在的各种实际损失,故ε值可分为“理论制冷系数”和“实际制冷系数”。

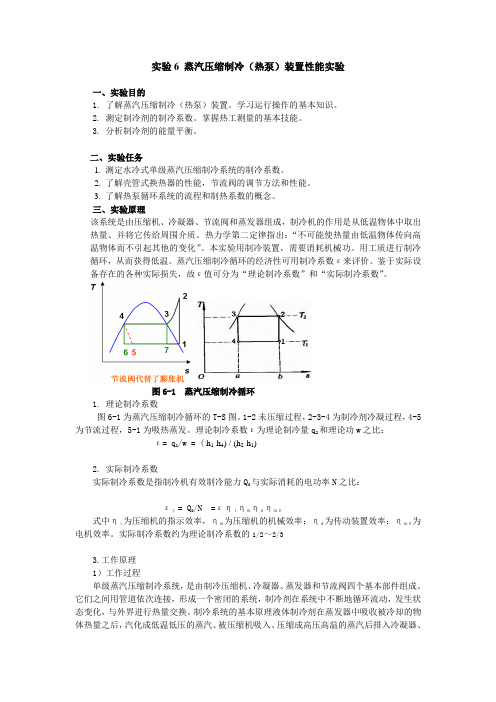

图6-1 蒸汽压缩制冷循环1. 理论制冷系数图6-1为蒸汽压缩制冷循环的T-S图。

1-2未压缩过程,2-3-4为制冷剂冷凝过程,4-5为节流过程,5-1为吸热蒸发。

理论制冷系数ε为理论制冷量q2和理论功w之比:ε= q2/w = ( h1-h4) / (h2-h1)2. 实际制冷系数实际制冷系数是指制冷机有效制冷能力Q0与实际消耗的电功率N之比:εγ= Q0/N =εηiηmηdηm0式中ηi为压缩机的指示效率,ηm为压缩机的机械效率;ηd为传动装置效率;ηm0为电机效率。

实际制冷系数约为理论制冷系数的1/2~2/33.工作原理1)工作过程单级蒸汽压缩制冷系统,是由制冷压缩机、冷凝器、蒸发器和节流阀四个基本部件组成。

它们之间用管道依次连接,形成一个密闭的系统,制冷剂在系统中不断地循环流动,发生状态变化,与外界进行热量交换。

制冷系统的基本原理液体制冷剂在蒸发器中吸收被冷却的物体热量之后,汽化成低温低压的蒸汽、被压缩机吸入、压缩成高压高温的蒸汽后排入冷凝器、在冷凝器中向冷却介质(水或空气)放热,冷凝为高压液体、经节流阀节流为低压低温的制冷剂、再次进入蒸发器吸热汽化,达到循环制冷的目的。

实验六+图形界面

实验六图形界面实验日期:2016 年6 月12 日班级:软件1401 学号(后四位):__0127_______ 姓名:_程瑞强_______ 成绩:成绩:一.实验目的1.掌握图形用户界面的设计方法2.掌握常用的构建用户界面的组件的用法3.掌握事件操作的原理4.能够对所设计的用户界面进行事件处理5.能够应用运算符解决实际小问题6.进一步熟悉Java的面向对象的编程思想二.实验题目(前2题任选1题,第3,4题任选1题)1.采用图形界面实现两个内容的交换,图形界面如下图1所示所示:图1 内容交换代码如下:package TestChange;import java.awt.BorderLayout;import java.awt.event.ActionEvent;import java.awt.event.ActionListener;import javax.swing.JButton;import javax.swing.JFrame;import javax.swing.JPanel;import javax.swing.JTextField;public class TestChange extends JFrame implements ActionListener{private static final long serialVersionUID = -3684503858019589006L;JPanel panel;JTextField tt1;JTextField tt2;JButton button;public TestChange(){this.setTitle("TestChange");this.setSize(355, 85);this.setDefaultCloseOperation(JFrame.EXIT_ON_CLOSE);panel = new JPanel();tt1 = new JTextField(10);tt2 = new JTextField(10);button = new JButton("Change");button.addActionListener(this);panel.add(tt1);panel.add(tt2);panel.add(button);this.add(panel, BorderLayout.NORTH);this.setResizable(false);this.setVisible(true);}public static void main(String[] str){new TestChange();}@Overridepublic void actionPerformed(ActionEvent e) {if(e.getSource() == button){String temp = tt1.getText();tt1.setText(tt2.getText());tt2.setText(temp);}}}2. 采用图形界面设计如下图2所示的界面。

实验六 方波发生器

实验六方波发生器一、实训目的1、学习单片机内部定时器的硬件结构及其应用。

2、定时器T0、T1的两种用途之一:作为定时器实现定时控制。

3、掌握TMOD、TCON的各位的意义,学会可编程控制方法。

4、学会使用VSM虚拟示波器观测波形。

二、实训预备知识1、单片机内部定时器/计数器的编程主要是时间常数的设置和有关控制寄存器的设置。

内部定时器/计数器在单片机的主要有定时和计数两种功能,本实训使用的是定时功能。

2、与定时器有关的寄存器有工作方式寄存器TMOD和控制寄存器TCON。

TMOD用于设置定时器/计数器的工作方式0~3,并确定用于定时还是计数。

TCON主要功能是为了定时器在溢出时设定标志位,并控制定时器的运行或停止。

3、内部计数器用作定时器时,是对机器周期计数。

每个机器周期的长度是12个振荡周期。

4、在设置时间常数前要先关闭对应的中断,设置完时间常数之后再打开该中断。

三、实训设备:微机一台、实训箱、THKL-C51仿真器、示波器、扁平数据线和一条串行数据通信线。

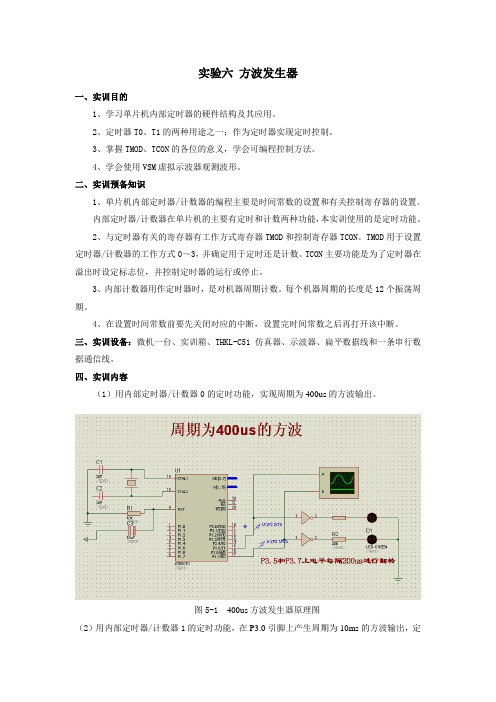

四、实训内容(1)用内部定时器/计数器0的定时功能,实现周期为400us的方波输出。

图5-1 400us方波发生器原理图(2)用内部定时器/计数器1的定时功能,在P3.0引脚上产生周期为10ms的方波输出,定时器采用查询和中断两种方式实现。

图5-210ms方波发生器原理图(3)用内部定时器/计数器0的方式2,在P3.0引脚上产生矩形波, 高电平为50us,低电平为300us。

五、程序设计步骤1、PROTEUS电路设计图4-25 矩形波波形图方波发生器电路原理图如图5-1、5-2所示,设计在PROTEU ISIS平台中进行。

(1)新建设计文件菜单【file】/【New Design】,出现选择模板窗口,选中”DEFAULT”模板,再单击”OK”按钮,在文件名框中输入文件名,单击”保存”按钮,则保存新建设计文件,其后缀自动为.DSN。

(2)从PROTEUS库中选取元器件单击“P”按钮,在其左上角“Keywords”(关键字)一栏中输入以下元器件的关键字,将以下元器件添加到对象选择器中。

实验六、示波器的调整和使用

实验六、示波器的调整和使用示波器是一种用来检测观察信号的常用仪器,其规格和型号很多,但主要组成部分基本相同。

可将信号衰减或放大,可观测信号的波形,测量电压和频率等。

预习要点1、示波器的主要结构和显示波形的基本原理2、示波器的校准和测量3、什么是李萨如图形?一、实验目的1.了解示波器的主要结构和显示波形的基本原理。

2.学会使用信号发生器。

3.学会正确使用示波器观察波形以及测量电压、周期和频率。

二、实验原理示波器是一种能观察各种电信号波形并可测量其电压、频率等的电子测量仪器。

示波器还能对一些能转化成电信号的非电量进行观测,因而它还是一种应用非常广泛的、通用的电子显示器。

1.示波器的基本结构示波器的型号很多,但其基本结构类似。

示波器主要是由示波管、X轴与Y轴衰减器和放大器、锯齿波发生器、整步电路、和电源等几步分组成。

其框图如图1所示。

(1) 示波管示波管由电子枪、偏转板、显示屏组成。

电子枪:由灯丝H、阴极K、控制栅极G、第一阳极A1、第二阳极A2组成。

灯丝通电发热,使阴极受热后发射大量电子并经栅极孔出射。

这束发散的电子经圆筒状的第一阳极A1和第二阳极A2所产生的电场加速后会聚于荧光屏上一点,称为聚焦。

A1与K之间的电压通常为几百伏特,可用电位器W2调节,A1与K之间的电压除有加速电子的作用外,主要是达到聚焦电子的目的,所以A1称为聚焦阳极。

W2即为示波器面板上的聚焦旋钮。

A2与K之间的电压为1千多伏以上,可通过电位器W3调节,A2与K之间的电压除了有聚焦电子的作用外,主要是达到加速电子的作用,因其对电子的加速作用比A1大得多,故称A2为加速阳极。

在有的示波器面板上设有W3,并称其为辅助聚焦旋钮。

在栅极G 与阴极K 之间加了一负电压即U K ﹥U G ,调节电位器W 1可改变它们之间的电势差。

如果G 、K 间的负电压的绝对值越小,通过G 的电子就越多,电子束打到荧光屏上的光点就越亮,调节W 1可调节光点的亮度。

实验六:半加减器、全加减器及其应用(tian)

数字电路实验报告姓名:田佳禾班级: 09011101学号: 2011302068实验六:半加减器、全加减器及其应用一、实验目的(1)掌握双进位全加器74LS183和四位二进制超前进位全加器的74LS283逻辑功能。

(2)熟悉集成加法器的使用方法。

(3)了解算术运算电路的结构。

二、实验设备(1)数字电路实验箱(2)数字万用表(3)74LS138(4)74SLS00(5)若干连接线三、实验原理1、半加/半减器原理两个二进制数相加/减,能实现半加/半减。

实现半加操作的电路叫做半加器。

如果用A表示被加数,B表示加数,S表示半加和,C表示向高位的进/借位,M为控制端,当M为1时是半减器,M为0时是半加器。

表1是半加/减器的真值表。

表 1根据真值表,可得到逻辑函数S 的卡诺图如下:AB 00 01 11 10 M 01B A B A B A S ⊕=+=同理可得逻辑函数C 的卡诺图AB 00 01 11 10()()MABM===+A+C⊕MBBMAAMBA2、全加/全减器原理全加器能进行加数、被加数和低位来的进位信号相加,并根据求和的结果给出该位的进位信号。

如果用Ai、Bi分别表示A、B的第i位,Ci-1表示为相邻低位来的进位数,Si表示为本位和数(称为全加和),Ci表示为向相邻高位的进位数。

则根据全加运算规则可列出全加器的真值表;同理,全减器真值表也可列出。

如表2(M为1表示全减,M为0表示全加)。

表2 根据真值表。

列出函数S的卡诺图:MA 00 01 11 10 BC 00011110CBAABCCBACBAS+++=()()CBABACBAC⊕⊕=⊕+⊕=同理可得C的卡诺图为MA 00 01 11 10 BC 00 01 11 10B A M AB MC A M AC M BC C ++++=()()()()A M C B BC C A M B A M C BC ⊕++=⊕+⊕+=()()()()A M C B BC C A M C B BC ⊕⊕∙=⊕⊕+=四、实验内容1、用74LS00和74LS86实现半加/减器(1)由实验原理知半加/减器中B A B A B A S ⊕=+=, ()()M A B M A M A B BM A M AB C ⊕=+=+= (2)实验电路图如下(3)开关A 、B 、M 接高电平对应真值表中的“1”,接地对应真值表中的“0”,灯S 、C 亮对应真值表中的“1”,不亮对应真值表中的“0”,检验实验电路是否能完成半加/减器的功能。

实验六 图及其应用

实验六图及其应用数据结构实验六图及其应用1、实验目的? 熟练掌握图的两种存储结构(邻接矩阵和邻接表)的表示方法 ? 掌握图的基本运算及应用? 加深对图的理解,逐步培养解决实际问题的编程能力2、实验内容:采用邻接表或邻接矩阵方式存储图,实现图的深度遍历和广度遍历;用广度优先搜索方法找出从一顶点到另一顶点边数最少的路径。

1.问题描述:利用邻接表存储结构,设计一种图(有向或无向),并能够对其进行如下操作:1) 创建一个可以随机确定结点数和弧(有向或无向)数的图; 2) 根据图结点的序号,得到该结点的值;3) 根据图结点的位置的第一个邻接顶点的序号,以及下一个邻接顶点的序号;4) 实现从第v 个顶点出发对图进行深度优先递归遍历; 5) 实现对图作深度优先遍历;6) 实现对图进行广度优先非递归遍历; 编写主程序,实现对各不同的算法调用。

2.实现要求:(以邻接表存储形式为例)编写图的基本操作函数::对图的各项操作一定要编写成为C(C++)语言函数,组合成模块化的形式,每个算法的实现要从时间复杂度和空间复杂度上进行评价。

1)“建立图的邻接表算法”:CreateGraph(ALGraph *G) 操作结果:采用邻接表存储结构,构造没有相关信息的图G2)“邻接表表示的图的递归深度优先遍历算法”:DFSTraverse(ALGraphG,void(*Visit)(char*)) 初始条件:图G 已经存在;操作结果:返回图的按深度遍历的结果。

3)“邻接表表示的图的广度优先遍历算法”: BFSTraverse(ALGraphG,void(*Visit)(char*)) 初始条件:图G 已经存在;操作结果:返回图的按广度遍历的结果。

4)“邻接表从某个结点开始的广度优先遍历算法”:BFS(ALGraph G, int v)初始条件:图G 已经存在;操作结果:返回图从某个结点开始的按广度遍历的结果。

分析: 修改输入数据,预期输出并验证输出的结果,加深对有关算法的理解。

实验五CMOS集成逻辑门的逻辑功能测试报告模板实验六 译码器及其应用

实验五CMOS集成逻辑门的逻辑功能测试一、实验目的1、掌握CMOS集成门电路的逻辑功能和器件的使用规则。

2、学会CMOS集成门电路逻辑功能的测试方法。

二、实验原理本实验将测定与门CC4081,或门CC4071,非门74LS04,与非门CC4011,或非门CC4001的逻辑功能。

各集成块的引脚排列图如下:CC4081四2输入与门CC4071四2输入或门74LS04六反相器(非门)CC4011四2输入与非门CC4001四2输入或非门CMOS电路的使用规则由于CMOS电路有很高的输入阻抗,这给使用者带来一定的麻烦,即外来的干扰信号很容易在一些悬空的输入端上感应出很高的电压,以至损坏器件。

CMOS电路的使用规则如下:V DD接电源正极,V SS接电源负极(通常接地⊥),不得接反。

CC4000系列的电源允许电压在+3~+18V范围内选择,实验中一般要求使用+5~+15V。

所有输入端一律不准悬空,闲置输入端的处理方法:按照逻辑要求,直接接V DD(与非门)或V SS(或非门)。

在工作频率不高的电路中,允许输入端并联使用。

输出端不允许直接与V DD或V SS连接,否则将导致器件损坏。

在装接电路,改变电路连接或插、拔电路时,均应切断电源,严禁带电操作。

焊接、测试和储存时的注意事项:电路应存放在导电的容器内,有良好的静电屏蔽;焊接时必须切断电源,电烙铁外壳必须良好接地,或拔下烙铁,靠其余热焊接;所有的测试仪器必须良好接地。

三、实验设备与器件数字电路实验箱、CC4011、CC4001、CC4071、CC4081。

四、实验内容测试验证CMOS各门电路的逻辑功能,判断其好坏。

与非门CC4011、与门CC4081、或门CC4071及或非门CC4001逻辑功能,其引脚见附录。

以CC4011为例:测试时,选好某一个14P插座,插入被测器件,其输入端A、B接逻辑开关的输出插口,其输出端Y接至逻辑电平显示器输入插口,拨动逻辑电平开关,逐个测试各门的逻辑功能,并记录。

实验六 计数器及其应用

计数器及其应用一、实验目的1.学习集成触发器构成计数器的方法;2.掌握中规模集成计数器的使用方法及功能测试方法;3.用集成电路计数器构成1/N分频器。

二、实验预习要求1.复习计数器电路工作原理;2.预习中规模集成电路计数器74LS192的逻辑功能及使用方法;3.复习实现任意进制计数的方法。

三、实验原理计数器是典型的时序逻辑电路,它用来累计和记忆输入脉冲的个数。

计数是数字系统中很重要的基本操作,集成计数器是最广泛应用的逻辑部件之一。

计数器种类较多,按构成计数器中的多触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器;根据计数制的不同,分为二进制计数器、十进制计数器和任意进制计数器;根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等。

图实验6.1 四位二进制异步加法计数器1. 用D触发器构成异步二进制加/减计数器。

如图实验6.1所示,用四个D触发器构成四位二进制异步加法计数器,其连接特点是将D触发器接成T’触发器,再由低位触发器的/Q 端和高一位的CP端相连。

如果将上图中的Q端与高一位的CP端相连,即可构成四位二进制异步减法计数器。

2. 中规模+进制计数器74LS192是同步十进制可逆计数器,如图实验6.2所示。

图实验6.2 74LS192逻辑符号及引脚排列CPu-加计数端;CPD-减计数端;/LD-置数端;/CO-非同步进位输出端;/BO-非同步借位输出端;D0、D1、D2、D3-计数器输入端;CR-清零端;Q0、Q1、Q2、Q3-数据输出端。

表实验6.1 74LS192逻辑功能表3. 4位同步二进制加法计数器74LS161表实验6.2 74LS161功能表CP-计数脉冲;D0~D3-数据输入端;/CR-清除端;Q0~Q3-输出端;/LD-预置端;CTP、CTT-使能端图实验6.3 74LS161引线排列图4. 计数器级联使用及任意进制计数器的实现(1)任意进制的实现图实验6.4所示利用74LS192采用复位法构成五进制计数器。

08初中物理电学实验PPT 实验六 测量小灯泡及发光二极管的电功率 物理实验设计与应用教学课件

(1)

(2)

6KΩ

12KΩ

(3)?

(4)?

思考题

3.有两个电阻器R1和R2,将其串联后的总电阻是12 欧姆,而将其并联后总电阻的12倍近似于32欧姆, 则R1和R2的电阻各为多大?

R1=? R2=? 12Ω

R1=?

R2=?

R1R212

R1R2 1232 R1 R2

4、8

扩展的参考内容:

A

B

R1

R2

R3

R

电阻串联时,其等效总电X 阻为各个电阻的和.

即: RR 1R 2R n

将一个个电阻直接跨接在某电路A、B的两端,这种接法称 为并联接法,见图7-2。

R1

A

B

R2

R3

RX

电阻并联时,其等1 1

R R1 R2

Rn

将电阻先按不同的串、并联方式组合在一起,然后 跨接在某电路A、B的两端,这种接法称为串并联 (混联)接法,见图3。

0

-

+

V G

G

0

-

+

A G

G

根据表2的要求计算出发光二极管的实际电功率。

表2

实际电压

电压(V) 电流(A)

等于额定电压值

1.6

0.006

低于额定电压值

1.2

0.004

略高于额定电压值 2.0

0.009

发光情况 电功率(W)

正常

0.010

偏暗

0.004

偏亮

0.018

思考题

1.测量小灯泡及发光二极管的电功率除了用伏安法外,还能 用其他方法吗?请设计出不同的测量方法。

2.小灯泡及发光二极管在未接入电路时分别测出的电阻值有 什么区别?

实验06 编码器及其应用

实验六 编码器及其应用一、实验目的1. 掌握一种门电路组成编码器的方法。

2. 掌握8 -3线优先编码器74LS148,10 -4线优先编码器74LS147的功能。

3. 学会使用两片8 -3线编码器组成16 -4线编码器。

二、实验原理 1、4-2编码器赋予若干位二进制码以特定含义称为编码,能实现编码功能的逻辑电路称为编码器。

编码器有若干个输入,在某一时刻只有一个输入信号被转换成二进制码。

下面是一个最简单的4输入、2位二进制码输出的编码器的逻辑原理图:图6-1 4-2编码器逻辑原理图 图6-2 74LS148逻辑图由图可得逻辑表达式为:321032101I I I I I I I I Y += 321032100I I I I I I I I Y +=功能表为:输入 输出 I 0 I 1 I 2 I 3 Y 1 Y 0 1 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 0 0111表6-1 4-2编码器功能表由该表可以看出,当I0~I3中在某一位输入为1时,输出Y1Y0为相应的代码。

例如,当I1为1时,输出Y1 Y0为01。

2、8-3线优先编码器74LS148上面的编码电路虽然简单,但有两个缺点。

其一是,当I0为1,I1~I3都为0和I0~I3均为0时,输出Y1 Y0均为00,这两种情况在实际中必须加以区分;其二是,同时有多个输入被编码时,输出会是混乱的。

在实际工作中,同时有多个输入被编码时,必须根据轻重缓急,规定好这些控制对象允许操作的先后次序,即优先识别。

识别信号的优先级并进行编码的逻辑部件称为优先编码器。

编码器74LS148的作用是将输入I0~I78个状态分别编成二进制码输出,它的功能表见表6-2,它的逻辑图见图6-2。

它有8个输入端,3个二进制码输出端,输入使能端EI,输出使能端EO和优先编码工作状态标志GS。

优先级分别从I7至I0递减。

输入输出EI 0 1 2 3 4 5 6 7 A2A1A0GS EOH ××××××××H H H H HL H H H H H H H H H H H H LL ×××××××L L L L L HL ××××××L H L L H L HL ×××××L H H L H L L HL ××××L H H H L H H L HL ×××L H H H H H L L L HL ××L H H H H H H L H L HL ×L H H H H H H H H L L HL L H H H H H H H H H H L H表6-2 优先编码器74LS148功能表3、10-4线优先编码器74LS14774LS147的输出为8421BCD码,它的逻辑图见图4-3,其功能表为:输入输出1 2 3 4 5 6 7 8 9 D C B A GSH H H H H H H H H H H H H 0××××××××L L H H L 1×××××××L H L H H H 1××××××L H H H L L L 1×××××L H H H H L L H 1××××L H H H H H L H L 1×××L H H H H H H L H H 1××L H H H H H H H H L L 1×L H H H H H H H H H L H 1L H H H H H H H H H H H L 1表6-3 优先编码器74LS147功能表图6-3 74LS147逻辑图三、实验设备与器材1、数字逻辑电路实验箱。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验六图的应用及其实现一、实验目的1.进一步功固图常用的存储结构。

2.熟练掌握在图的邻接表实现图的基本操作。

3.理解掌握AOV网、AOE网在邻接表上的实现以及解决简单的应用问题。

二、实验内容从键盘上输入AOV网的顶点和有向边的信息,建立其邻接表存储结构,然后对该图拓扑排序,并输出拓扑序列. 试设计程序实现上述AOV网的类型定义和基本操作,完成上述功能。

相关常量及结构定义:typedef int InfoType;typedef char VertexType;typedef int SElemType;#define STACK_INIT_SIZE 100 //存储空间初始分配量#define STAXKINCREMENT 10 //存储空间分配增量#define MAX_VERTEX_NUM 20typedef struct ArcNode{int adjvex;struct ArcNode *nextarc;InfoType *info;}ArcNode;typedef struct VNode{VertexType data;struct ArcNode *firstarc;}VNode,AdjList[MAX_VERTEX_NUM];typedef struct ALGraph{AdjList vertices;int vexnum, arcnum;int kind;}ALGraph;typedef struct{SElemType *base;SElemType *top;int stacksize;}SqStack;设计相关函数声明:int CreateDG(ALGraph &G)int InitStack(SqStack &S)int Push(SqStack &S,SElemType e)int Pop(SqStack &S,SElemType &e)int StackEmpty(SqStack S)void FindInDegree(ALGraph G,int *indegree)int TopologicalSort(ALGraph G)三、数据结构与核心算法的设计描述1.创建AOV网int CreateDG(ALGraph &G){int i,j,k,v1,v2;cout<<"请输入该图的顶点数:"<<"请输入该图的边数:"<<endl;cin>>G.vexnum>>G.arcnum;for(i=0;i<G.vexnum;i++){G.vertices[i].data=i;G.vertices[i].firstarc=NULL;}cout<<"请输入一条边的始点和终点:"<<endl;for(k=0;k<G.arcnum;++k){cout<<"请输入第"<<k+1<<"条边的始点和终点: ";cin>>v1>>v2;i=v1; j=v2;while(i<1||i>G.vexnum||j<1||j>G.vexnum){cout<<"请输入第"<<k+1<<"条边的始点和终点: ";cin>>v1>>v2;i=v1; j=v2;}i--;j--;ArcNode *p;p=(ArcNode *)malloc(sizeof(ArcNode));if(!p) return -1;p->adjvex=j;p->nextarc=G.vertices[i].firstarc;p->info=NULL; G.vertices[i].firstarc=p;G.vertices[i];}return 0;}2.初始化栈int InitStack(SqStack &S){S.base=(SElemType*)malloc(STACK_INIT_SIZE*sizeof(SElemType));if(!S.base) exit (-1);S.top=S.base;S.stacksize=STACK_INIT_SIZE;return 0;}3.入栈int Push(SqStack &S,SElemType e){if(S.top-S.base>=S.stacksize){S.base=(SElemType*)realloc(S.base,(S.stacksize+STAXKINCREME NT)*sizeof(SElemType));if(!S.base) exit (-1);S.top=S.base+S.stacksize;S.stacksize+=STAXKINCREMENT; }*S.top++=e;return 0;}4.出栈int Pop(SqStack &S,SElemType &e) {if(S.top==S.base) return -1;e=*--S.top;return 0;}5.判断栈是否为空int StackEmpty(SqStack S){if(S.top==S.base) return -1;else return 0;}6.个顶点入度void FindInDegree(ALGraph G,int *indegree){int i;for(i=0;i<G.vexnum;i++)indegree[i]=0;for(i=0;i<G.vexnum;i++)while(G.vertices[i].firstarc){indegree[G.vertices[i].firstarc->adjvex]++;G.vertices[i].firstarc=G.vertices[i].firstarc->nextarc;}}7.拓扑排序int TopologicalSort(ALGraph G){int i,k,indegree[MAX_VERTEX_NUM];ArcNode *p;SqStack S;FindInDegree(G,indegree);InitStack(S);for(i=0;i<G.vexnum;i++)if(!indegree[i]) Push(S,i);int count=0;while(!StackEmpty(S)){Pop(S,i);cout<<i+1<<'\t'; ++count;for(p=G.vertices[i].firstarc; p; p=p->nextarc){k=p->adjvex;if(!(--indegree[k])) Push(S,k);}}if(count<G.vexnum) return -1;else return 0;}四、函数的调用主函数主要设计:int main(){ALGraph G;CreateDG(G);TopologicalSort(G);return 0;}五、实验总结本次试验通过对有向图进行拓扑排序,我了解了有向图邻接表的存储结构更重要的的是学会了对有向图的拓扑排序算法,其中也将之前学过的栈结合起来,巧妙的找到了一个拓扑序列,可不足的是,该算法只能找到这一条拓扑序列,但是我相信通过完成了这次试验后我会改进算法而能将图的所有的拓扑序列找出来。

六、程序清单#include <iostream>using namespace std;typedef int InfoType;typedef char VertexType;typedef int SElemType;#define STACK_INIT_SIZE 100#define STAXKINCREMENT 10#define MAX_VERTEX_NUM 20 typedef struct ArcNode{int adjvex;struct ArcNode *nextarc; InfoType *info;}ArcNode;typedef struct VNode{VertexType data;struct ArcNode *firstarc;}VNode,AdjList[MAX_VERTEX_NUM]; typedef struct ALGraph{AdjList vertices;int vexnum, arcnum;int kind;}ALGraph;typedef struct{SElemType *base;SElemType *top;int stacksize;}SqStack;int CreateDG(ALGraph &G){int i,j,k,v1,v2;cout<<"请输入该图的顶点数:"<<"请输入该图的边数:"<<endl; cin>>G.vexnum>>G.arcnum;for(i=0;i<G.vexnum;i++){G.vertices[i].data=i;G.vertices[i].firstarc=NULL;}cout<<"请输入一条边的始点和终点:"<<endl;for(k=0;k<G.arcnum;++k){cout<<"请输入第"<<k+1<<"条边的始点和终点: ";cin>>v1>>v2;i=v1; j=v2;while(i<1||i>G.vexnum||j<1||j>G.vexnum){cout<<"请输入第"<<k+1<<"条边的始点和终点: ";cin>>v1>>v2;i=v1; j=v2;}i--;j--;ArcNode *p;p=(ArcNode *)malloc(sizeof(ArcNode));if(!p) return -1;p->adjvex=j;p->nextarc=G.vertices[i].firstarc;p->info=NULL; G.vertices[i].firstarc=p;G.vertices[i];}return 0;}int InitStack(SqStack &S){S.base=(SElemType *)malloc(STACK_INIT_SIZE*sizeof(SElemType));if(!S.base) exit (-1);S.top=S.base;S.stacksize=STACK_INIT_SIZE;return 0;}int Push(SqStack &S,SElemType e){if(S.top-S.base>=S.stacksize){S.base=(SElemType*)realloc(S.base,(S.stacksize+STAXKINCREMENT)*size of(SElemType));if(!S.base) exit (-1);S.top=S.base+S.stacksize;S.stacksize+=STAXKINCREMENT;}*S.top++=e;return 0;}int Pop(SqStack &S,SElemType &e){if(S.top==S.base) return -1;e=*--S.top;return 0;}int StackEmpty(SqStack S){if(S.top==S.base) return -1;else return 0;}void FindInDegree(ALGraph G,int *indegree){int i;for(i=0;i<G.vexnum;i++)indegree[i]=0;for(i=0;i<G.vexnum;i++)while(G.vertices[i].firstarc){indegree[G.vertices[i].firstarc->adjvex]++;G.vertices[i].firstarc=G.vertices[i].firstarc->nextarc;}}int TopologicalSort(ALGraph G){int i,k,indegree[MAX_VERTEX_NUM];ArcNode *p;SqStack S;FindInDegree(G,indegree);InitStack(S);for(i=0;i<G.vexnum;i++)if(!indegree[i]) Push(S,i);int count=0;while(!StackEmpty(S)){Pop(S,i);cout<<i+1<<'\t'; ++count;for(p=G.vertices[i].firstarc; p; p=p->nextarc){k=p->adjvex;if(!(--indegree[k])) Push(S,k);}}if(count<G.vexnum) return -1;else return 0;}int main(){ALGraph G;CreateDG(G);TopologicalSort(G); return 0;}。