外文翻译排版格式参考

毕业论文外文翻译格式【范本模板】

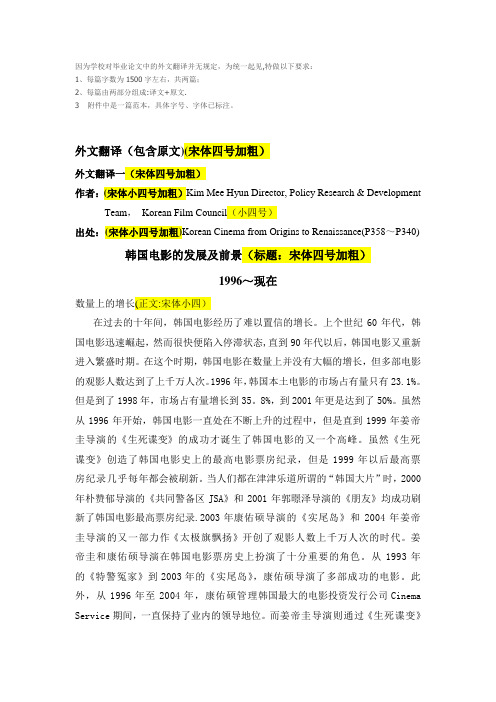

因为学校对毕业论文中的外文翻译并无规定,为统一起见,特做以下要求:1、每篇字数为1500字左右,共两篇;2、每篇由两部分组成:译文+原文.3 附件中是一篇范本,具体字号、字体已标注。

外文翻译(包含原文)(宋体四号加粗)外文翻译一(宋体四号加粗)作者:(宋体小四号加粗)Kim Mee Hyun Director, Policy Research & Development Team,Korean Film Council(小四号)出处:(宋体小四号加粗)Korean Cinema from Origins to Renaissance(P358~P340) 韩国电影的发展及前景(标题:宋体四号加粗)1996~现在数量上的增长(正文:宋体小四)在过去的十年间,韩国电影经历了难以置信的增长。

上个世纪60年代,韩国电影迅速崛起,然而很快便陷入停滞状态,直到90年代以后,韩国电影又重新进入繁盛时期。

在这个时期,韩国电影在数量上并没有大幅的增长,但多部电影的观影人数达到了上千万人次。

1996年,韩国本土电影的市场占有量只有23.1%。

但是到了1998年,市场占有量增长到35。

8%,到2001年更是达到了50%。

虽然从1996年开始,韩国电影一直处在不断上升的过程中,但是直到1999年姜帝圭导演的《生死谍变》的成功才诞生了韩国电影的又一个高峰。

虽然《生死谍变》创造了韩国电影史上的最高电影票房纪录,但是1999年以后最高票房纪录几乎每年都会被刷新。

当人们都在津津乐道所谓的“韩国大片”时,2000年朴赞郁导演的《共同警备区JSA》和2001年郭暻泽导演的《朋友》均成功刷新了韩国电影最高票房纪录.2003年康佑硕导演的《实尾岛》和2004年姜帝圭导演的又一部力作《太极旗飘扬》开创了观影人数上千万人次的时代。

姜帝圭和康佑硕导演在韩国电影票房史上扮演了十分重要的角色。

从1993年的《特警冤家》到2003年的《实尾岛》,康佑硕导演了多部成功的电影。

外文翻译的格式样式

外文翻译格式样式

标题(黑体小二加粗居中)

(宋体小四空一行)

外文作者署名(楷体小四号居中)

(宋体小四空一行)

1 内容(黑体三号加粗)

1.1内容(黑体四号加粗)

边坡是地壳表部一切具有临空面的地质体,具有一定的坡度和高度,包括人工边坡、自然边坡以及崩滑体。

在重力、风化、侵蚀和其它地质作用下,边坡不断地发生变化,应力重新分布,并且随着边(宋体小四号)……

说明:以上为外文翻译的格式,译文前应附有被翻译的外文原件复印件,为了反映文稿的科学依据和译者尊重他人研究成果的严肃态度及向读者提出有关信息的出处,要求译者按著录/题名/出版事项顺序排列注明,请同学们遵照执行。

期刊:著者,题名,期刊名称,出版年,卷号(期号),起始页码。

书籍:著者,书名、版次(第一版不标注),出版地,出版者,出版年,起始页码。

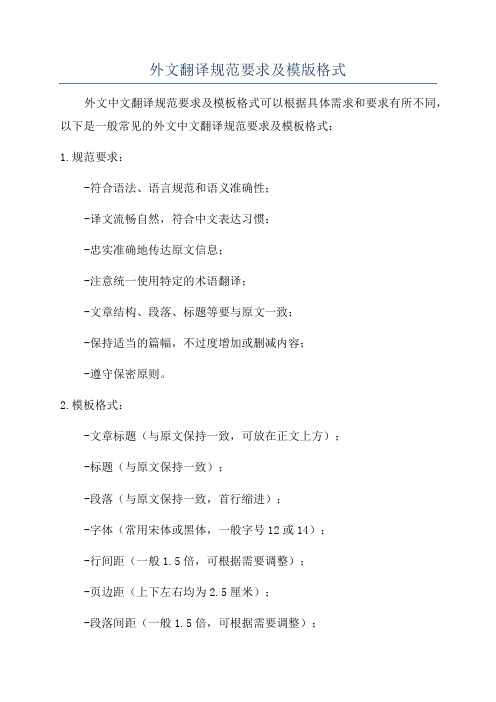

外文翻译规范要求及模版格式

外文翻译规范要求及模版格式

外文中文翻译规范要求及模板格式可以根据具体需求和要求有所不同,以下是一般常见的外文中文翻译规范要求及模板格式:

1.规范要求:

-符合语法、语言规范和语义准确性;

-译文流畅自然,符合中文表达习惯;

-忠实准确地传达原文信息;

-注意统一使用特定的术语翻译;

-文章结构、段落、标题等要与原文一致;

-保持适当的篇幅,不过度增加或删减内容;

-遵守保密原则。

2.模板格式:

-文章标题(与原文保持一致,可放在正文上方);

-标题(与原文保持一致);

-段落(与原文保持一致,首行缩进);

-字体(常用宋体或黑体,一般字号12或14);

-行间距(一般1.5倍,可根据需要调整);

-页边距(上下左右均为2.5厘米);

-段落间距(一般1.5倍,可根据需要调整);

以上是一般常见的外文中文翻译规范要求及模板格式,具体要求和格式可以根据具体的翻译项目和要求进行调整。

在翻译过程中,保持准确、流畅、专业是非常重要的。

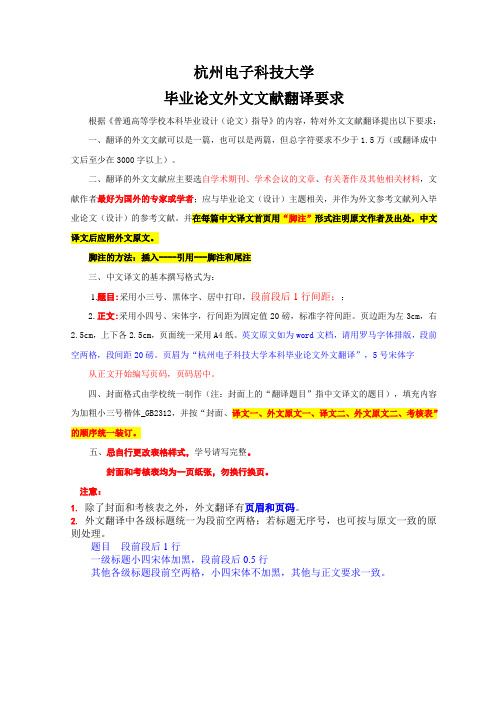

3-外文翻译模板格式及要求

杭州电子科技大学毕业论文外文文献翻译要求根据《普通高等学校本科毕业设计(论文)指导》的内容,特对外文文献翻译提出以下要求:一、翻译的外文文献可以是一篇,也可以是两篇,但总字符要求不少于1.5万(或翻译成中文后至少在3000字以上)。

二、翻译的外文文献应主要选自学术期刊、学术会议的文章、有关著作及其他相关材料,文献作者最好为国外的专家或学者;应与毕业论文(设计)主题相关,并作为外文参考文献列入毕业论文(设计)的参考文献。

并在每篇中文译文首页用“脚注”形式注明原文作者及出处,中文译文后应附外文原文。

脚注的方法:插入----引用---脚注和尾注三、中文译文的基本撰写格式为:1.题目:采用小三号、黑体字、居中打印,段前段后1行间距;;2.正文:采用小四号、宋体字,行间距为固定值20磅,标准字符间距。

页边距为左3cm,右2.5cm,上下各2.5cm,页面统一采用A4纸。

英文原文如为word文档,请用罗马字体排版,段前空两格,段间距20磅。

页眉为“杭州电子科技大学本科毕业论文外文翻译”,5号宋体字从正文开始编写页码,页码居中。

四、封面格式由学校统一制作(注:封面上的“翻译题目”指中文译文的题目),填充内容为加粗小三号楷体_GB2312,并按“封面、译文一、外文原文一、译文二、外文原文二、考核表”的顺序统一装订。

五、忌自行更改表格样式,学号请写完整。

封面和考核表均为一页纸张,勿换行换页。

注意:1.除了封面和考核表之外,外文翻译有页眉和页码。

2.外文翻译中各级标题统一为段前空两格;若标题无序号,也可按与原文一致的原则处理。

题目段前段后1行一级标题小四宋体加黑,段前段后0.5行其他各级标题段前空两格,小四宋体不加黑,其他与正文要求一致。

毕业论文外文文献翻译毕业设计(论文)题目Xxx(单击此处添加论文题目)翻译(1)题目指翻译后的第一篇中文译文的题目翻译(2)题目指翻译后的第二篇中文译文的题目若无,则本栏留空学院经贸学院专业国际经济与贸易(单击此处添加专业)姓名XXXXXX(单击此处添加姓名)班级XX020811(单击此处添加班级)学号XX023101(单击此处添加班级)指导教师XXXXXX(单击此处添加指导教师)单击此处添加翻译后的第一篇中文译文的题目1 [单击此处添加译文正文]一、单击此处添加一级标题1[单击此处添加译文正文]1.[单击此处添加译文正文]2.[单击此处添加译文正文]3.[单击此处添加译文正文]二、单击此处添加一级标题2[单击此处添加译文正文]1.[单击此处添加译文正文]2.[单击此处添加译文正文]3.[单击此处添加译文正文]三、单击此处添加一级标题3……………………………以下是模板的使用方法说明文字,正式成文后请删除。

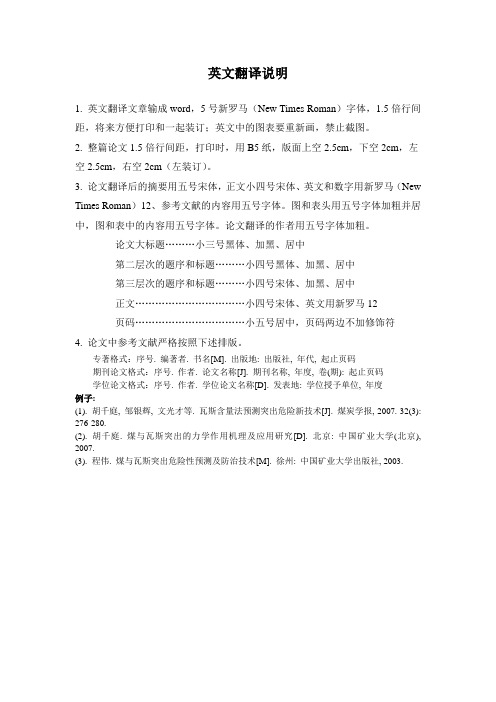

毕业论文(英文翻译)排版格式

英文翻译说明

1. 英文翻译文章输成word,5号新罗马(New Times Roman)字体,1.5倍行间距,将来方便打印和一起装订;英文中的图表要重新画,禁止截图。

2. 整篇论文1.5倍行间距,打印时,用B5纸,版面上空2.5cm,下空2cm,左空2.5cm,右空2cm(左装订)。

3. 论文翻译后的摘要用五号宋体,正文小四号宋体、英文和数字用新罗马(New Times Roman)12、参考文献的内容用五号字体。

图和表头用五号字体加粗并居中,图和表中的内容用五号字体。

论文翻译的作者用五号字体加粗。

论文大标题………小三号黑体、加黑、居中

第二层次的题序和标题………小四号黑体、加黑、居中

第三层次的题序和标题………小四号宋体、加黑、居中

正文……………………………小四号宋体、英文用新罗马12

页码……………………………小五号居中,页码两边不加修饰符

4. 论文中参考文献严格按照下述排版。

专著格式:序号. 编著者. 书名[M]. 出版地: 出版社, 年代, 起止页码

期刊论文格式:序号. 作者. 论文名称[J]. 期刊名称, 年度, 卷(期): 起止页码

学位论文格式:序号. 作者. 学位论文名称[D]. 发表地: 学位授予单位, 年度

例子:

(1). 胡千庭, 邹银辉, 文光才等. 瓦斯含量法预测突出危险新技术[J]. 煤炭学报, 2007. 32(3): 276-280.

(2). 胡千庭. 煤与瓦斯突出的力学作用机理及应用研究[D]. 北京: 中国矿业大学(北京), 2007.

(3). 程伟. 煤与瓦斯突出危险性预测及防治技术[M]. 徐州: 中国矿业大学出版社, 2003.。

外文翻译及外文原文(参考格式)

外文翻译要求:1、外文资料与毕业设计(论文)选题密切相关,译文准确、质量好。

2、阅读2篇幅以上(10000字符左右)的外文资料,完成2篇不同文章的共2000汉字以上的英译汉翻译3、外文资料可以由指导教师提供,外文资料原则上应是外国作者。

严禁采用专业外语教材文章。

4、排序:“一篇中文译文、一篇外文原文、一篇中文译文、一篇外文原文”。

插图内文字及图名也译成中文。

5、标题与译文格式(字体、字号、行距、页边距等)与论文格式要求相同。

下页附:外文翻译与原文参考格式2英文翻译 (黑体、四号、顶格)外文原文出处:(译文前列出外文原文出处、作者、国籍,译文后附上外文原文)《ASHRAE Handbook —Refrigeration 》.CHAPTER3 .SYSTEM Practices for ammonia 3.1 System Selection 3.2 Equipment3.10 Reciprocating Compressors第3章 氨制冷系统的实施3.1 系统选择在选择一个氨制冷系统设计时,须要考虑一些设计决策要素,包括是否采用(1)单级压缩(2)带经济器的压缩(3)多级压缩(4)直接蒸发(5)满液式(6)液体再循环(7)载冷剂。

单级压缩系统基本的单级压缩系统由蒸发器、压缩机、冷凝器、储液器(假如用的话)和制冷剂控制装置(膨胀阀、浮球阀等)。

1997 ASHRAE 手册——“原理篇”中的第一章讨论了压缩制冷循环。

图1.壳管式经济器的布置外文翻译的标题与译文中的字体、字号、行距、页边距等与论文格式相同。

英文原文(黑体、四号、顶格)英文翻译2(黑体,四号,顶格)外文原文出处:(黑体,四号,顶格)P. Fanning. Nonlinear Models of Reinforced and Post-tensioned Concrete Beams. Lecturer, Department of Civil Engineering, University College Dublin. Received 16 Jul 2001.非线形模型钢筋和后张法预应力混凝土梁摘要:商业有限元软件一般包括混凝土在荷载做用下非线性反应的专用数值模型。

外文翻译撰写规范

第一部分:格式篇

1.外文翻译封面中从“院系”——“指导老师”旁边的下划线请保持长度一致。

2.封面中“原文出处”信息应该完整,同参考文献中的外文文献格式。

3.先中文后英文,中文页码为阿拉伯数字,英文页码为罗马数字。

4.中英文上方第一行都是文章或者书的名称,第二行是出处。

5.字间距为标准,行距为固定值,设置值为23。

如标题与标题、标题与段落之

间间距明显较大时,请选定标题并选择“段落”检查间距中“段前”、“段后”

是否是0行。

6.中文文章段落中出现除序号外的阿拉伯数字或英文应用Times New Roman字

体。

第二部分:内容篇

1.必须是英文文献翻译成中文,不能中文翻译成英文。

2. 英文文献必须是外国人写的,不能只是中国人发表的外文论文。

3.外文文献只要和所写课题相关即可,不用完全一致。

如课题为审计风险,如果找不到审计风险的外文,也可以找审计相关的外文即可。

4.关键词前后翻译必须一致,英文缩写在中文翻译中第一次出现时必须翻译出全称。

5.不能仅仅依靠翻译软件,翻译的中文应检查是否语句通顺,是否有词不达意的情况。

(论文)外文翻译模版

沈阳工业大学

本科生外文翻译

文章中文题目:_______________________________ 文章外文题目:_______________________________

学院:

专业班级:

学生姓名:

指导教师:

年月日

外文翻译格式、装订要求(对中文的要求):

1.字数要求:不少于3000中文字符,或不少于10000个英文字符。

2.外文翻译内容一律用A4纸打印;

3.图表5号字,宋体。

图表要居中;图的编号和名称在图下,居中;表的编号和名称在表上,居中。

4.大标题用三号宋体(加粗)、小标题用四号宋体(加粗)、内容用小四宋体、行间距20磅、页边距上下2.54厘米、左右3.17厘米。

5.中文在上,外文在下,左侧装订。

(外文必须用A4纸打印,原文其它格式格式可以不变)

6.统一用上页封面和指导教师评语,指导教师评语装订在最后一页。

外文文献翻译封面格式及要求(模版)

毕业论文外文文献翻译院年级专业:2009级XXXXXXXXXXX 姓 名:学 号:附 件:备注:(注意:备注页这一整页的内容都不需要打印,看懂了即可)1.从所引用的与毕业设计(论文)内容相近的外文文献中选择一篇或一部分进行翻译(不少于3000实词);2.外文文献翻译的装订分两部分,第一部分为外文文献;第二部分为该外文文献的中文翻译,两部分之间用分页符隔开。

也就是说,第一外文文献部分结束后,使用分页符,另起一页开始翻译。

3.格式方面,外文文献的格式,除了字体统一使用Times new roman 之外,其他所有都跟中文论文的格式一样。

中文翻译的格式,跟中文论文的格式一样。

(注意:备注页这一整页的内容都不需要打印,看懂了即可,定稿后,请删除本页.)范文如下:注意,下面内容每一部份均已用分页符分开了,如果用本模板,请将每一模块单独删除,直接套用到每一模板里面,不要将全部内容一次性删除.【Abstract】This paper has a systematic analysis on outside Marco-environment of herbal tea beverage industry and major competitors of brands inside the herbal tea market. Based onthe theoretic framework, this paper takes WONG LO KAT and JIA DUO BAO herbal tea as an example, and researches the strategy on brand positioning and relevant marketing mix of it. Through analysis on the prevention sense of WONG LO KAT herbal tea, it was positioned the beverage that can prevent excessive internal heat in body, a new category divided from the beverage market. the process of brand positioning of it in Consumers brain was finished. Based on this positioning strategy, WONG LO KAT reasonably organized and arranged its product strategy, price strategy, distribution strategy and promotion strategy, which not only served for and further consolidated the position of preventing excessive internal heat in body, but also elevated the value of brand. The JDB and WONG LO KAT market competition brings us enlightenment. Reference the successful experience from the JDB and lessons from the failure of the WONG LO KAT.,Times New Roman.【Key Words】Brand positioning; Marketing mix; Positioning Strategy; enlightenment, lessons;ABC(本页为英文文献摘要,关键词两项一起单独一页,字体为:Times New Roman,小四号,1.5倍行距)(注:以下为英文文献正文内容,英文全文3000字.具体标题以原文为准.全文字体为Times New Roman.行间距为1.5倍.字号大小与论文正文的各级标题一致.如下:)I.Times New Roman ,Times New Roman,Times New RomanTimes New Roman, Times New Roman, Times New Roman, Times New Roman,This paper has a systematic analysis on outside Marco-environment of herbal tea beverage industry and major competitors of brands inside the herbal tea market. Based on the theoretic framework, this paper takes WONG LO KAT and JIA DUO BAO herbal tea as an example, and researches the strategy on brand positioning and relevant marketing mix of it. Through analysis on the prevention sense of WONG LO KAT herbal tea, it was positioned the beverage that can prevent excessive internal heat in body, a new category divided from the beverage market. the process of brand positioning of it in Consumers brain was finished. Based on this positioning strategy, WONG LO KAT reasonably organized and arranged its product strategy, price strategy, distribution strategy and promotion strategy, which not only served for and further consolidated the position of preventing excessive internal heat in body, but also elevated the value of brand. The JDB and WONG LO KAT market competition brings us enlightenment. Reference the successful experience from the JDB and lessons from the failure of the WONG LO KAT.This paper has a systematic analysis on outside Marco-environment of herbal tea beverage industry and major competitors of brands inside the herbal tea market. Based on the theoretic framework, this paper takes WONG LO KAT and JIA DUO BAO herbal tea as an example, and researches the strategy on brand positioning and relevant marketing mix of it. Through analysis on the prevention sense of WONG LO KAT herbal tea, it was positioned the beverage that can prevent excessive internal heat in body, a new category divided from the beverage market. the process of brand positioning of it in Consumers brain was finished. Based on this positioning strategy, WONG LO KAT reasonably organized and arranged its product strategy, price strategy, distribution strategy and promotion strategy, which not only served for and further consolidated the position of preventing excessive internal heat in body, but also elevated the value of brand. The JDB and WONG LO KAT market competition brings us enlightenment. Reference the successful experience from the JDB and lessons fromthe failure of the WONG LO KAT.II.Times New Roman ,Times New Roman,Times New RomanTimes New Roman, Times New Roman, Times New Roman, Times New Roman,This paper has a systematic analysis on outside Marco-environment of herbal tea beverage industry and major competitors of brands inside the herbal tea market. Based on the theoretic framework, this paper takes WONG LO KAT and JIA DUO BAO herbal tea as an example, and researches the strategy on brand positioning and relevant marketing mix of it. Through analysis on the prevention sense of WONG LO KAT herbal tea, it was positioned the beverage that can prevent excessive internal heat in body, a new category divided from the beverage market. the process of brand positioning of it in Consumers brain was finished. Based on this positioning strategy, WONG LO KAT reasonably organized and arranged its product strategy, price strategy, distribution strategy and promotion strategy, which not only served for and further consolidated the position of preventing excessive internal heat in body, but also elevated the value of brand. The JDB and WONG LO KAT market competition brings us enlightenment. Reference the successful experience from the JDB and lessons from the failure of the WONG LO KAT.This paper has a systematic analysis on outside Marco-environment of herbal tea beverage industry and major competitors of brands inside the herbal tea market. Based on the theoretic framework, this paper takes WONG LO KAT and JIA DUO BAO herbal tea as an example, and researches the strategy on brand positioning and relevant marketing mix of it. Through analysis on the prevention sense of WONG LO KAT herbal tea, it was positioned the beverage that can prevent excessive internal heat in body, a new category divided from the beverage market. the process of brand positioning of it in Consumers brain was finished. Based on this positioning strategy, WONG LO KAT reasonably organized and arranged its product strategy, price strategy, distribution strategy and promotion strategy, which not only served for and further consolidated the position of preventing excessive internal heat in body, but also elevated the value of brand. The JDB and WONG LO KAT market competition brings us enlightenment. Reference the successful experience from the JDB and lessons from the failure of the WONG LO KAT.III.Times New Roman ,Times New Roman,Times New RomanTimes New Roman, Times New Roman, Times New Roman, Times New Roman,This paper has a systematic analysis on outside Marco-environment of herbal tea beverage industry and major competitors of brands inside the herbal tea market. Based on the theoretic framework, this paper takes WONG LO KAT and JIA DUO BAO herbal tea as an example, and researches the strategy on brand positioning and relevant marketing mix of it. Through analysis on the prevention sense of WONG LO KAT herbal tea, it was positioned the beverage that can prevent excessive internal heat in body, a new category divided from the beverage market. the process of brand positioning of it in Consumers brain was finished. Based on this positioning strategy, WONG LO KAT reasonably organized and arranged its product strategy, price strategy, distribution strategy and promotion strategy, which not only served for and further consolidated the position of preventing excessive internal heat in body, but also elevated the value of brand. The JDB and WONG LO KAT market competition brings us enlightenment. Reference the successful experience from the JDB and lessons from the failure of the WONG LO KAT.This paper has a systematic analysis on outside Marco-environment of herbal tea beverage industry and major competitors of brands inside the herbal tea market. Based on the theoretic framework, this paper takes WONG LO KAT and JIA DUO BAO herbal tea as an example, and researches the strategy on brand positioning and relevant marketing mix of it. Through analysis on the prevention sense of WONG LO KAT herbal tea, it was positioned the beverage that can prevent excessive internal heat in body, a new category divided from the beverage market. the process of brand positioning of it in Consumers brain was finished. Based on this positioning strategy, WONG LO KAT reasonably organized and arranged its product strategy, price strategy, distribution strategy and promotion strategy, which not only served for and further consolidated the position of preventing excessive internal heat in body, but also elevated the value of brand. The JDB and WONG LO KAT market competition brings us enlightenment. Reference the successful experience from the JDB and lessons from the failure of the WONG LO KAT.This paper has a systematic analysis on outside Marco-environment of herbal teabeverage industry and major competitors of brands inside the herbal tea market. Based on the theoretic framework, this paper takes WONG LO KAT and JIA DUO BAO herbal tea as an example, and researches the strategy on brand positioning and relevant marketing mix of it. Through analysis on the prevention sense of WONG LO KAT herbal tea, it was positioned the beverage that can prevent excessive internal heat in body, a new category divided from the beverage market. the process of brand positioning of it in Consumers brain was finished. Based on this positioning strategy, WONG LO KAT reasonably organized and arranged its product strategy, price strategy, distribution strategy and promotion strategy, which not only served for and further consolidated the position of preventing excessive internal heat in body, but also elevated the value of brand. The JDB and WONG LO KAT market competition brings us enlightenment. Reference the successful experience from the JDB and lessons from the failure of the WONG LO KAT.This paper has a systematic analysis on outside Marco-environment of herbal tea beverage industry and major competitors of brands inside the herbal tea market. Based on the theoretic framework, this paper takes WONG LO KAT and JIA DUO BAO herbal tea as an example, and researches the strategy on brand positioning and relevant marketing mix of it. Through analysis on the prevention sense of WONG LO KAT herbal tea, it was positioned the beverage that can prevent excessive internal heat in body, a new category divided from the beverage market. the process of brand positioning of it in Consumers brain was finished. Based on this positioning strategy, WONG LO KAT reasonably organized and arranged its product strategy, price strategy, distribution strategy and promotion strategy, which not only served for and further consolidated the position of preventing excessive internal heat in body, but also elevated the value of brand. The JDB and WONG LO KAT market competition brings us enlightenment. Reference the successful experience from the JDB and lessons from the failure of the WONG LO KAT.【摘要】本文是对凉茶饮料的宏观环境以及凉茶市场内部主要品牌的竞争对手进行了系统分析。

外文翻译及外文原文参考格式

外文翻译要求:1、外文资料与毕业设计(论文)选题密切相关,译文准确、质量好。

2000的共字符左右)的外文资料,完成2篇不同文章、阅读22篇幅以上(10000 汉字以上的英译汉翻译。

严禁采用专业外国作者可以由指导教师提供,外文资料原则上应是3、外文资料外语教材文章。

插图、排序:“一篇中文译文、一篇外文原文、一篇中文译文、一篇外文原文”4 内文字及图名也译成中文。

与论文格式要求相同。

5、标题与译文格式(字体、字号、行距、页边距等)下页附:外文翻译与原文参考格式英文翻译黑体、四号、顶格()外文原文出处:)(译文前列出外文原文出处、作者、国籍,译文后附上外文原文 .CHAPTER3 .SYSTEM Practices for ammonia —Refrigeration》《ASHRAE Handbook System Selection 3.1Equipment3.2外文翻译的标题与译Reciprocating Compressors3.10 字号文中的字体页边距等与论文距、式相同。

章氨制冷系统的实施第3 3.1 系统选择)在选择一个氨制冷系统设计时,须要考虑一些设计决策要素,包括是否采用(1)液体再64)直接蒸发(5)满液式()多级压缩(单级压缩(2)带经济器的压缩(3 7循环()载冷剂。

单级压缩系统基本的单级压缩系统由蒸发器、压缩机、冷凝器、储液器(假如用的话)和制冷剂手册——“原理篇”中的第一章讨论控制装置(膨胀阀、浮球阀等)。

1997 ASHRAE了压缩制冷循环。

图1.壳管式经济器的布置文件可采用外文原文有PDF 文件直接插入。

PDF英文原文)(黑体、四号、顶格2英文翻译(黑体,四号,顶格)外文原文出处:(黑体,四号,顶格)Lecturer, Concrete Beams. Reinforced and Post-tensioned Models P. Fanning. Nonlinear ofDepartment of Civil Engineering, University College Dublin. Received 16 Jul 2001.非线形模型钢筋和后张法预应力混凝土梁商业有限元软件一般包括混凝土在荷载做用下非线性反应的专用数值模型。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

毕业设计(论文)外文资料翻译系别:电子信息系专业:通信工程班级:B100309姓名:张杨学号: B外文出处:附件: 1. 原文; 2. 译文2014年03月An Introduction to the ARM 7 ArchitectureTrevor Martin CEng, MIEETechnical DirectorThis article gives an overview of the ARM 7 architecture and a description of its major features for a developer new to the device. Future articles will examine other aspects of the ARM architecture.Basic CharacteristicsThe principle feature of the ARM 7 microcontroller is that it is a register based load-and-store architecture with a number of operating modes. While the ARM7 is a 32 bit microcontroller, it is also capable of running a 16-bit instruction set, known as "THUMB". This helps it achieve a greater code density and enhanced power saving. While all of the register-to-register data processing instructions are single-cycle, other instructions such as data transfer instructions, are multi-cycle. To increase the performance of these instructions, the ARM 7 has a three-stage pipeline. Due to the inherent simplicity of the design and low gate count, ARM 7 is the industry leader in low-power processing on a watts per MIP basis. Finally, to assist the developer, the ARM core has a built-in JTAG debug port and on-chip "embedded ICE" that allows programs to be downloaded and fully debugged in-system.In order to keep the ARM 7 both simple and cost-effective, the code and data regions are accessed via a single data bus. Thus while the ARM 7 is capable of single-cycle execution of all data processing instructions, data transfer instructions may take several cycles since they will require at least two accesses onto the bus (one for the instruction one for the data). In order to improve performance, a three stage pipeline is used that allows multiple instructions to be processed simultaneously.The pipeline has three stages; FETCH, DECODE and EXECUTE. The hardware of each stage is designed to be independent so up to three instructions can be processed simultaneously. The pipeline is most effective in speeding up sequential code. However a branch instruction will cause the pipeline to be flushed marring its performance. As we shall see later the ARM 7 designers had some clever ideas to solve this problem.InstructionFig 1 ARM 3- Stage pipelineARM7 Programming ModelThe programmer's model of the ARM 7 consists of 15 user registers, as shown in Fig. 3, with R15 being used as the Program Counter (PC). Since the ARM 7 is a load-and- store architecture, an user program must load data from memory into the CPU registers, process this data and then store the result back into memory. Unlike other processors no memory to memory instructions are available.M1M2M34,R 1,R 2 (R 4=R 0+R 2)3Fig 2 Load And Store ArchitectureAs stated above R15 is the Program Counter. R13 and R14 also have special functions; R13 is used as the stack pointer, though this has only been defined as a programming convention. Unusually the ARM instruction set does not have PUSH and POP instructions so stack handling is done via a set of instructions that allow loading and storing of multiple registers in a single operation. Thus it is possible to PUSH or POP the entire register set onto the stack in a single instruction. R14 has special significance and is called the "link register". When a call is made to a procedure, the return address is automatically placed into R14, rather than onto a stack, as might be expected. A return can then be implemented by moving the contents of R14 into R15, the PC. For multiple calling trees, the contents of R14 (the link register) must be placed onto the stack.15 User registers +PCR13 is used as the stack pointer R14 is the link registerR14 is the Program Counter Current Program Status RegisterFig 3 User Mode Register ModelIn addition to the 16 CPU registers, there is a current program status register (CPSR). This contains a set of condition code flags in the upper four bits that record the result of a previous instruction, as shown in Fig 4. In addition to the condition code flags, the CPSR contains a number of user-configurable bits that can be used to change the processor mode, enter Thumb processing and enable/disable interrupts.31 30 29 28 27Negative Carry OverflowIRQ System UserUndefined instruction AbortThumb instruction setFig 4 Current Program Status Register and Flags Exception And Interrupt ModesThe ARM 7 architecture has a total of six different operating modes, as shown below. These modes are protected or exception modes which have associated interrupt sources and their own register sets.User: This mode is used to run the application code. Once in user mode the CPSR cannot be written to and modes can only be changed when an exception is generated.FIQ: (Fast Interrupt reQuest) This supports high speed interrupt handling. Generally it is used for a single critical interrupt source in a systemIRQ: (Interrupt ReQuest) This supports all other interrupt sources in a system Supervisor: A "protected" mode for running system level code to access hardware or run OS calls. The ARM 7 enters this mode after resetAbort: If an instruction or data is fetched from an invalid memory region, an abort exception will be generatedUndefined Instruction: If a FETCHED opcode is not an ARM instruction, an undefined instruction exception will be generated.The User registers R0-R7 are common to all operating modes. However FIQ mode has its own R8 -R14 that replace the user registers when FIQ is entered. Similarly, each of the other modes have their own R13 and R14 so that each operating mode has its own unique Stack pointer and Link register. The CPSR is also common to all modes. However in each of the exception modes, an additional register一the saved program status register (SPSR),is added. When the processor changes the current value of the CPSR stored in the SPSR,this can be restored on exiting the exception mode.System&User FIQ Supervisor Abort IRQ Undefined Fig 5 Full Register Set For ARM 7Entry to the Exception modes is through the interrupt vector table. Exceptions in the ARM processor can be split into three distinct types.(i) Exceptions caused by executing an instruction, these include software interrupts, undefined instruction exceptions and memory abort exceptions(ii) Exceptions caused as a side effect of an instruction such as a abort caused by trying to fetch data from an invalid memory region.(iii) Exceptions unrelated to instruction execution, this includes reset, FIQ and IRQ interrupts.In each case entry into the exception mode uses the same mechanism. On generation of the exception, the processor switches to the privileged mode, thecurrent value of the PC+4 is saved into the Link register (R14) of the privileged mode and the current value of CPSR is saved into the privileged mode's SPSR. The IRQ interrupts are also disabled and if the FIQ mode is entered, the FIQ interrupts are also disabled, Finally the Program Counter is forced to the exception vector address and processing of the exception can start. Usually the first action of the exception routine will be to push some or all of the user registers onto the stack.Prefetch Abort(instruction fetch memory abort)Software interrupt (SWI)Undefined instruction ResetData Abort (data access momory abort)IRQ (interrupt)FIQ (fast interrupt)Supervisor Undefined Supervisor Abort Abort IRQ FIQ0x000000000x0000001C0x000000040x0000000C 0x000000080x000000100x00000018Fig 6 ARM 7 Vector TableA couple of things are worth noting on the vector table. Firstly, there is a missing vector at 0x000000014. This was used on an earlier ARM architecture and is left empty on ARM 7 to allow backward compatibility. Secondly, the FIQ interrupt is at the highest address so the FIQ routines could start from this address, removing the need for a jump instruction to reach the routine. It helps make entry into the FIQ routine as fast as possible.Once processing of the exception has finished, the processor can leave the privileged mode and return to the user mode. Firstly the contents of any registers previously saved onto the stack must be restored. Next the CSPR must be restored from the SPSR and finally the Program Counter is restored by moving the contents of the link register to R15, . the Program Counter). The interrupted program flow can then restart.Data TypesThe ARM instruction set supports six data types namely 8 bit signed and unsigned, 16 bit signed and unsigned plus 32 bit signed and unsigned. The ARM processor instruction set has been designed to support these data types in Little or Big-endian formats. However most ARM silicon implementations use the Little-endian format. ARM instructions typically have a three-operand format, as shown below ADD Rl ,R2, R3 ; Rl=R2+R3ARM7 Program Flow ControlIn all processors there is a small group of instructions that are conditionally executeddepending on a group of processor flags. These are branch instructions such as branch not equal. Within the ARM instruction set, all instructions are conditionally executable.31 28CONDFig. 7 Instruction Condition Code BitsThe top four bits of each instruction contain a condition code that must be satisfied if the instruction is to be executed. This goes a long way to eliminating small branches in the program code and eliminating stalls in the pipeline so increasing the overall program performance. Thus for small conditional branches of three instructions or less, conditional execution of instructions should be used. For larger jumps, normal branching instructions should be used.Fig. 8 Instruction Condition CodesThus our ADD instruction below could be prefixed with a condition code, as shown. This adds no overhead to instruction executionEQADD R1,R2,R3 ;If(Zero flag = 1)then R1 = R2+R3The ARM7 processor also has a 32-bit barrel shifter that allows it to shift or rotate one of the operands in a data processing instruction. This takes place in the same cycle as the instruction. The ADD instruction could be expanded as followsEQADD R1,R2 R3,LSL #2 ; If ( Zero flag = 1) then R1 = R2+ (R3 x 4)Finally the programmer may decide if a particular instruction can set the condition code flags in the CPSR.EQADDS R1,R2 R3,LSL #2; If (Zero flag = 1) then R1 = R2 + (R3 x4)and set condition code flagsIn the ARM instruction set there are no dedicated call or return instructions. Instead these functions are created out of a small group of branching instructions.The standard branch (B) instruction allows a jump of around+-32Mb. A conditional branch can be formed by use of the condition codes. For example, a "branch not equal" would be the branching instruction B and the condition code "NE" for not equal giving "BNE". The next form of the branch instruction is the branch with link. This is the branch instruction but the current value of the PC +4 is saved into R14, the link register. This acts as a CALL instruction by saving the return address into R14. A return instruction is not necessary since a return can be implemented by moving R14 into the PC. The return is more complicated in the case of an interrupt routine. Depending on the type of exception, it may be necessary to modify the contents of the link register to get the correct return address. For example, in the case of an IRQ or FIQ interrupt, the processor will finish its current instruction, increment the PC to the next instruction and then jumping to the vector table. This means that the value in the link register is PC+4 or one instruction ahead of the return address. This means we need to subtract 4 from the value in the link register to get the correct return address.This can be done in a single instruction thus:SUBS pc, r14,#40x80000x400PC=0x80000x4000x8000Both thebranch and branch-with-link may perform an exchange between 32-bit and 16-bit instruction sets and vice versa .The Branch exchange will jump to a location and start to execute 16-bit Thumb instructions. Branch link exchange will jump to a location, save PC+4 into the linkregister and start execution of 16-bit Thumb instructions. In both cases, the T bit is set in the CPSR. An equivalent instruction is implemented in the Thumb instruction set to return to 32-bit ARM instruction processing.0x8000T=1Y=10x4000x4000x8000Fig. 10 Branch Exchange and Branch Link Exchange Instruction OperationSoftware InterruptsThe ARM instruction set has a software interrupt instruction. Execution of this instruction forces an exception as described above; the processor willenter supervisor mode and jump to the SWI vector at 0x00000008.Fig. 11 Software Interrupt InstructionThe bit field 0-23 of the SWI instruction is empty and can be used to hold an ordinal. On execution of an SWI instruction, this ordinal can be examined to determine which SWI procedure to run and gives over 16 million possible SWI functions.…Swi_ #1 . call swi function one…Tn the swi handlerregister unsigned*link ptr asm ("r14");In order to access OS calls or SFR registers, the user code must make a SWI call . All these functions are the running in a supervisor mode, with a separate stack and link register.As well as instructions to transfer data to and from memory and to CPU registers, the ARM 7 has instructions to save and load multiple registers. It is possible to load or save all 16 CPU registers or a selection of registers in a single instruction. Needless to say, this is extremely useful when entering or exiting a procedure.M0Fig. 12 Load and Store Multiple Instruction OperationThe CPSR and SPSR are only accessed by two special instructions to move their contents to and from a CPU register. No other instruction can act on them directly.MSRR15R15Fig. 13 Programming The SPSR And CPSR RegistersTHUMB SupportThe ARM processor is capable of executing both 32-bit (ARM) instructions and 16- Bit (Thumb instructions). The Thumb instruction set must always be entered by running a Branch exchange or branch link exchange instruction and NOT by setting the T bit in the CPSR. Thumb instructions are essentially a mapping of their 32 bit cousins but unlike the ARM instructions, they are unconditionally executed except though for branch instructions.Fig. 14 Thumb Instruction ProcessingThumb instructions reduced number of only have unlimited access to registers RO-R7 and R13一Rl5. A instructions can access the full register set.Thumb programmers modelThe Thumb instruction set has the same load and store multiple instructions as ARM and in addition, has a modified version of these instructions in the form of PUSH and POP that implement a full descending stack in the conventional manner. The Thumb instruction set also supports the SWI instruction, except that the ordinal field is only 8 bits long to support 256 different SWI calls. When the processor is executing Thumb code and an exception occurs, it will switch to ARM mode in order to process the exception. When the CPSR is restored the, Thumb bit will be reset and the processor continues to run Thumb instructions.BCXBXThumb Exception ProcessingThumb has a much higher code density than ARM code, needing some 70% of the space of the latter. However in a 32-bit memory, ARM code is some 40% faster than Thumb. However it should be noted that if you only have 16-bit wide memory then Thumb code will be faster than ARM code by about 45%. Finally the other important aspect of Thumb is that it can use up to 30% less power than ARM code.ARM7的体系结构介绍 特里沃马丁曾,鼠技术总监本文给出了ARM 7架构的概述和开发新的设备,以及主要功能的描述,未来将研究ARM 体系结构的其他方面。