Synopsys工具简介(1)

舍不得说的PDF文件:Synopsys OptSim工具介绍说明书

DATASHEET Overview The Synopsys OptSim tool is an award-winning photonic integrated circuit and fiber-optic system simulator. With state-of-the-art time- and frequency-domain split-step algorithms, OptSim provides engineers around the globe with a native photonic-domain environment to design and optimize photonic circuits and systems. OptSim can be used as a standalone solution with its own graphical user interface (Windows and Linux), or integrated into the OptoCompiler Photonic IC design platform (Linux). When used as an OptoCompiler-integrated simulator, OptSim:•Supports electro-optic (E-O) co-simulation with Synopsys PrimeSim HSPICE and PrimeSim SPICE electrical circuit simulators •Integrates seamlessly with the PrimeWave Design Environment for advanced simulation, analyses, and visualization including parametric scans, Monte Carlo and corner analyses •Provides single- and multimode fiber-optic system modeling capabilities.When used as a standalone simulator, OptSim’s GUI provides functionalities of schematic entry, simulation setup, and visualization.Introduction Photonic integration is an answer to the ever-increasing demands for more bandwidth, better energy efficiency, smaller footprint, and improved reliability. The adaptation of photonic ICs (PICs) is rapidly growing acrossindustry segments such as telecom, data centers, optical interconnects,automotive, sensing, aerospace & defense, artificial intelligence (AI), andphotonic computing. PICs are becoming complex and the component count isincreasing at a rapid pace. Co-packaged optics (CPO) and xPU I/O are drivingmore complex trade-offs between electronics and photonics. Gone are the dayswhen it was sufficient to model photonics on the back of an envelope, withsome homegrown code, or as electronics in electrical circuit simulators. WithOptSim, you use the most comprehensive optical simulator with the industry’sbest electrical circuit simulators on the respective portions of the design withinthe OptoCompiler platform.Features at a Glance•E lectronic-photonic co-design via Synopsys PrimeSim HSPICE and PrimeSim SPICE•Simulation of single and multimode fiber optic systems and photonic integrated circuits•Seamless integration with OptoCompiler and PrimeWave Design Environment•Extensive libraries of photonic andelectronic components and analysistools•Support for numerous foundryprocess design kits (PDKs)•Support for custom photonics (PDKsand devices) via Photonic DeviceCompiler•Support for hierarchical design and bidirectional signal flow•Design for manufacturing via MonteCarlo and corner analyses OptSim Electro-Optic Co-Simulation of Photonic Integrated Circuits and Fiber-Optic SystemsDesigning single- and multimode fiber-optic systems requires capabilities to support advanced intensity- and phase-modulation for both single- and multi-channel transmission with direct and coherent detection. The interplay of polarization-dependent transmission impairments with noise, crosstalk, and multi-path interference (MPI) can create challenges to the channel capacity. In addition to PIC modeling capabilities, OptSim provides rich libraries of components and powerful analyses options to facilitate the design of a diverse range of system applications such as coherent telecom systems, RF-over-fiber, high-speed Ethernet, passive-optical-networks, and free-space optics.Figure 1: Photonic and electronic circuit and system simulation from the OptoCompiler cockpitFeatures•Works with foundry model libraries and provides a complete library of generic model templates of integrated photonics devices, enabling engineers to tailor models to measured behavior. In addition to supporting PIC design models and features, OptSim provides a rich library of single- and multimode fiber-optic system design models to support testing a PIC at the system levelFigure 2: The OptSim library includes electrical and photonic models to simulate circuits and systems•Models bidirectional signal flow for both optical (single- and multi-wavelength) and electrical signals•Models multipath interference (MPI), reflections, and resonances from network and PIC devices•Supports Monte Carlo and corner analyses•Supports simulation of design hierarchies•Supports measurement- and datafile-driven modeling of active and passive photonic components, electroniccomponents, and circuits•Supports custom design, combining foundry models and custom devices•Co-simulation with PrimeSim HSPICE and PrimeSim SPICE enables simulation of electronics in the PIC using industry-leading electrical circuit simulators together with the simulation of photonic circuits in OptSimFigure 3: Co-simulating electronic and photonic circuits in OptSim•OptSim is integrated with the Synopsys PrimeWave Design Environment, for both electrical and photonic netlists allowing setup of test benches, specifying simulation engine and parameters, performing scans and analyses for both electrical, photonic, and combined schematicsFigure 4: Setting up a testbench and simulation in PrimeWave Design Environment•OptSim results and waveforms (logical, electrical, and optical) can be viewed in both the PrimeWave Design Environment WaveView and OptSim Viewer©2021 Synopsys, Inc. All rights reserved. Synopsys is a trademark of Synopsys, Inc. in the United States and other countries. A list of Synopsys trademarks isavailable at /copyright .html . All other names mentioned herein are trademarks or registered trademarks of their respective owners.Figure 5: OptSim: Viewing simulation waveforms in PrimeWave Design Environment WaveView•Standalone OptSim (Windows, Linux) has its own graphical user interface and provides an intuitive simulation experienceFigure 6: OptSim GUI: Simulation of a PAM4 fiber-optic systemApplications:•Single- and multi-stage PICs for photonic computing, optical neural networks, life sciences, photonic sensor PICs •Segmented-electrode (SE) and traveling-wave Mach-Zehnder modulators (TW-MZM), optical filters, ring resonators,ring modulators•Transceivers for coherent and non-coherent fiber optic communication systems (such as NRZ, RZ, m-PAM, BPSK, QPSK,m-QAM, and OFDM)•Single- and multimode fiber-optic systems and circuits•Free-space optics, RF-over-fiber: Intermodulation distortion (IMD), dynamic range, sensitivity•Datacenter and automotive interconnects•Photonic systems with multipath interference (MPI), reflections, and resonancesPlatform Support•Linux: Red Hat Enterprise (64-bit), CentOS (64-bit)•Windows (64-bit): Standalone OptSim。

SYNOPSYS

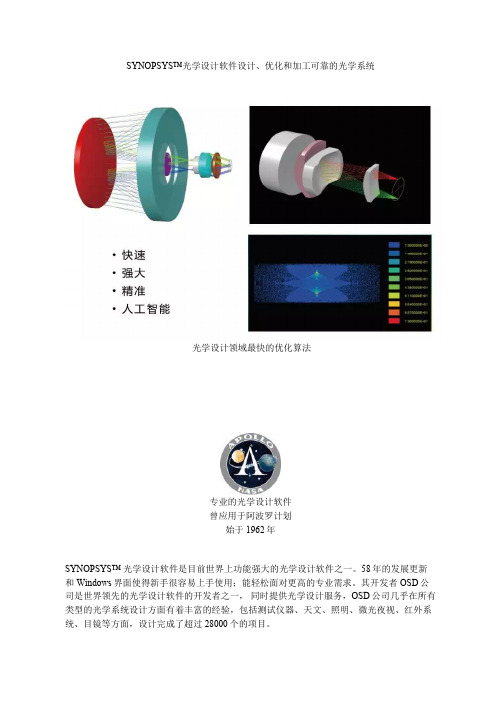

SYNOPSYS™光学设计软件设计、优化和加工可靠的光学系统光学设计领域最快的优化算法专业的光学设计软件曾应用于阿波罗计划始于1962年SYNOPSYS™ 光学设计软件是目前世界上功能强大的光学设计软件之一。

58年的发展更新和Windows界面使得新手很容易上手使用;能轻松面对更高的专业需求。

其开发者OSD公司是世界领先的光学设计软件的开发者之一,同时提供光学设计服务,OSD公司几乎在所有类型的光学系统设计方面有着丰富的经验,包括测试仪器、天文、照明、微光夜视、红外系统、目镜等方面,设计完成了超过28000个的项目。

光刻镜头从1976年以来,全球的用户已成功地利用SYNOPSYS™设计研制了大量镜头,受到广大客户的肯定和好评。

SYNOPSYS™可以分析优化各种各样的复杂光学系统。

支持多种特殊光学面如衍射光学元件、复杂非球面、自由曲面设计、各种变焦镜头,扫描系统。

很容易实现元件的偏心和倾斜;广角镜头非球面相机镜头美国Optical Systems Design(LLC简称OSD),作为一个光学设计服务和软件开发商,五十多年来一直孜孜不倦地在时间范围内推动创新光学技术的发展。

目前OSD公司是世界最大的光学设计软件供应商,发展了国际领先的光学设计软件——SYNOPSYS™光学设计软件。

客户遍布全世界25个国家和地区。

OSD公司可以快速有效地解决用户的设计需求、概念发展或方案开发、详细的镜头设计、公差分析、技术性能分析(包括衍射效应,通过Monte-Carlo 分析公差预算影响);建立的透镜系统会自动匹配首选供应商的光学样本列表,从而降低加工成本和加快设计加工进程。

反射式系统--------------------------------------初始结构:专利文件和优良设计起始点:专家系统工具XSYS可以存储并使用来自设计良好的光学结构。

输入所要设计的系统的使用波长、相对孔径、视场等参数,软件即可从自带的镜头库中找出对应的结构以供选择。

SynopsysDesignCompiler使用

SynopsysDesignCompiler使⽤Synopsys Design Compiler使⽤⼀、介绍:美国Synopsys公司发布的“Design Compiler”软件,简称“DC”,是⼀种逻辑合成⼯具。

通过改进电路延迟时间的计算⽅法,缩⼩了逻辑合成时的时序与布局完成后的最终时序之间的偏差。

DC得到全球60多个半导体⼚商、380多个⼯艺库的⽀持。

据最新Dataquest的统计,Synopsys的逻辑综合⼯具占据91%的市场份额。

DC是⼗⼆年来⼯业界标准的逻辑综合⼯具,也是Synopsys最核⼼的产品。

它使IC设计者在最短的时间内最佳的利⽤硅⽚完成设计。

它根据设计描述和约束条件并针对特定的⼯艺库⾃动综合出⼀个优化的门级电路。

它可以接受多种输⼊格式,如硬件描述语⾔、原理图和⽹表等,并产⽣多种性能报告,在缩短设计时间的同时提⾼设计性能。

⼆、要求:由于实训没有硬性要求VHDL⽂件,本⼈挑选了已经预先做好的洗⾐机时控电路,利⽤Synopsys Design Compiler⼯具,进⾏优化分析,通过这⼀过程熟悉软件的使⽤。

三、过程:设置优化运⾏库,鉴于⽼师在练习⼿册上⾯提供的例⼦,我们使⽤库LSI-10K,因此在打开VHDL⽂件前,需要作以下设置Setup->Defaults,填⼊以下信息。

在File->read打开要分析优化的VHDL⽂件,这⾥我选择⼀个洗⾐机时控电路NewWasher.vhd 如下所⽰(分别为不同层次的视图:顶层、器件、门级电路)在Tools->Design Optimization中设置好兼顾平衡的约束条件(左图),确定编译后,产⽣了右边经过优化的门级电路图。

接下来,把优化过的图形转换为VHDL⽂件和DB⽂件输出,另存到指定位置File->Save As如右图,⽣成了新的DB⽂件和vhd⽂件。

接下来,是要设定CLK的周期,根据分析、优化、编译出来的Slack Time 松弛数值和Area⾯积数值,选取最合适的平衡点。

IC设计常用软件介绍

IC设计常用软件介绍下出按用途对IC设计软件作一些介绍。

IC设计工具很多,其中按市场所占份额排行为Cadence、Mentor Graphics和Synopsys。

这三家都是ASIC设计领域相当有名的软件供应商。

其它公司的软件相对来说使用者较少。

(1)物理验证工具物理验证工具包括版图设计工具、版图验证工具、版图提取工具等等。

这方面Cadence也是很强的,其Dracula、Virtuso、Vampire等物理工具有很多的使用者。

(2)模拟电路仿真器前面讲的仿真器主要是针对数字电路的,对于模拟电路的仿真工具,普遍使用SPICE,这是唯一的选择。

只不过是选择不同公司的SPICE,像MiceoSim的PSPICE、Meta Soft的HSPICE等等。

HSPICE现在被Avanti公司收购了。

在众多的SPICE 中,最好最准的当数HSPICE,作为IC设计,它的模型最多,仿真的精度也最高。

(3)布局和布线在IC设计的布局布线工具中,Cadence软件是比较强的,它有很多产品,用于标准单元、门阵列已可实现交互布线。

最有名的是Cadence spectra,它原来是用于PCB布线的,后来Cadence把它用来作IC的布线。

其主要工具有:Cell3,Silicon Ensemble—标准单元布线器;Gate Ensemble—门阵列布线器;Design Planner—布局工具。

其它各EDA软件开发公司也提供各自的布局布线工具。

(4)综合工具综合工具可以把HDL变成门级网表。

这方面Synopsys工具占有较大的优势,它的Design Compile是作综合的工业标准,它还有另外一个产品叫Behavior Compiler,可以提供更高级的综合。

另外最近美国又出了一家软件叫Ambit,说是比Synopsys 的软件更有效,可以综合50万门的电路,速度更快。

今年初Ambit被Cadence公司收购,为此Cadence放弃了它原来的综合软件Synergy。

Synopsys

AS I C门 , 结合 P r o t o C o mp i l e r 设 计 自动 化 和 调 试 软 件 , 可 支持高达 1 6亿 个 AS I C 门 的设 计 。 HAP S硬 件 与 P r o t o — C o mp i l e r 软 件 的结 合 , 极 大 地 加 速 了软 件 开 发 、 硬 件/ 软 件 集 成 和 系统 验 证 。 P r o t o C o mp i l e r 软 件 内 置 HAP S系 统 架 构 的 知 识 , 与

卓越性 能 , 同 时配 备 有 双 存储 区 的现 场 升级 闪存 ( 高 达

2 MB ) 、 大 容量 RAM( 5 1 2 KB ) 以及 在 整个 P I 口 2产 品组合 中

F P GA 的原 型 系 统 , 该 系统 为 S y n o p s y s的 端 到 端 原 型 解 决 方 案 的一 部 分 。HAP S一8 0系 统 提 供 了 高 达 1 0 0 M Hz

的执行引擎 ; 用于创建 、 分 析 图形 和 网 络 并 实 现 可 视 化 的

At me l 低 功 耗 蓝 牙 智 能 解 决 方 案 批 量 上 市

At me l 推 出 低 功 耗 和 小 封 装 的 量 产 型 Bl u e t o o t 用 于 增 加 社 区 创 作

S AMA5 D 2拓 展 了 At me l S AMA5系 列 产 品 , 为 需 要 入 门级 MP U 和 更 广工 业 级温 度 范 围 ( 环境 温 度 ~4 O ~ 1 0 5℃ ) 的 应 用 提 供 了 极 佳 的 性 价 比 。 对 于 使 用 基 于 ARM9 2 6的 MP U 的设 计 人 员 , 其 追 求 更 高 性 能 以 及 包 括 低功 耗 、 更 高安 全 性 、 DDR3支 持 、 更 小尺 寸、 音频、 US B

synopsys dc

Synopsys dc1.1 什么是DC?DC(Design Compiler)是Synopsys的logical synthesis优化工具,它根据design description和constraints自动综合出一个优化了的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和netlist等,并产生多种性能报告,在缩短设计时间的同时提高读者设计性能。

1.2 DC能接受多少种输入格式?支持.db, .v, .vhd , edif, .vgh等等,以及.lib等相关格式。

1.3 DC提供多少种输出格式?提供.db, .v, .vhd, edif, .vgh等,并可以输出sdc, .sdf等相关格式文件。

1.4 DC的主要功能或者主要作用是什么?DC是把HDL描述的电路综合为跟工艺相关的门级电路。

并且根据用户的设计要求,在timing和area,timing和power上取得最佳的效果。

在floorplanning和placement和插入时钟树后返回DC进行时序验证1.5 如何寻找帮助?帮助可以用3种求助方式:1. 使用SOLD,到文档中寻求答案2. 在命令行中用man+ DC命令3. 在命令行中用info+ DC命令1.6 如何找到SOLD文档?SOLD文档可以在teminal中输入sold&执行。

$> sold&或者用命令which dc_shell找到dc的安装目录。

找到online目录。

1.7 如何配置DC?综合设置提供必要的参数给DC,使工具能够知道进行综合时所需要的必要的信息,即重要参数:工艺库,目标库,标志库等等。

要在.synopsys_dc.setup上设置好这些参数。

而.synopsys_dc.setup要在三个目录下有说明,一个是synopsys的安装目录,一个是用户文件夹,最后一个是工程目录。

由后一个设置覆盖前一个文件。

参数包括:search_path, target_library, link_library, symbol_library1.8 target_library 是指什么?target_library是在synthesis的map时需要的实际的工艺库1.9 link_library如何指定?链接时需要的库,通常与library相同,设置时,需要加“*”,表示内存中的所有库。

Synopsys系列工具简介

Synopsys系列工具简介Synopsys的产品线覆盖了整个IC设计流程,使客户从设计规范到芯片生产都能用到完备的最高水平设计工具。

公司主要开发和支持基于两个主要平台的产品,Galaxy设计平台和Discovery验证平台。

这些平台为客户实现先进的集成电路设计和验证提供了整套综合性的工具。

Synopsys解决方案包括:System Creation(系统生成)System Verification and Analysis(系统验证与分析)Design Planning(设计规划)Physical Synthesis(物理综合)Design for Manufacturing(可制造设计)Design for Verification(可验证设计)Test Automation(自动化测试)Deep Submicron, Signal and Layout Integrity(深亚微米技术、信号与规划完整性技术)Intellectual Property and Design Reuse Technology(IP 核与设计重用技术)Standard and Custom Block Design(标准和定制模块设计)Chip Assembly(芯片集成)Final Verification(最终验证)Fabrication and Packaging(制造与封装设计工具)Technology CAD(TCAD)(工艺计算机辅助设计技术)主要包括以下工具:1.VCS (Verilog Compiled Simulator)2.DC (Design Compiler)3.ICC (IC Compiler)4.PT (PrimeTime)5.Hercules (Hercules Physical Verification)6.Star-RCXT (parasitic extraction tool)7.LEDA (LEDA Checker and LEDA Specifier)8.Formality (RTL to gate-level equivalence checking of cell-based designs)9.TetraMAX ATPG (Provides manufacturing test patterns for scan designs)1.VCS (Verilog Compiled Simulator)VCS是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言、PLI和SDF。

synopsys_formality指导手册_概述说明

synopsys formality指导手册概述说明1. 引言1.1 概述在硬件设计领域,验证是一个非常重要的环节。

在设计过程中,我们需要确保设计的正确性和可靠性。

为了实现这个目标,Formality工具被广泛应用于电子设计自动化(EDA)过程中的形式验证。

Synopsys Formality是一款强大的形式验证工具,它可以帮助我们验证两个不同层次或版本的设计之间的等效性。

通过使用Formality,我们可以有效地检查逻辑门级网表和原始RTL之间是否存在功能差异或者错误。

本指导手册将介绍Formality工具的基本概念、应用场景以及使用步骤。

你将了解到如何利用Formality进行验证,并掌握其使用方法和技巧。

1.2 文章结构本文将分为以下几个部分:- 引言:对Formality进行概述并介绍文章结构。

- 正文:详细介绍Formality工具及其相关内容。

- Formality基本概念:解释Formality中涉及到的关键概念和术语。

- Formality的应用场景:探讨使用Formality解决哪些问题以及在哪些情况下选择使用该工具。

- 使用Formality进行验证的步骤:分步骤介绍如何使用Formality进行验证。

- 结论:总结本文的主要内容,并指出Formality在硬件验证中的重要性和前景。

1.3 目的本指导手册的目的是为读者提供对于Formality工具的全面理解。

通过阅读本文,读者将能够了解Formality在形式验证中的基本概念、功能和应用场景,从而能够更好地应用该工具来提高硬件设计的准确性和可靠性。

2. 正文Formality是Synopsys公司开发的一款形式验证工具,它旨在为硬件设计工程师提供一种高效且可靠的形式验证解决方案。

Formality通过比较两个逻辑设计的等效性来进行验证,确保电路实现与规范之间不存在功能差异或逻辑错误。

Formality作为一种形式验证工具,在电路设计领域中有着广泛的应用。

Synopsys工具简介(1)

Synopsys工具简介LEDALEDA是可编程的语法和设计规范检查工具,它能够对全芯片的VHDL和V erilog描述、或者两者混合描述进行检查,加速SoC的设计流程。

LEDA预先将IEEE可综合规范、可仿真规范、可测性规范和设计服用规范集成,提高设计者分析代码的能力。

VCS TMVCS是编译型V erilog模拟器,它完全支持OVI标准的V erilog HDL语言、PLI和SDF。

VCS具有目前行业中最高的模拟性能,其出色的内存管理能力足以支持千万门级的ASIC设计,而其模拟精度也完全满足深亚微米ASIC Sign-Off的要求。

VCS结合了节拍式算法和事件驱动算法,具有高性能、大规模和高精度的特点,适用于从行为级、RTL到Sign-Off等各个阶段。

VCS已经将CoverMeter中所有的覆盖率测试功能集成,并提供V eraLite、CycleC 等智能验证方法。

VCS和Scirocco也支持混合语言仿真。

VCS和Scirocco都集成了V irsim 图形用户界面,它提供了对模拟结果的交互和后处理分析。

Scirocco TMScirocco是迄今为止性能最好的VHDL模拟器,并且是市场上唯一为SoC验证度身定制的模拟工具。

它与VCS一样采用了革命性的模拟技术,即在同一个模拟器中把节拍式模拟技术与事件驱动的模拟技术结合起来。

Scirocco的高度优化的VHDL编译器能产生有效减少所需内存,大大加快了验证的速度,并能够在一台工作站上模拟千万门级电路。

这一性能对要进行整个系统验证的设计者来说非常重要。

V eraV era验证系统满足了验证的需要,允许高效、智能、高层次的功能验证。

V era验证系统已被Sun、NEC、Cisco等公司广泛使用以验证其实际的产品,从单片ASIC到多片ASIC 组成的计算机和网络系统,从定制、半定制电路到高复杂度的微处理器。

V era验证系统的基本思想是产生灵活的并能自我检查的测试向量,然后将其结合到test-bench中以尽可能充分测试所设计的电路。

SYNOPSYS界面操作课堂(一)

有问必答——SYNOPSYS界面操作课堂(一)一、操作界面模块问题汇总1、问:SYNOPSYS 如何快捷撤销操作?答:SYNOPSYS 中的撤回操作大致分为两种:(1)文字编辑撤回操作(使用 Ctrl+Z)例如在 Editor Window 中编辑宏或者在 Command Window 中编写命令,想要撤回编辑的文字,那么同时按住 Ctrl+Z 即可撤回。

(2)对镜头做出修改,之后返回到修改之前的镜头结构(使用 Ctrl+U 或者 F3 )例如:手动或者通过命令修改了镜头的厚度,或者优化了镜头,然后想要返回之前的结构,那么只需要直接使用 Ctrl+U 或者 F3 即可。

最多可以返回至10步之前。

通过 WS 修改表面1的厚度为 5mm。

然后关闭 WS 。

接着使用 Ctrl+U 或 F3 ,则镜头结构返回到修改之前。

再次打开 WS ,表面1厚度为 4mm。

若想要再返回到修改后的镜头结构,按 Ctrl+Y 就可以了。

2、问:输入命令 MMF,得到的 MTF 曲线图为什么不是彩色的?答:在CommandWindow中输入 MSS,在其打开的对话框中,将开关 35 打开。

或者直接在 Command Window 中输入 ON 35.3、问:SYNOPSYS 怎么缩小PAD窗口?答:点击 PAD 窗口的右上角图标。

4、问:点击按钮,为什么不显示图形呢?答:如下图5、问:SYNOPSYS 输入透镜的F数在哪里设置?答:你输入了透镜的曲率半径和材料,波长,系统的焦距就定了。

你输入了 YMP1 ,然后系统的 F 数就出来了。

或者,你想要使用最后一个面控制F数,那么可使用 UMC 命令UMC 1/(2*F/#)若想对 F 数进行修改,比例,F 数变为2。

这样的话,可以新建一个宏,输入如下代码:CHGFNO 2END6、问:下图中, X 方向不能取样?答:点击 Define skew field 按钮。

7、问: ZSEARCH 是否有类似 DSEARCH 中的 USE CURRENT 功能?答:目前 ZSEARCH 中没有 USE CURRENT功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Synopsys工具简介LEDALEDA是可编程的语法和设计规范检查工具,它能够对全芯片的VHDL和V erilog描述、或者两者混合描述进行检查,加速SoC的设计流程。

LEDA预先将IEEE可综合规范、可仿真规范、可测性规范和设计服用规范集成,提高设计者分析代码的能力。

VCS TMVCS是编译型V erilog模拟器,它完全支持OVI标准的V erilog HDL语言、PLI和SDF。

VCS具有目前行业中最高的模拟性能,其出色的内存管理能力足以支持千万门级的ASIC设计,而其模拟精度也完全满足深亚微米ASIC Sign-Off的要求。

VCS结合了节拍式算法和事件驱动算法,具有高性能、大规模和高精度的特点,适用于从行为级、RTL到Sign-Off等各个阶段。

VCS已经将CoverMeter中所有的覆盖率测试功能集成,并提供V eraLite、CycleC 等智能验证方法。

VCS和Scirocco也支持混合语言仿真。

VCS和Scirocco都集成了V irsim 图形用户界面,它提供了对模拟结果的交互和后处理分析。

Scirocco TMScirocco是迄今为止性能最好的VHDL模拟器,并且是市场上唯一为SoC验证度身定制的模拟工具。

它与VCS一样采用了革命性的模拟技术,即在同一个模拟器中把节拍式模拟技术与事件驱动的模拟技术结合起来。

Scirocco的高度优化的VHDL编译器能产生有效减少所需内存,大大加快了验证的速度,并能够在一台工作站上模拟千万门级电路。

这一性能对要进行整个系统验证的设计者来说非常重要。

V eraV era验证系统满足了验证的需要,允许高效、智能、高层次的功能验证。

V era验证系统已被Sun、NEC、Cisco等公司广泛使用以验证其实际的产品,从单片ASIC到多片ASIC 组成的计算机和网络系统,从定制、半定制电路到高复杂度的微处理器。

V era验证系统的基本思想是产生灵活的并能自我检查的测试向量,然后将其结合到test-bench中以尽可能充分测试所设计的电路。

V era验证系统适用于功能验证的各个层次,它具有以下特点:与设计环境的紧密集成、启发式及全随机测试、数据及协议建模、功能代码覆盖率分析。

Physical CompilerPhysical Compiler解决0.18微米以下工艺技术的IC设计环境,是Synopsys物理综合流程的最基本的模块,它将综合、布局、布线集成于一体,让RTL设计者可以在最短的时间内得到性能最高的电路。

通过集成综合算法、布局算法和布线算法。

在RTL到GDS II的设计流程中,Physical Compiler向设计者提供了可以确保即使是最复杂的IC设计的性能预估性和时序收敛性。

Clocktree CompilerClockTree Compiler是嵌入于Physical Compiler的工具,它帮助设计者解决深亚微米IC 设计中时钟树的时序问题。

它不仅能够简化设计流程,而且可以极大的提高时钟树的质量:对于插入延时有5%-20%的改进,对时钟偏移有5%-10%的改进。

DC-Expert (Design Compiler)DC得到全球60多个半导体厂商、380多个工艺库的支持。

据最新Dataquest的统计,Synopsys的逻辑综合工具占据91%的市场份额。

DC是十二年来工业界标准的逻辑综合工具,也是Synopsys最核心的产品。

它使IC设计者在最短的时间内最佳的利用硅片完成设计。

它根据设计描述和约束条件并针对特定的工艺库自动综合出一个优化的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和网表等,并产生多种性能报告,在缩短设计时间的同时提高设计性能。

DC Ultra对于当今所有的IC设计,DC Ultra是可以利用的最好的综合平台。

它扩展了DC Expert 的功能,包括许多高级的综合优化算法,让关键路径的分析和优化在最短的时间内完成。

在其中集成的Module Compiler数据通路综合技术,DC Ultra利用同样的VHDL/V erilog流程,能够创造出又快又小的电路。

DFT CompilerDFT Compiler提供独创的“一遍测试综合”技术和方案。

它和Design Compiler、Physical Compiler系列产品集成在一起的,包含功能强大的扫描式可测性设计分析、综合和验证技术。

DFT Compiler可以使设计者在设计流程的前期,很快而且方便的实现高质量的测试分析,确保时序要求和测试覆盖率要求同时得到满足。

DFT Compiler同时支持RTL级、门级的扫描测试设计规则的检查,以及给予约束的扫描链插入和优化,同时进行失效覆盖的分析。

Power CompilerPower Compiler提供简便的功耗优化能力,能够自动将设计的功耗最小化,提供综合前的功耗预估能力,让设计者可以更好的规划功耗分布,在短时间内完成低功耗设计。

Power Compiler嵌入Design Compiler/Physical Compiler之上,是业界唯一的可以同时优化时序、功耗和面积的综合工具。

FPGA Compiler IIFPGA Compiler II是一个专用于快速开发高品质FPGA产品的逻辑综合工具,可以根据设计者的约束条件,针对特定的FPGA结构(物理结构)在性能与面积方面对设计进行优化,自动地完成电路的逻辑实现过程,从而大大降低了FPGA设计的复杂度。

FPGA Compiler II利用了特殊的结构化算法,结合高层次电路综合方法,充分利用复杂的FPGA结构将设计输入综合成为满足设计约束条件,以宏单元或LUT为基本模块的电路,可以多种格式输出到用户的编程系统中。

FPGA Compiler II为FPGA设计者提供高层次设计方法,并为IC设计者用FPGA做样片而最后转换到ASIC提供了有效的实现途径。

Prime Power动态功耗的门级仿真和分析的工具,可精确分析基于门级的设计的功耗问题,逐渐成为ASIC和对功耗要求较高的结构定制产品(袖珍计算机和通讯设备)设计者的高级解决方案PrimeTimePrimeTime是针对复杂、百万门芯片进行全芯片、门级静态时序分析的工具。

PrimeTime 可以集成于逻辑综合和物理综合的流程,让设计者分析并解决复杂的时序问题,并提高时序收敛的速度。

PrimeTime是众多半导体厂商认可的、业界标准的静态时序分析工具。

FormalityFormality是高性能、高速度的全芯片的形式验证:等效性检查工具。

它比较设计寄存器传输级对门级或门级对门级来保证它没有偏离原始的设计意图。

在一个典型的流程中,用户使用形式验证比较寄存器传输级源码与综合后门级网表的功能等效性。

这个验证用于整个设计周期,在扫描链插入、时钟树综合、优化、人工网表编辑等等之后,以便在流程的每一阶段都能在门级维持完整的功能等效。

这样在整个设计周期中就不再需要耗时的门级仿真。

将Formality和PrimeTime这两种静态验证方法结合起来,一个工程师可以在一天内运行多次验证,而不是一天或一周只完成一次动态仿真验证。

SaberSaber是Synopsys公司开发并于1987年推出的模拟及混合信号仿真软件,被誉为全球最先进的系统仿真软件,也是唯一的多技术、多领域的系统仿真产品。

与传统仿真软件不同,Saber在结构上采用硬件描述语言(MAST)和单内核混合仿真方案,并对仿真算法进行了改进,使Saber仿真速度更快、更加有效、应用也越来越广泛。

应用工程师在进行系统设计时,建立最精确、最完善的系统仿真模型是至关重要的。

Saber可同时对模拟信号、事件驱动模拟信号、数字信号以及模数混合信号设备进行仿真。

利用Synopsys公司开发的Calaversas算法,Saber可以确保同时进行的两个仿真进程都能获得最大效率,而且可以实现两个进程之间的信息交换,并在模拟和数字仿真分析之间实现了无缝联接。

Saber适用领域广泛,包括电子学、电力电子学、电机工程、机械工程、电光学、光学、水利、控制系统以及数据采样系统等等。

只要仿真对象能够用数学表达式进行描述,Saber就能对其进行系统级仿真。

在Saber中,仿真模型可以直接用数学公式和控制关系表达式来描述,而无需采用电子宏模型表达式。

因此,Saber可以对复杂的混合系统进行精确的仿真,仿真对象不同系统的仿真结果可以同时获得。

为了解决仿真过程中的收敛问题,Saber内部采用5种不同的算法依次对系统进行仿真,一旦其中某一种算法失败,Saber 将自动采用下一种算法。

通常,仿真精度越高,仿真过程使用的时间也越长。

普通的仿真软件都不得不在仿真精度和仿真时间上进行平衡。

Saber采用其独特的设计,能够保证在最少的时间内获得最高的仿真精度。

Saber工作在SaberDesigner图形界面环境下,能够方便的实现与Cadence Design System和Mentor Graphics的集成。

通过上述软件也可以直接调用Saber 进行仿真。

JupiterXT TM芯片设计者在层次化物理设计环境中完成从门级网表到布局布线收敛的重要工具,可以帮助您将Timing、Area和Power与您的设计进行匹配,JupiterXT通过下面的方法来管理和优化您的设计:1、物理版图的层次化管理2、精确的面积、寄生参数和时序估计3、层次化布局布线流程中,精确的子模块时序加载Astro TMAstro是Synopsys为超深亚微米IC设计进行设计优化、布局、布线的设计环境。

Astro 可以满足5千万门、时钟频率GHz、在0.10及以下工艺线生产的SoC设计的工程和技术需求。

Astro高性能的优化和布局布线能力主要归功于Synopsys在其中集成的两项最新技术:PhySiSys和Milkyway DUO结构。

Design Vision TMSynopsys综合环境的图形界面,在通用技术层和门级进行设计浏览和分析的分析工具。

Mars-rail TMMars-Rail用于功耗和电漂移(?)的分析和优化,以完成低功耗高可靠性的设计。

它将自动在Apollo-II的布局布线中起作用。

Mars-Rail的优点:Mars-xtalk TMMars-Xtalk可以进行充分的串扰分析,并能够进行防止串扰发生的布局和布线,解决超深亚微米芯片设计中的信号完整性问题。

CosmosLE/SE TMSynopsys的Cosmos解决方案可以进行自前向后的混合信号、全定制IC设计。

它可以很好的处理自动化的设计流程和设计的灵便性,使得设计周期可以缩短数周甚至几个月。

CosmosLE提供了一个基于Milkyway数据库的完整物理IC设计环境,同时可以无缝集成,动态交互操作所有Synopsys公司领先的物理设计工具。