时钟树_STM32中文参考手册_V10

stm32 时钟

STM32之时钟树笔记1STM32有五个时钟源:HSI、HSE、LSI、LSE、PLL1.1HSI:高速内部时钟、RC振荡器、频率为8MHz、时钟精度较差,可作为备用时钟源(时钟安全系统CSS)。

1.2HSE:高速外部时钟、可接外部晶体/陶瓷谐振器(4MHz~16MHz)或外部时钟源(HSE旁路,Max 25MHz)。

1.3LSI:低速内部时钟、RC振荡器、频率为40kHz,大容量MCU可进行LSI时钟校准。

1.4LSE:低速外部时钟、接频率为32.768kHz的外部晶体/陶瓷谐振器。

1.5PLL:锁相环倍频输出,时钟输入源可选择HSI/2、HSE或HSE/2。

倍频可选择为2~16倍,最大输出72MHz。

用户可通过多个预分频器配置AHB总线、高速APB2总线和低速APB1总线的频率。

AHB 和APB2域的最大频率是72MHZ。

APB1域的最大允许频率是36MHZ。

SDIO接口的时钟频率固定为HCLK/2。

●40kHz的LSI供独立看门狗IWDG使用,另外它还可以被选择为实时时钟RTC的时钟源。

另外,实时时钟RTC的时钟源还可以选择LSE,或者是HSE的128分频。

RTC的时钟源通过RTCSEL[1:0]来选择。

●STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。

该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

●另外,STM32还可以选择一个PLL输出的2分频、HSI、HSE、或者系统时钟输出到MCO脚(PA8)上●系统时钟SYSCLK,是供STM32中绝大部分部件工作的时钟源。

系统时钟可选择为PLL输出、HSI或者HSE,在选择时钟源前注意要判断目标时钟源是否已经稳定振荡。

Max=72MHz,它分为2路,1路送给I2S2、I2S3使用的I2S2CLK、I2S3CLK;另外1路通过AHB分频器分频(1/2/4/8/16/64/128/256/512)分频后送给以下8大模块使用:①送给SDIO使用的SDIOCLK时钟。

stm32时钟详细说明

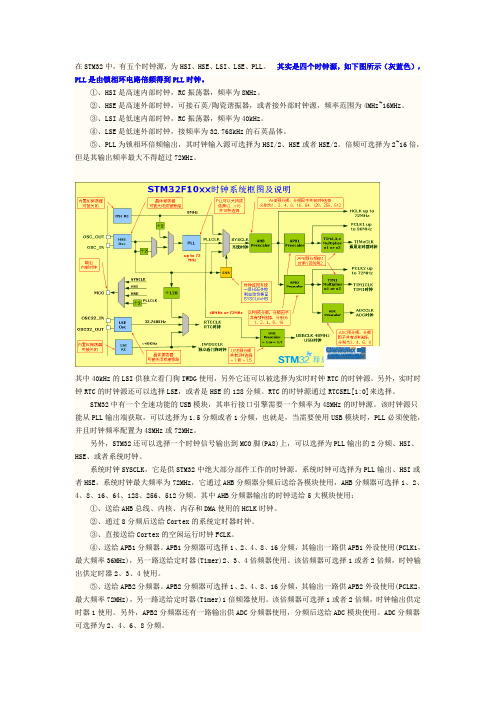

在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

其实是四个时钟源,如下图所示(灰蓝色),PLL是由锁相环电路倍频得到PLL时钟。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。

倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

其中40kHz的LSI供独立看门狗IWDG使用,另外它还可以被选择为实时时钟RTC的时钟源。

另外,实时时钟RTC的时钟源还可以选择LSE,或者是HSE的128分频。

RTC的时钟源通过RTCSEL[1:0]来选择。

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。

该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

另外,STM32还可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟。

系统时钟SYSCLK,它是供STM32中绝大部分部件工作的时钟源。

系统时钟可选择为PLL输出、HSI或者HSE。

系统时钟最大频率为72MHz,它通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。

其中AHB分频器输出的时钟送给5大模块使用:①、送给AHB总线、内核、内存和DMA使用的HCLK时钟。

②、通过8分频后送给Cortex的系统定时器时钟。

③、直接送给Cortex的空闲运行时钟FCLK。

④、送给APB1分频器。

STM32中文参考手册

9.1 DMA简介

9.2 DMA主要特性

9.3 功能描述

STM32F10xxx参考手册

75

75 75 76 76 77 77 77

78

78 78 79 79 80 80 81 82 82

83

83 83 86 86 87 87

88

89

89

89 89

91

91 92 92 92 94

108

9.4.3 DMA通道x配置寄存器(DMA_CCRx)(x = 1…7)

108

9.4.4 DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1…7)

110

9.4.5 DMA通道x外设地址寄存器(DMA_CPARx)(x = 1…7)

110

9.4.6 DMA通道x存储器地址寄存器(DMA_CPARx)(x = 1…7)

16

1.3 可用的外设

16

2 存储器和总线构架

17

2.1 系统构架

17

2.2 存储器组织

18

2.3 存储器映像

19

2.3.1 嵌入式SRAM

20

2.3.2 位段

20

2.3.3 嵌入式闪存

21

2.4 启动配置

23

3 CRC计算单元(CRC)

25

3.1 CRC简介

25

3.2 CRC主要特性

25

3.3 CRC功能描述

STM32F10xxx参考手册

38

38 39

39

39 39 40 40 42

45

45

45 45 46

46

48 48 49 49 49 50 50 50 50 50

STM32时钟树

STM32F10xx 时钟树STM32有五个时钟源,HSI RC,HSE OSC,LSI RC,LSE OSC,PLL。

实际是四个,PLL 是由锁相环电路倍频得到的。

HSI 高速内部时钟,8MHzHSE高速外部时钟,频率为4MHz~16MHzLSI 低速内部时钟,40kHzLSE低速外部时钟,32.768kHzPLL的时钟源为两个高速时钟,可选HSI/2,HSE,HSE/2,最大为72MHzOSC 为晶振,振荡器(Oscillator)引脚ˈɒsɪleɪtə(r),STM32F10xx系列处理器有两个外部时钟源,分别接OSC和OSC32引脚,前者为高速,后者为低速。

内置RC振荡器可以被关闭。

STM32有一个时钟监视系统CSS,一旦HSE失效则会自动切换至SYSTICK = HSI。

介绍完时钟源,下面介绍一下STM32每个模块分别对应哪个时钟源。

低速的:1.独立看门狗的时钟源为低速内部时钟LSI ,40kHz2.RTC时钟的时钟源可以有三个,分别为LSI,LSE或者HSE的128分频,通过RTCSEL[1:0]来选择,其中RTCSEL为RCC_CSR寄存器其中的两位。

高速的:1.全速功能的USB模块,其串行接口引擎需要一个频率为48MHz,该时钟源只能从PLL 输出端获得,可以选择1分频或者1.5分频,也就是说,当使用了USB模块,PLL必须使能,而且时钟频率需配置为48MHz或者72MHz.2.系统时钟SYSCLK,是供STM32中绝大部分部件工作的时钟源,系统时钟可选择,PLL 输出,HSI或者HSE输出,全是高速的,系统时钟最大频率为72MHz。

系统时钟并不是直接提供给各模块使用,它需要通过AHB分频器分频给各个模块使用。

AHB的分频因子有9种,1,2,4,8,16,64,128,256,512。

AHB是Advanced High performance Bus,即高级高性能总线,这是一种系统总线,主要用于高性能模块如CPU,DMA,DSP等之间的连接,AHB系统由主模块,从模块和基础结构三部分组成,整个AHB总线上的传输都是由主模块发出,从模块负责回应。

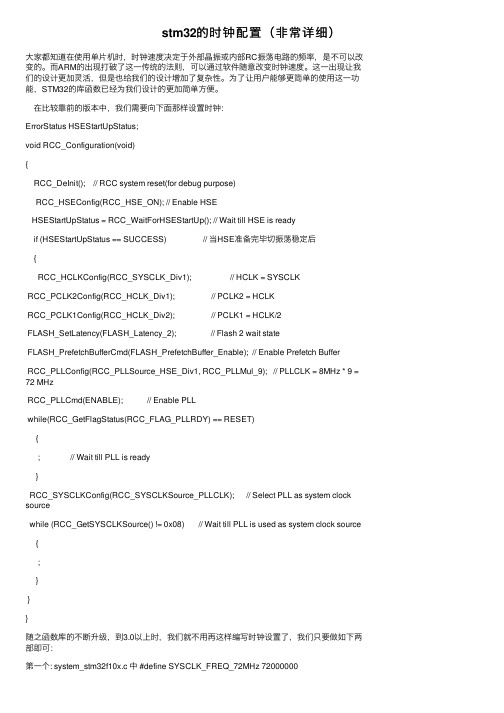

stm32的时钟配置(非常详细)

stm32的时钟配置(⾮常详细)⼤家都知道在使⽤单⽚机时,时钟速度决定于外部晶振或内部RC振荡电路的频率,是不可以改变的。

⽽ARM的出现打破了这⼀传统的法则,可以通过软件随意改变时钟速度。

这⼀出现让我们的设计更加灵活,但是也给我们的设计增加了复杂性。

为了让⽤户能够更简单的使⽤这⼀功能,STM32的库函数已经为我们设计的更加简单⽅便。

在⽐较靠前的版本中,我们需要向下⾯那样设置时钟:ErrorStatus HSEStartUpStatus;void RCC_Configuration(void){RCC_DeInit(); // RCC system reset(for debug purpose)RCC_HSEConfig(RCC_HSE_ON); // Enable HSEHSEStartUpStatus = RCC_WaitForHSEStartUp(); // Wait till HSE is readyif (HSEStartUpStatus == SUCCESS) // 当HSE准备完毕切振荡稳定后{RCC_HCLKConfig(RCC_SYSCLK_Div1); // HCLK = SYSCLKRCC_PCLK2Config(RCC_HCLK_Div1); // PCLK2 = HCLKRCC_PCLK1Config(RCC_HCLK_Div2); // PCLK1 = HCLK/2FLASH_SetLatency(FLASH_Latency_2); // Flash 2 wait stateFLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable); // Enable Prefetch BufferRCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9); // PLLCLK = 8MHz * 9 = 72 MHzRCC_PLLCmd(ENABLE); // Enable PLLwhile(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){; // Wait till PLL is ready}RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); // Select PLL as system clock sourcewhile (RCC_GetSYSCLKSource() != 0x08) // Wait till PLL is used as system clock source {;}}}随之函数库的不断升级,到3.0以上时,我们就不⽤再这样编写时钟设置了,我们只要做如下两部即可:第⼀个: system_stm32f10x.c 中 #define SYSCLK_FREQ_72MHz 72000000第⼆个:调⽤SystemInit()说明:在stm32固件库3.0中对时钟频率的选择进⾏了⼤⼤的简化,原先的⼀⼤堆操作都在后台进⾏。

stm32时钟树分析

void RCC_Configuration(void){/* RCC system reset(for debug purpose) */ RCC_DeInit();/* Enable HSE */RCC_HSEConfig(RCC_HSE_ON);/* Wait till HSE is ready */HSEStartUpStatus = RCC_WaitForHSEStartUp();if(HSEStartUpStatus == SUCCESS){/* Enable Prefetch Buffer */FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);/* Flash 2 wait state */FLASH_SetLatency(FLASH_Latency_2);/* HCLK = SYSCLK */RCC_HCLKConfig(RCC_SYSCLK_Div1);/* PCLK2 = HCLK */RCC_PCLK2Config(RCC_HCLK_Div1);/* PCLK1 = HCLK/2 */RCC_PCLK1Config(RCC_HCLK_Div2);/* PLLCLK = 8MHz * 9 = 72 MHz */RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);/* Enable PLL */RCC_PLLCmd(ENABLE);/* Wait till PLL is ready */while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){}/* Select PLL as system clock source */RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);/* Wait till PLL is used as system clock source */while(RCC_GetSYSCLKSource() != 0x08){}}}systemclock共有三个来源,上面代码最后RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);应该是选择PLLCLK为时钟源void RCC_Configuration(void){/* RCC system reset(for debug purpose) */RCC_DeInit();/* Enable HSE */RCC_HSEConfig(RCC_HSE_ON); ------------SHE外部晶振起震(8M)/* Wait till HSE is ready */HSEStartUpStatus = RCC_WaitForHSEStartUp();if(HSEStartUpStatus == SUCCESS) --------------起震成功配置,flash取指令设置{/* Enable Prefetch Buffer */FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);/* Flash 2 wait state */FLASH_SetLatency(FLASH_Latency_2);/* HCLK = SYSCLK */RCC_HCLKConfig(RCC_SYSCLK_Div1); --------------AHB总线不分频/* PCLK2 = HCLK */RCC_PCLK2Config(RCC_HCLK_Div1); --------------APB2总线不分频/* PCLK1 = HCLK/2 */RCC_PCLK1Config(RCC_HCLK_Div2); --------------APB1总线二分频/* PLLCLK = 8MHz * 9 = 72 MHz */RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9); -----PLLCLK =8MHz * 9 = 72 MHz/* Enable PLL */RCC_PLLCmd(ENABLE); --------------- PLL 使能/* Wait till PLL is ready */while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){}/* Select PLL as system clock source */RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); -------选择PLLCLK为系统时钟systemclk/* Wait till PLL is used as system clock source */while(RCC_GetSYSCLKSource() != 0x08){}}}从这里可以看到最后AHB时钟为72M(最大也是72M);APB2时钟72M(最大也是72M);APB1时钟36M(最大也是36M);所以可以得到APB2预分频系数为1;APB1预分频系数为2。

STM32技术参考手册第4章复位和时钟控制(上)

4 复位和时钟控制4.1 复位STM32F支持三种复位形式,分别为系统复位、上电复位和备份区域复位。

4.1.1 系统复位系统复位将复位除时钟控制寄存器CSR中的复位标志和备份区域中的寄存器以外的所有寄存器(见图3)。

当以下事件中的一件发生时,产生一个系统复位:1. NRST管脚上的低电平(外部复位)2. 窗口看门狗计数终止(WWDG复位)3. 独立看门狗计数终止(IWDG复位)4. 软件复位(SW复位)5. 低功耗管理复位可通过查看RCC_CSR控制状态寄存器中的复位状态标志位来确认复位事件来源。

软件复位通过将Cortex-M3中断应用和复位控制寄存器中的SYSRESETREQ位置1,可实现软件复位。

请参考Cortex技术参考手册获得进一步信息。

低功耗管理复位在以下两种情况下可产生低功耗管理复位:1. 在进入待机模式时产生低功耗管理复位:通过将用户选择字节中的nRST_STDBY位置1将使能该复位。

这时,即使执行了进入待机模式的过程,系统将被复位而不是进入待机模式。

2. 在进入停止模式时产生低功耗管理复位:通过将用户选择字节中的nRST_STOP位置1将使能该复位。

这时,即使执行了进入停机模式的过程,系统将被复位而不是进入停机模式。

关于用户选择字节的进一步信息,请参考STM32F10x闪存编程手册。

4.1.2 电源复位当以下事件中之一发生时,产生电源复位:1. 上电/掉电复位(POR/PDR复位)2. 从待机模式中返回电源复位将复位除了备份区域外的所有寄存器。

(见图3)图中复位源将最终作用于RESET管脚,并在复位过程中保持低电平。

复位入口矢量被固定在地址0x0000_0000~0x0000_0004。

图4-1.复位电路备份区域拥有两个专门的复位,它们只影响备份区域。

4.1.3 备份域复位当以下事件中之一发生时,产生备份区域复位。

1. 软件复位,备份区域复位可由设置备份区域控制寄存器RCC_BDCR中的BDRST位产生。

图文详解stm32时钟树

对于广大初次接触STM32的读者朋友(甚至是初次接触ARM器件的读者朋友)来说,在熟悉了开发环境的使用之后,往往“栽倒”在同一个问题上。

这问题有个关键字叫:时钟树。

众所周知,微控制器(处理器)的运行必须要依赖周期性的时钟脉冲来驱动——往往由一个外部晶体振荡器提供时钟输入为始,最终转换为多个外部设备的周期性运作为末,这种时钟“能量”扩散流动的路径,犹如大树的养分通过主干流向各个分支,因此常称之为“时钟树”。

在一些传统的低端8位单片机诸如51,AVR,PIC等单片机,其也具备自身的一个时钟树系统,但其中的绝大部分是不受用户控制的,亦即在单片机上电后,时钟树就固定在某种不可更改的状态(假设单片机处于正常工作的状态)。

比如51单片机使用典型的12MHz晶振作为时钟源,则外设如IO口、定时器、串口等设备的驱动时钟速率便已经是固定的,用户无法将此时钟速率更改,除非更换晶振。

而STM32微控制器的时钟树则是可配置的,其时钟输入源与最终达到外设处的时钟速率不再有固定的关系,本文将来详细解析STM32微控制器的时钟树。

图1是STM32微控制器的时钟树,表1是图中各个标号所表示的部件。

标号图1标号释义1内部低速振荡器(LSI,40Khz)2外部低速振荡器(LSE,32.768Khz)3外部高速振荡器(HSE,3-25MHz)4内部高速振荡器(HIS,8MHz)5PLL输入选择位6RTC时钟选择位7PLL1分频数寄存器8PLL1倍频寄存器9系统时钟选择位10USB分频寄存器11AHB分频寄存器12APB1分频寄存器13AHB总线14APB1外设总线15APB2分频寄存器16APB2外设总线17ADC预分频寄存器18ADC外设19PLL2分频数寄存器20PLL2倍频寄存器21PLL时钟源选择寄存器22独立看门狗设备23RTC设备图1STM32的时钟树在认识这颗时钟树之前,首先要明确“主干”和最终的“分支”。

假设使用外部8MHz 晶振作为STM32的时钟输入源(这也是最常见的一种做法),则这个8MHz便是“主干”,而“分支”很显然是最终的外部设备比如通用输入输出设备(GPIO)。