模式锁存触发电路设计任务说明习题解答

数字电路习题及解答(触发器及时序逻辑电路)

1第8章 触发器和时序逻辑电路——基本习题解答8.4如果D 触发器外接一个异或门,则可把D 触发器转换成T 触发器,试画出其逻辑图。

解:Q n +1=D=T ⊕Q n 故D =T ⊕Q n 如题8.4图所示。

题8.4.图8.5试用T 触发器和门电路分别构成D 触发器和JK 触发器。

解:(1)T 触发器构成D 触发器Q n +1=D =T ⊕Q n ∴T =D ⊕Q n 如题8.5(a )图所示。

题8.5(a )图(2)T 触发器构成JK 触发器Q n +1=n n n n Q K Q J Q T Q T +=+=T ⊕Q n ∴T =n n n n n KQ Q J Q Q K Q J +=⊕+)(如题8.5(b )图所示。

题8.5(b )图8.6逻辑电路如题8.6图(a )所示,设初始状态Q 1=Q 2=0,试画出Q 1和Q 2端的输出波形。

时钟脉冲C 的波形如题8.6图(b )所示,如果时钟频率是4000Hz ,那么Q 1和Q 2波形的频率各为多少?题8.6图(a ) 题8.6图(b )解:JK 触发器构成了T ′触发器,逻辑电路为异步加法计数,Q 1和Q 2端的输出波形如题CP228.6图(c )所示。

Q 1输出波形为CP 脉冲的二分频,Q 2输出波形为CP 脉冲的四分频。

如果CP 脉冲频率为4000Hz ,则Q 1波形的频率是2000Hz ;Q 2波形的频率是1000Hz 。

题8.6图(c )8.8试列出题8.8图所示计数器的状态表,从而说明它是一个几进制计数器。

题8.8图解:F 0:J 0=21Q Q ,K 0=1F 1:J 1=Q 0,K 1=20=Q 0+Q 2 F 2:QJ 2=K 2=1假设初态均为0,分析结果如题8.8图(a )所示,Q 2Q 1Q 0经历了000-001-010-011-100-101-110七种状态,因此构成七进制异步加法计数器。

题8.8图(a )8.9试用主从型JK 触发器组成两位二进制减法计数器,即输出状态为“11”、“10”、“01”、Q Q Q3“00”。

锁存器与触发器ppt课件.ppt

5.2 SR锁存器 SR是各种触发器的基本构成部分 一、电路结构与工作原理

图5.2.1 或非门构成的SR锁存器

’ ’

a.电路图

b.图形符号

图5.2.2 与非门构成的SR锁存器

5.2.1 SR锁存器

电路的初态与次态

VI1 1 VO1 Q 1 1

VI1 1 VO1 Q 0 0

1 VI2

G2

Q0 VO2

1 VI2

G2

Q1 VO2

3. 模拟特性分析

O1 = I2 I1 = O2

G1 VI1 1 VO1 Q

O1

e

稳态点

(dQ=1)

1 VI2

G2

Q VO2

c

介稳态

点

a

0

b 稳态点

(Q=I01)

概述

一、能用于记忆1位二进制信号的基本单元电 路统称为触发器

5)动作特点:E=1期间电路对信号敏感,并按S 、 R信号改变 锁存器的状态。

5.2.2 D 锁存器

1. 逻辑门控 D 锁存器

逻辑电路图

R

G4 & Q4

G2

≥1

E

1 G5

D S

≥1 &

Q3 G1 G3

国标逻辑符号

Q

D 1D

Q

E E1

Q

Q

该锁存器有几种工作状态?有非定义状态吗?

1. 逻辑门控 D 锁存器

逻辑功能

D 锁存器的功能表

E

R =D

G4 &

Q4

G2 ≥1

G5 1

≥1 & Q3

四人智力竞赛抢答器电路原理及设计

四人智力竞赛抢答器电路原理及设计目录一、设计目的 ..................................................................... .............................................. 2 二、设计任务与要求 ..................................................................... .. (2)1、设计任务 ..................................................................... . (2)2、设计要求 ..................................................................... . (2)三、四人智力竞赛抢答器电路原理及设计 .....................................................................31、设计方案 ..................................................................... . (3)2、系统框图 ..................................................................... . (3)3、方案比较 ..................................................................... . (4)方案1 ...................................................................... ........................................................................ . (4)方案2:...................................................................... ........................................................................ (4)方案3: ..................................................................... ........................................................................ . (4)4、单元电路设计及元器件选择 ..................................................................... (4)(1)抢答电路 ..................................................................... ........................................................................ .. (4)(2)定时电路 ............................................................................................................................................. .. (7)(3)报警电路 ..................................................................... ........................................................................ .. (9)(4)时序控制电路 ..................................................................... ......................................................................10(5)元器件列表 ..................................................................... ........................................................................ .. 125、四路抢答器总电路图 ..................................................................... ........................................... 13 四、设计过程中的问题和解决办法 ..................................................................... ......... 13 五、设计成品的优点与不足 ..................................................................... ..................... 14 六、心得体会 ..................................................................... ................................................ 14 七、实物图 ..................................................................... (15)1、正面 ..................................................................... ......................................................................152、反面 ..................................................................... ......................................................................161四人智力竞赛抢答器一、设计目的1.掌握四人智力竞赛抢答器电路的设计、组装与调试方法。

第5章--触发器-习题答案.docx

第五章触发器5.1画出如题图5.1所示的基本RS触发器输出端Q、Q的电压波形图。

宁和★的电压波形如图5.1(b) 所示。

解:波形如图:5.2或门组成的基本RS触发器电路如题图5.2(a)所示,己知S和R的波形如题图5.2(b)所示。

试画出Q、3的波形图。

设触发器的初态Q = 0。

题图解:波形如图:5.3题图5.3所示为一个防抖动输出开关电路。

当拨动开关K 时,由于开关接通瞬间发生振颤,R 和S 的波形如图中所示,请画出Q 和Q 端的对应波形。

解:波形如图: 5.4有一时钟RS 触发器如题图5.4所示,试画出它的输出端。

的波形。

初态Q =0-解:波形如图:(b题图(a) (b)题图5.45.5设具有异步端的主从JK 触发器的初始状态Q =0,输入波形如题图5.5所示,试画出输出端Q 的波形。

CLKk题图5.5解:波形如图:CLK5.6设题图5.6的初始状态为0 21 Qo =000,在脉冲CLK 作用下,画出0、0、0的波形(所用 器件都是CD4013)o S D 、R D 分别是CD4013高电平有效的异步置1端,置。

端。

题图5.6解:波形如图:I II I I II I I I(-1__L-. I I --I_L-I I —I__L-1 1 1 1 1 1 0 1 1 1 Illi 1 -J_L- 1 Illi Illi —r i i H — i i i 1(-J__L- 1 1 1 1 1 1 -Hi i /III K I 1 1 1 1 1 1 1 1 o : | | IIII IIII i -i―i - i IIII i i i U_ i i i i i ii -i —i — i i i i i i t; ; 1 1 1 1 1 01 I IIII i [ i i i i —i i—i i ii i.1 1」 1 1 1 IIII IIII IIII1 1 11 1 1 1 1 1 oljiiii i i i i iiiii i ! i i i , 1 1 1——1tnmjwwi.,r -: ~: ~: : ~: ~: ~: ~: ~: ~: ~: ~: ~: ~~: ~: t5.7设题图5.7电路两触发器初态均为0,试画出0、0波形图。

(完整版)触发器时序逻辑电路习题答案

第4章 触发器4.3 若在图4.5电路中的CP 、S 、R 输入端,加入如图4.27所示波形的信号,试画出其Q 和Q 端波形,设初态Q =0。

SRCP图4.27 题4.3图解:图4.5电路为同步RS 触发器,分析作图如下:S RQ4.5 设图4.28中各触发器的初始状态皆为Q =0,画出在CP 脉冲连续作用下个各触发器输出端的波形图。

Q 11CPQ 3CPCPQ 2Q 6Q 4Q 5CP图4.28 题4.5图解:Q Q nn 111=+ Q Q n n 212=+ Q Q nn 313=+Q Q n n 414=+ Q Q n n 515=+ Q Q nn 616=+Q 1CP Q 2Q 3Q 4Q 5Q64.6 试写出 图4.29(a)中各触发器的次态函数(即Q 1 n+1 、 Q 2 n+1与现态和输入变量之间的函数式),并画出在图4.29(b )给定信号的作用下Q 1 、Q 2的波形。

假定各触发器的初始状态均为Q =0。

1A BCP>1D C1=1A BQ 1Q 2Q 2(a)BA(b)图4.29题4.6图解:由图可见:Q B A AB Q n n 111)(++=+ B A Q n ⊕=+12B A Q 2Q 14.7 图4.30(a )、(b )分别示出了触发器和逻辑门构成的脉冲分频电路,CP 脉冲如图4.30(c )所示,设各触发器的初始状态均为0。

(1)试画出图(a )中的Q 1、Q 2和F 的波形。

(2)试画出图(b )中的Q 3、Q 4和Y 的波形。

Y(b )(c )CPQ 1Q 2(a )图4.30 题4.7图解: (a )Q Q nn 211=+ QQ nn 112=+ Q F 1CP ⊕= R 2 = Q 1 低电平有效CPQ 1Q 2F(b )Q Q Q n n n 4313=+ Q Q Q n n n 4314=+ Q Q Y nn43=CP 3= CP 上降沿触发 CP 4= CP 下降沿触发CPQ 3Q 4Y4.8 电路如图4.31所示,设各触发器的初始状态均为0。

第4章等习题答案复习过程

第4章等习题答案思考题:题4.1.1 按触发方式触发器可分为、和三类。

答:电平触发、主从触发、边沿触发。

题4.1.2 由与非门构成的RS锁存器输入信号不允许同时为。

答:0题4.1.3 触发器有个稳定状态,它可记录位二进制码,存储8位二进制信息需要个触发器。

答:2、1、8。

题4.1.4 如果由或非门构成的RS锁存器输入信号同时为1,此时输出的原端Q和非端Q为。

然后改变两输入信号为0,输出原端Q和非端Q为。

答:0、不定(0,1或1,0)题4.2.1 在图4.2.1(b)中将C1改为C2,当C2有效时,1S、1R和C2 。

答:无关。

题4.2.2 同步RS触发器和RS锁存器主要区别是。

答:触发信号。

题4.2.3 保证同步D触发器的输出稳定,要求输入有效信号的高电平至少需要。

答: 4t pd。

题4.2.4 同步触发器的缺点是。

(A)抗干扰能力差(B)空翻现象(C)多次翻转(D)约束条件答:A、B、C、D。

题4.2.5 同步D触发器和同步RS触发器相同之处是,不同之处是。

(A)空翻现象,约束条件(B)同步信号,空翻现象(C)约束条件,空翻现象(D)时钟,同步信号答: A题4.3.1 具有约束条件的触发器有。

收集于网络,如有侵权请联系管理员删除(A)主从RS触发器(B)由主从RS触发器组成D触发器(C)主从JK触发器(D)由主从JK触发器组成D触发器答:A题4.3.2 具有一次翻转特性的触发器有。

(A)主从RS触发器(B)由主从RS触发器组成D触发器(C)主从JK触发器(D)由主从JK触发器组成D触发器答:C、D题4.3.3 主从RS触发器不能完全克服多次翻转的原因是。

(A)主从RS触发器的主触发器工作原理和同步RS触发器相同(B)主从RS触发器的从触发器工作原理和同步RS触发器相同(C)输入信号R不稳定(D)异步复位或置位不考虑时钟的到来就将输出清零或置1答:A题4.3.4 主从触发器的时钟在高电平时,将输入信号传递到。

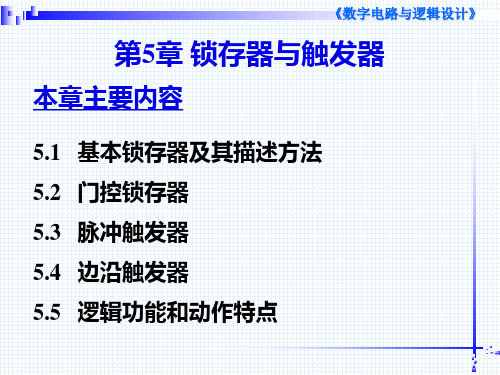

第5章 锁存器与触发器

《数字电路与逻辑设计》

3) 状态转换图与激励表

将锁存器两个状态之间的转换及其所需要的输 入条件用图形的方式表示称为状态转换图(简称为 状态图),用表格的形式表示则称为激励表。

基本SR锁存器的状态图如下图所示,表5-2为 其激励表。

表5-2 基本SR锁存器的激励表

SD=0

RD=´

0

SD=1 RD=0

《数字电路与逻辑设计》

第5章 锁存器与触发器

本章主要内容

5.1 基本锁存器及其描述方法 5.2 门控锁存器 5.3 脉冲触发器 5.4 边沿触发器 5.5 逻辑功能和动作特点

《数字电路与逻辑设计》

本章重点:

掌握锁存器与触发器的电路结构、逻辑 功能和动作特点

本章难点:

触发器的工作原理

《数字电路与逻辑设计》

此外,锁存器的功能还可以用状态转换图和激 励表表示。

《数字电路与逻辑设计》

1) 特性表(真值表) 基本锁存器的特性表如表5-1所示。

表5-1 基本SR锁存器特性表 与非门构成的锁存器 或非门构成的锁存器 SD RD Q Q* SD RD Q Q* 1 1 0 0 0000 1 1 1 1 0011 1 0 0 0 0100 1 0 1 0 0110 0 1 0 1 1001 0 1 1 1 1011 0 0 0 × 1 1 0× 0 0 1 × 1 1 1×

《数字电路与逻辑设计》

(2) CLK为高电平时, 由于SD=(S·CLK)=S、RD=(R·CLK)=R,因 此门控锁存器将根据输入信号S和R实现其相应的 功能。

将SD=S、RD=R代入到基本锁存器的特性方 程Q*=SD+RD·Q,可得到门控锁存器的特性方程为

Q*=S+R·Q

《数字电路-分析与设计》1--10章习题及解答(部分)_北京理工大学出版社

6-17先分别将‘290接为8421和5421计数器,再分别用M-1=6(QDQCQBQA=0110)8421和(QAQDQCQB=1001)5421置位即可,应特别注意高低位的顺序。波形图和状态图略。

低电平噪声容限:

甲的关门电平大,所以甲在输入低电平时的

抗干扰能力强。

3-6 试说明下列各种门电路中哪些可以将输出端并联使用(输入端的状态不一定相同)。

⑴ 具有推拉式输出级的TTL电路;

⑵ TTL电路的OCபைடு நூலகம்;

⑶ TTL电路的TS门;

⑷ 普通的CMOS门;

⑸ 漏极开路输出的CMOS门;

⑹ CMOS电路的TS门。

6-24应从RCO引出,此时不管分频比为多少,分频关系都是正确的。

6-25画出状态顺序表或状态图即可。

对于图(a),只要注意QB=0时预置,并且DCBA=QD110即可。

由状态图知,这是模6计数器。

对于图(b),只要注意QC=0时预置,并且DCBA=QD100即可。

由状态图知,这是模10计数器。

该电路设计巧妙,QD均为占空比为50%的方波。

3-5 有两个相同型号的TTL“与非”门,对它们进行测试的结果如下:

⑴ 甲的开门电平为1.4V,乙的开门电平为1.5V;

⑵ 甲的关门电平为1.0V,乙的关门电平为0.9V。

试问在输入相同高电平时,哪个抗干扰能力强?在输入相同的低电平时,哪个抗干扰能力强?

解:高电平噪声容限:

甲的开门电平小,所以甲在输入高电平时的抗干扰能力强;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

任务8.2模式锁存触发电路设计任务说明习题解答

一、测试

(一)判断题

1、移位寄存器74LS194 可串行输入并行输出,但不能串行输入串行输出。

答案:F

解题:并行送数功能。

当/CR=1,M1M0=11时,在上升沿作用下,D0~D3端输入的数码d0~d3并行送入寄存器。

当/CR=1、M1M0=01时,在上升沿作用下,DSR端输入的数码依次送入寄存器。

2、寄存器并行方式与串行方式比较,并行存取方式的速度比串行存取方式慢得多,而且所用的数据线要比串行方式多。

答案:F

解题:寄存器并行方式与串行方式比较,并行存取方式的速度比串行存取方式快得多,但所用的数据线要比串行方式多。

3、寄存器能够把串行数据变成并行数据。

答案:T

解题:寄存器能够把串行数据变成并行数据。

4、双向移位寄存器74LS194当/CR端输入低电平时,所有输出均为零。

答案:T

解题:双向移位寄存器74LS194当/CR端输入低电平时,所有输出均为零。

5、数据锁存器74HC573的/OE引脚输入无效信号为高时,输出为高阻。

答案:T

解题:数据锁存器74HC573的/OE引脚输入无效信号为高时,输出为高阻

6.能存放二值代码的部件叫做寄存器。

寄存器按功能分为数码寄存器和移位寄存器。

数码寄存器只供暂时存放数码,可以根据需要将存放的数码随时取出参加运算或者进行数据处理。

移位寄存器不但可存放数码,而且在移位脉冲作用下,寄存器中的数码可根据需要向左或向右移位。

答案:T

解题:能存放二值代码的部件叫做寄存器。

寄存器按功能分为数码寄存器和移位寄存器。

数码寄存器只供暂时存放数码,可以根据需要将存放的数码随时取出参加运算或者进行数据处理。

移位寄存器不但可存放数码,而且在移位脉冲作用下,寄存器中的数码可根据需要向左或向右移位。

7.从寄存器取出数码的方式也有并行输出和串行输出两种。

在并行输出方式中,被取出的数码在对应的输出端同时出现;在串行输出方式中,被取出的数码在一个输出端逐位输出。

答案:T

解题:从寄存器取出数码的方式也有并行输出和串行输出两种。

在并行输出方式中,被取出的数码在对应的输出端同时出现;在串行输出方式中,被取出的数码在一个输出端逐位输出。

8.构成寄存器的核心器件是触发器。

对寄存器中的触发器只要求具有置0、置1的功能即可,所以无论何种结构的触发器,只要具有该功能就可以构成寄存器了。

答案:T

解题:构成寄存器的核心器件是触发器。

对寄存器中的触发器只要求具有置0、置1的功能即可,所以无论何种结构的触发器,只要具有该功能就可以构成寄存器了。

9. 数据锁存器74HC573的输出具有高阻、保持、数据输出等功能。

答案:T

解题: 数据锁存器74HC573的输出具有高阻、保持、数据输出等功能。

10.构成寄存器的核心器件是触发器。

所有触发器都可以构成寄存器。

答案:F

解题:对寄存器中的触发器只要求具有置0、置1的功能即可,不是所有的寄存器,比如T和T’寄存器就不可以。

(二)选择题

1、有一组代码需暂时存放,应选用()。

A.计数器

B.寄存器

C.编码器

D.译码器

答案:B

解题:寄存器可用于数据存储。

2、如果采用四位单向移位寄存器,将四位二进制数串行输入变保存起来需()个CP脉冲才能完成。

A.1

B.4

C.8

D.16

答案:B

解题:因为要求是串行输入,每次CP输入一位数据。

所以需要4个脉冲。

3、为了把串行输入的数据转换为并行输出的数据,可以使用()。

A.寄存器B.移位寄存器C.计数器D.存储器

答案:B

解题:移位寄存器可以实现串行输入的数据转换为并行输出的数据。

4、有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP作用下,四位数据的移位过程是( A )。

A. 1011--0110--1100--1000--0000

B. 1011--0101--0010--0001--0000

C. 1011--1100--1101--1110--1111

D. 1011--1010--1001--1000—0111

答案:A

解题:1011--0110--1100--1000--0000

5、N个触发器可以构成能寄存()位二进制数码的寄存器。

A.N-1

B.N

C.N+1

D.2N

答案:B

解题:一个触发器对应寄存器的一个位。

6. 下列功能的触发器中,()不能构成移位寄存器。

A.SR触发器B.JK触发器C.D触发器D.T和T'触发器。

答案:D

解题:要求具有置0、置1的功能。

7. 4位移位寄存器,现态Q0Q1Q2Q3为1100,经左移1位后其次态为()。

A.0011或1011 B.1000或1001 C.1011或1110 D.0011或1111

答案:B

解题:输入是0,出现1000;输入是1,出现1001状态。

8.一个四位串行数据,输入四位移位寄存器,时钟脉冲频率为1kHz,经过()可转换为4位并行数据输出。

A.8ms B.4ms C.8µs D.4µs

答案:B

解题:需要4个CP脉冲时间,每个CP时间为1ms。

9.要使锁存器74HC573将输入数据送到输出端,那么输出使能端/OE和锁存控制端LE信号分别为()

A.0,1

B.0,0

C.1,0

D.1,1

答案:A

解题: 输出使能端/OE有效,为0;锁存控制端LE为有效信号1,实现将输入数据送到输出端功能。

10.当锁存器74HC573的输出使能端/OE为低电平,锁存控制端LE信号也为低电平,那么输出()

A.高阻抗

B.保持

C.D

答案:B

解题: 输出使能端/OE有效,为0;锁存控制端LE为有效信号0,实现将输入数据送到输出端功能保持功能。

二、课后作业

1、试画出用2片74LS194组成8位双向移位寄存器的逻辑图。

解题:如下图所示。

图1

2、分析下图所示电路,画出状态转换图和时序图,并说明CP 和Q2是几分频。

×

××××&1

074LS194D R D IR D

IL CP D 0D 1D 2D 3

Q 0Q 1Q 2Q 3S 0S 1CP R D

图题2

解题:从图所示电路图可知,S1S0=01,根据表4.8-3所示的74LS194功能移寄存器的逻辑功能,可画出如图4.8-7所示的状态图。

从上述时序图可知,CP与Q2之间的关系为七分频。