华为命题【华为命题均属于集成电路专业赛(创芯大赛)】

华为笔试真题及答案

华为笔试真题及答案1、华为公司的全称为()A、深圳市华为技术有限公司B、华为技术有限公司C、华为公司D、我司(答案:B,答A、C者酌情给分,答D者马上辞退,我司三令五申制止使用该华为内部土语,屡禁不止,老员工不行教也,只好从新员工抓起,格杀勿论)2、华为公司的企业性质是()A、民营B、私营C、国营D、上市公司(答案:A,此题主要让考生了解公司的性质)3、华为公司的商标象征()A、红太阳B、菊花C、扇贝(答案:B,答A者酌情给分,答C者马上辞退,每天就想着吃)4、从以下选项中选择出公司的常务副总裁()A、任正非B、孙亚芳C、李一男D、郑宝用E、张燕燕(答案:BD,答C者马上辞退,让他到李一男的公司去报到吧)5、华为公司的年终奖一般是在每年的什么时候发()A、元旦后B、春节前C、7月下旬或8月上旬D、劳动节前E、国庆节前(答案:C,切记,由于是年中奖,而不是年终奖)6、华为公司的配给你的”股票是()A、**发的B、用自己的奖金去买(答案:B)7、老板常说的土八路,是指()A、老板自己的革命年月的光芒历史B、本地化的用服兄弟C、季度考核为D的兄弟(答案:B)2023华为笔试真题及答案二1. 找错void test1(){char string[10];char* str1=0123456789;strcpy(string, str1);}答:外表上并且编译都不会错误。

但假如string数组原意表示的是字符串的话,那这个赋值就没有到达意图。

最好定义为char string[11],这样最终一个元素可以存储字符串结尾符\0;void test2(){char string[10], str1[10];for(int I=0; I10;I++){str1[I] =a;}strcpy(string, str1);}答:strcpy使用错误,strcpy只有遇到字符串末尾的\0才会完毕,而str1并没有结尾标志,导致strcpy函数越界访问,不妨让str1[9]=\0,这样就正常了。

集成电路创新大赛题目

集成电路创新大赛题目随着信息技术的不断发展,集成电路已经成为了现代电子工业的核心领域之一。

为了促进集成电路领域的创新发展,近年来,国内外各大高校和企业纷纷举办集成电路创新大赛,吸引了大批电子、计算机、通信等相关专业的优秀学生和科研人员参赛。

那么在集成电路创新大赛中,都有哪些经典的比赛题目呢?以下是其中几个经典的集成电路创新大赛题目:1、基于FPGA的数字信号处理算法设计。

FPGA是一种可编程逻辑器件,广泛应用于数字信号处理、图像处理、嵌入式系统等领域。

这个题目要求参赛者设计一种数字信号处理算法,并采用FPGA实现。

这对参赛者的硬件设计和软件调试能力都有一定的挑战性。

2、基于深度学习的图像识别系统设计。

深度学习已经成为了目前最流行的人工智能技术之一。

这个题目要求参赛者设计一种基于深度学习的图像识别系统,并采用ASIC实现。

参赛者需要具备深度学习算法的理论基础和ASIC设计的实际经验。

3、基于MEMS传感器的智能健康手环设计。

MEMS传感器是一种微型化、集成化的传感器,广泛应用于智能手机、智能手环等产品中。

这个题目要求参赛者设计一种基于MEMS传感器的智能健康手环,并实现心率、血氧、血压等多种健康监测功能。

这个题目对参赛者的硬件设计和算法实现能力都有较高的要求。

4、基于5G通信芯片的高速数据传输系统设计。

5G通信是目前最热门的通信技术之一,具有超高速率、低延迟、高可靠性等特点。

这个题目要求参赛者设计一种基于5G通信芯片的高速数据传输系统,并实现高速数据的稳定、低延迟的传输。

这个题目对参赛者的通信技术和芯片设计能力都有一定的挑战性。

总的来说,在集成电路创新大赛中,题目的难度和挑战性与时俱进,反映了当前集成电路领域的最新技术和发展趋势。

只有参赛者拥有强大的专业知识和实践能力,才能在这些比赛中脱颖而出,成为集成电路领域的未来之星。

22年华为杯题型方法

22年华为杯题型方法华为杯全国大学生智能硬件设计大赛一直以来都备受瞩目,每年吸引众多高校学子积极参与。

2022年的华为杯赛事已经落下帷幕,本文将为大家总结本次比赛的特点、题型分类以及解题方法,并为今后的备赛提供一些建议。

一、华为杯赛事简介华为杯全国大学生智能硬件设计大赛旨在激发大学生创新意识,提高创新能力,培养创新型人才。

赛事分为初赛、复赛和决赛三个阶段,参赛选手需在规定时间内完成各项任务,展示自己的硬件设计能力。

二、2022年华为杯题型分类1.创意设计类:此类题目要求选手针对给定场景或需求,设计具有创新性和实用性的智能硬件产品。

2.技术实现类:此类题目侧重于考察选手对硬件技术原理的理解和运用,要求选手完成特定功能模块的设计和实现。

3.系统集成类:此类题目要求选手将多个硬件模块整合成一个完整的系统,展示系统的稳定性和协同性能。

4.人工智能类:此类题目主要考察选手对人工智能技术的应用和创新,包括算法设计、模型训练等。

三、解题方法与策略1.充分了解赛事规则和评分标准,明确题目要求,避免走弯路。

2.注重团队协作,明确分工,发挥团队成员的优势,提高工作效率。

3.善于借鉴往届优秀作品和现有技术成果,博采众长,为自己的设计增添亮点。

4.关注前沿技术动态,掌握核心技术,提升自身竞争力。

四、备赛指南1.提前做好准备,积累硬件设计相关知识和技能。

2.参加培训课程,提升自己的技术水平和实践能力。

3.组队参赛,寻找志同道合的队友,共同进步。

4.多参加模拟赛和热身赛,熟悉赛事流程,提高应变能力。

总之,华为杯全国大学生智能硬件设计大赛为广大学子提供了一个展示自己才华的舞台。

要想在比赛中脱颖而出,需要扎实的技术功底、创新思维和团队协作。

2020年中国研究生数学建模竞赛A题--华为题_芯片相噪算法设计

2020年中国研究生数学建模竞赛A题(华为公司命题)ASIC芯片上的载波恢复DSP算法设计与实现光数字信号处理(DSP)芯片是光传输领域里的“心脏”,这种芯片往往是基于专用集成电路(ASIC)实现的。

例如,采用7nm芯片工艺制造的光传输芯片容量可以达到800Gbps,相当于单光纤可实现48T bps的容量,保障了网络流量的爆发型增长。

ASIC芯片的DSP算法设计通常包含两个主要步骤,第一步是根据信道损伤的物理模型设计补偿算法,此时只需要考虑浮点计算;第二步是根据芯片资源和功耗约束,将算法改造成ASIC芯片可实现的定点形式,此时需要将算法细化为芯片上最基本的乘、加等运算,并考虑定点量化噪声的影响。

怎样权衡性能和资源,实现具体场景下的最优设计,是DSP芯片算法工程领域持久不变的课题。

本题以oDSP中一种关键的载波恢复算法为例,探讨算法与芯片的最优工程设计。

首先介绍关于基本通信系统和ASIC芯片上算法设计的基本知识。

一、通信系统模型本题考虑一个简化的数字通信系统性能评估模型,如图1所示。

发送端编码后的二进制序列映射调制为星座点上的符号并向外发送,每秒发送的符号个数称为波特率fBaud。

信号在信道中受到色散和相位噪声的影响,并人为加入加性高斯白噪声,噪声量用信号和噪声功率的比值表示。

接收端先补偿色散,再由载波恢复(Carrier Recovery, CR)算法补偿相位噪声,最后信号进行判决后逆映射为二进制比特序列。

受信道中损伤和噪声影响,星座图会发生扩散,从而导致信号判错,使接收到的二进制序列与发端不一致,从而带来误码。

错误二进制比特占总二进制比特的比率称为误码率(BER)。

只要BER小于某个门限,那么纠错编码后的BER就能够小于1e-15次方量级,达到工程意义上的“无误码”传输。

本题中不考虑纠错编码,BER均指直接判决后的BER。

算法评估中常用RSNR(Required SNR)代价来评估算法性能。

SNR(Signal-to-Noise Ratio)指的是信号功率和噪声功率的比例。

2020年数学建模A题--华为题_芯片相噪算法设计题目重点

2020年中国研究生数学建模竞赛A题(华为公司命题)ASIC芯片上的载波恢复DSP算法设计与实现光数字信号处理(DSP)芯片是光传输领域里的“心脏”,这种芯片往往是基于专用集成电路(ASIC)实现的。

例如,采用7nm芯片工艺制造的光传输芯片容量可以达到800Gbps,相当于单光纤可实现48T bps的容量,保障了网络流量的爆发型增长。

ASIC芯片的DSP算法设计通常包含两个主要步骤,第一步是根据信道损伤的物理模型设计补偿算法,此时只需要考虑浮点计算;第二步是根据芯片资源和功耗约束,将算法改造成ASIC芯片可实现的定点形式,此时需要将算法细化为芯片上最基本的乘、加等运算,并考虑定点量化噪声的影响。

怎样权衡性能和资源,实现具体场景下的最优设计,是DSP芯片算法工程领域持久不变的课题。

本题以oDSP中一种关键的载波恢复算法为例,探讨算法与芯片的最优工程设计。

首先介绍关于基本通信系统和ASIC芯片上算法设计的基本知识。

一、通信系统模型本题考虑一个简化的数字通信系统性能评估模型,如图1所示。

发送端编码后的二进制序列映射调制为星座点上的符号并向外发送,每秒发送的符号个数称为波特率fBaud。

信号在信道中受到色散和相位噪声的影响,并人为加入加性高斯白噪声,噪声量用信号和噪声功率的比值表示。

接收端先补偿色散,再由载波恢复(Carrier Recovery, CR)算法补偿相位噪声,最后信号进行判决后逆映射为二进制比特序列。

受信道中损伤和噪声影响,星座图会发生扩散,从而导致信号判错,使接收到的二进制序列与发端不一致,从而带来误码。

错误二进制比特占总二进制比特的比率称为误码率(BER)。

只要BER小于某个门限,那么纠错编码后的BER就能够小于1e-15次方量级,达到工程意义上的“无误码”传输。

本题中不考虑纠错编码,BER均指直接判决后的BER。

算法评估中常用RSNR(Required SNR)代价来评估算法性能。

SNR(Signal-to-Noise Ratio)指的是信号功率和噪声功率的比例。

最全华为上机试题及部分答案

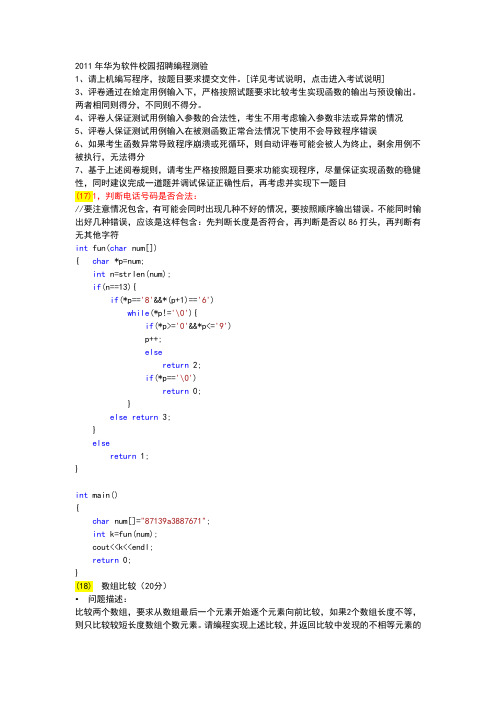

2011年华为软件校园招聘编程测验1、请上机编写程序,按题目要求提交文件。

[详见考试说明,点击进入考试说明]3、评卷通过在给定用例输入下,严格按照试题要求比较考生实现函数的输出与预设输出。

两者相同则得分,不同则不得分。

4、评卷人保证测试用例输入参数的合法性,考生不用考虑输入参数非法或异常的情况5、评卷人保证测试用例输入在被测函数正常合法情况下使用不会导致程序错误6、如果考生函数异常导致程序崩溃或死循环,则自动评卷可能会被人为终止,剩余用例不被执行,无法得分7、基于上述阅卷规则,请考生严格按照题目要求功能实现程序,尽量保证实现函数的稳健性,同时建议完成一道题并调试保证正确性后,再考虑并实现下一题目(17)1,判断电话号码是否合法://要注意情况包含,有可能会同时出现几种不好的情况,要按照顺序输出错误。

不能同时输出好几种错误,应该是这样包含:先判断长度是否符合,再判断是否以86打头,再判断有无其他字符int fun(char num[]){ char *p=num;int n=strlen(num);if(n==13){if(*p=='8'&&*(p+1)=='6')while(*p!='\0'){if(*p>='0'&&*p<='9')p++;elsereturn 2;if(*p=='\0')return 0;}else return 3;}elsereturn 1;}int main(){char num[]="87139a3887671";int k=fun(num);cout<<k<<endl;return 0;}(18) 数组比较(20分)•问题描述:比较两个数组,要求从数组最后一个元素开始逐个元素向前比较,如果2个数组长度不等,则只比较较短长度数组个数元素。

华为测试题+答案

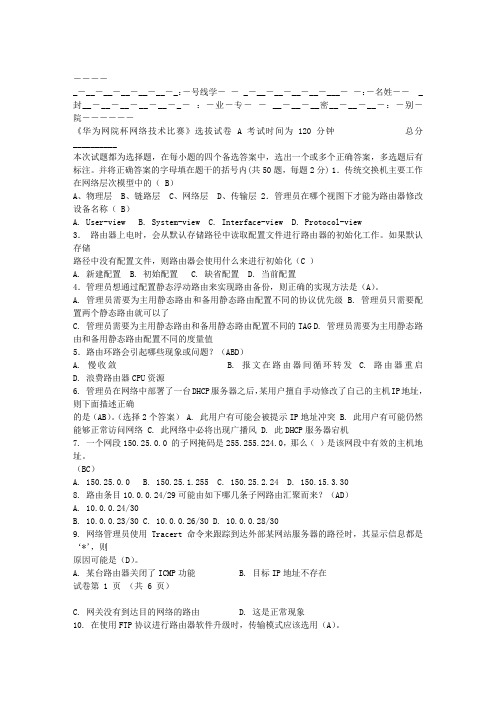

――――_―__―__―__―__―__―_:―号线学―― _―__―__―__―__―___――:―名姓―― _封__―__―__―__―__―_―:―业―专―― __―__―__密__―__―__―:―别―院――――――《华为网院杯网络技术比赛》选拔试卷 A 考试时间为120分钟总分__________本次试题都为选择题,在每小题的四个备选答案中,选出一个或多个正确答案,多选题后有标注。

并将正确答案的字母填在题干的括号内(共50题,每题2分) 1.传统交换机主要工作在网络层次模型中的( B)A、物理层B、链路层C、网络层D、传输层 2.管理员在哪个视图下才能为路由器修改设备名称( B)A. User-viewB. System-viewC. Interface-viewD. Protocol-view3.路由器上电时,会从默认存储路径中读取配置文件进行路由器的初始化工作。

如果默认存储路径中没有配置文件,则路由器会使用什么来进行初始化(C )A. 新建配置B. 初始配置C. 缺省配置D. 当前配置4.管理员想通过配置静态浮动路由来实现路由备份,则正确的实现方法是(A)。

A. 管理员需要为主用静态路由和备用静态路由配置不同的协议优先级B. 管理员只需要配置两个静态路由就可以了C. 管理员需要为主用静态路由和备用静态路由配置不同的TAGD. 管理员需要为主用静态路由和备用静态路由配置不同的度量值5.路由环路会引起哪些现象或问题?(ABD)A. 慢收敛B. 报文在路由器间循环转发C. 路由器重启D. 浪费路由器CPU资源6. 管理员在网络中部署了一台DHCP服务器之后,某用户擅自手动修改了自己的主机IP地址,则下面描述正确的是(AB)。

(选择2个答案) A. 此用户有可能会被提示IP地址冲突 B. 此用户有可能仍然能够正常访问网络 C. 此网络中必将出现广播风 D. 此DHCP服务器宕机7. 一个网段150.25.0.0 的子网掩码是255.255.224.0,那么()是该网段中有效的主机地址。

IC笔试题大全(部分含答案)

EE笔试/面试题目集合分类--IC设计基础1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。

(仕兰微面试题目)2、FPGA和ASIC的概念,他们的区别。

(未知)答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点模拟电路1、基尔霍夫定理的内容是什么?(仕兰微电子)2、平板电容公式(C=εS/4πkd)。

(未知)3、最基本的如三极管曲线特性。

(未知)4、描述反馈电路的概念,列举他们的应用。

(仕兰微电子)5、负反馈种类(电压并联反馈,电流串联反馈,电压串联反馈和电流并联反馈);负反馈馈的优点(降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用)(未知)6、放大电路的频率补偿的目的是什么,有哪些方法?(仕兰微电子)7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。

(未知)8、给出一个查分运放,如何相位补偿,并画补偿后的波特图。

(凹凸)9、基本放大电路种类(电压放大器,电流放大器,互导放大器和互阻放大器),优缺点,特别是广泛采用差分结构的原因。

(未知)10、给出一差分电路,告诉其输出电压Y+和Y-,求共模分量和差模分量。

(未知)11、画差放的两个输入管。

(凹凸)12、画出由运放构成加法、减法、微分、积分运算的电路原理图。

并画出一个晶体管级的运放电路。

(仕兰微电子)13、用运算放大器组成一个10倍的放大器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

华为命题【华为命题均属于集成电路专业赛(创芯大赛)】赛题一:采用硬件RTL代码方式实现串行FFT算法(要求工作频率达到1Ghz)。

描述及要求:1.FFT支持串行64、128、256、512点运算,支持FFT/IFFT两种运算模式。

2.运算支持自适应压缩移位,以减少设计电路面积。

3.对采用的基运算组合方式(基2、4、8)不做强制要求,最大支持基8运算。

4.为减少面积存储单元采用两块单口ram(同一时刻只读或只写),每块大小256*32(数据位宽32bits,ram深度为256(最大支持512点))。

5. FFT输入I/Q数据为12bits有符号数,输出I/Q数据30bits,30bits为理论计算最大值(512点基2串行实现)。

各种运算单元带来的位宽扩展情况:Radix-2 2点FFT最大会带来2bit的数据位扩展Radix-4 4点FFT最大会带来3bit的数据位扩展Radix-8 8点FFT最大会带来4bit的数据位扩展注:自适应移位、ram、复乘器、旋转因子表等均有相应的IP可供选择,选手也可自行设计。

评审得分点:1.500条用例(预设),用例跑通越多,得分越高。

2.FFT运算处理时间越短,得分越高。

3.面积越小,得分越高。

4.综合时钟频率越高,得分越高。

5.时钟门控率越高,得分越高。

输出要求:1.算法设计文档和算法代码。

2.详细设计文档和逻辑代码、软件代码。

赛题二:采用软硬件结合的方式实现SM9算法(要求具备防DFA\SPA\DPA能力)。

描述及要求:1. SM9需要的模乘、模加等基本运算使用硬件实现。

其他高层算法可采用软件实现。

具备防止各种已知SPA\DPA\DFA(二阶或者高阶)攻击的能力。

2.可只实现点乘运算,其它高层算法不强制要求。

3.256点乘至少可以达到20次/S(对应时钟频率为120MHz,其他时钟频率其它密钥位宽可等比例折算)。

4.是否素域等不做强制要求。

评审得分点:1.防攻击能力越强越全面,没有任何防护漏洞。

得分越高。

2. SM9密钥位宽至少为256位,位数越长,得分越高。

3.性能越高,得分越高。

输出要求:1.算法设计文档和算法代码。

2.详细设计文档和逻辑代码、软件代码。

赛题三:逻辑实现ZUC算法(要求具备防DFA\SPA\DPA能力)。

描述及要求:1.逻辑实现一个完整的ZUC算法设计。

具备防止各种已知SPA\DPA(二阶或者高阶)攻击的能力。

防护手段不限。

2.理论分析SPA\DPA(二阶或者高阶)攻击对ZUC的理论破解时间。

3.时钟频率不限,资源不限,功耗不限。

采用VHDL\VERILOG实现。

评审得分点:1.具备防止各种已知SPA\DPA(二阶或者高阶)攻击的能力,无安全漏洞。

2.SPA\DPA防攻击理论清晰,理论破解时间越长得分越高。

输出要求:1.算法设计文档和算法代码。

2.详细设计文档和逻辑代码。

赛题四:基于sigma_delta的高性能Audio Codec设计。

描述及要求:1.实现完整的Digital+Analog系统建模;2.Verilog实现Digital逻辑,完成仿真验证及资源开销;Analog部分完成建模仿真;3.给出完整的性能报告,包含SNR、THD+N、频响、带内平坦度等指标。

评审得分点:1.关键性能指标SNR>100dB,THD+N<-80dB;性能越好得分越高;2.Digital逻辑面积越小得分越高。

输出要求:1.算法设计文档和算法代码。

2.详细设计文档和逻辑代码。

3.仿真报告。

赛题五:低功耗的语音识别系统设计。

描述及要求:1.能通过语音端点检测(VAD:VoiceActivity Detection)实现语音唤醒,满足在有语音环境下才进行后续的语音识别,从而达到低功耗的要求。

2.能对简单的词语和短命令(“播放”、“暂停”等)进行高精度的识别。

3. Verilog实现Digital逻辑。

评审得分点:1.高噪声条件下(SNR<5DB)语音唤醒的虚警率(误唤醒)和漏检率均不高于30%;低噪声条件下虚警率(误唤醒)和漏检率均不高于15%。

2.语音识别模块的识别率越高越好。

输出要求:1.详细设计文档及算法设计文档。

2.性能测试或仿真报告。

赛题六:麦克风阵列算法建模及方案实现。

描述及要求:1.麦克风阵列是利用一定数目,一定空间构型的声学传感器(一般是麦克风)组成,用来对声场的空间特性进行采样并处理的系统。

2.麦克风阵列近场(2~3个mic)或远场算法(大于3个mic)建模(波束形成/声源定位/去混响技术…),任选其一。

3.方案实现:资源不限,平台不限。

选择一个语音应用场景,完成对该算法硬件平台方案实现。

评审得分点:1.对现有主流算法对比分析,可从抗干扰性、识别率、运算速度、算法代价等方面进行分析。

2.选择一种算法进行代码实现,仿真结果分析。

3.硬件平台实现,对比算法仿真结果。

能够对mic器件选择、mic数量及摆放位置进行理论分析。

4.能够对算法优化改进分析。

输出要求:1.算法分析设计文档和算法代码(matlab/c/c++)。

赛题七:实现一个SparseMatrix-Multiply-Vector Accelerator。

命题描述:实现一个Sparse Matrix-Multiply-Vector (SpMV) Accelerator,提供RTL code,加速算法,并演示计算流程。

我们提供下列矩阵集合(包含MATLAB mat-file格式,Matrix Market 格式,和Rutherford/Boeing格式,做题时选其中一种格式即可):/research/sparse/matrices/HB/beause.html/research/sparse/matrices/Bai/rbsa480.html /research/sparse/matrices/Bai/qc2534.html /research/sparse/matrices/DRIVCAV/cavity07.ht ml/research/sparse/matrices/Fluorem/GT01R.html /research/sparse/matrices/HB/arc130.html /research/sparse/matrices/HB/bp_1600.html /research/sparse/matrices/HB/mbeause.html /research/sparse/matrices/Hollinger/g7jac010.ht ml/research/sparse/matrices/JGD_Homology/ch6-6 -b3.html/research/sparse/matrices/JGD_Homology/n2c6-b4.html/research/sparse/matrices/JGD_GL7d/GL7d11.ht ml请自行下载矩阵,并将其转换为32-bit浮点。

以Dense或者CSR/COO/HYB 等常见稀疏矩阵存储格式(或者自定义的某种稀疏存储格式),将上面所列12个矩阵分次存入内存空间。

利用所提供的脚本生成与这些矩阵(Mi x Ni)尺寸相配的随机向量(N x 1)并存入内存。

向量和矩阵的存入不计入运算时间。

所设计的加速器,需要从内存中读取矩阵和向量,并传入加速器内部实现矩阵和向量相乘,并最后将结果存入内存。

实现要求:1.所有矩阵,向量元素均为single-precisionfloating point(32 bits)长度2.加速器的硬件逻辑中最多存在256个fp32浮点乘法器3.12个矩阵的格式预处理可由软件处理;但对随机产生的12个向量的预处理必须由加速器的硬件逻辑完成。

4.允许将附加和预处理后得到的信息存入内存5.不允许用有损的方式6.加速器与内存之间的读、写的数据位宽各为128-bit。

为简化非关键特性,内存频率和加速器同频,接口为Dual Port SRAM,单cycle延迟。

(见图1)7.由脚本随机产生的向量也会有一定程度的稀疏率(30%~80%)。

参赛者可以结合稀疏向量一同加速。

(注意不能对向量预处理。

注意处理向量的硬件代价)8.脚本:向量取决于矩阵的高度,请自行用脚本产生一组随机向量(稀疏率为30%-80%),或使用提供脚本生成向量.提供的脚本为python 3脚本,参赛者可根据需求修改为python 2或其他脚本的语法。

import randomas rnimport mathimport syslength =sys.argv[1]lower= int(length)*30/100upper= int(length)*80/100ran= rn.randint(lower,upper)array= []for x inrange(ran):array.append(0.0)for y inrange(int(length) - ran):array.append(rn.uniform(-10.0,10.0))rn.shuffle(array)for elem inarray:print(str(elem) + ", ", end ='')print("")评审得分点:1.计算结果要正确,可忽略32bit精度结果的误差2.所费的运算时间越少,得分越高3.通常,如果矩阵不做任何稀疏存储,仅以Dense格式进行运算,则运算时间肯定会比稀疏化后矩阵的时间长;如果根据CSR/COO/HYB(或者自定义的某种稀疏存储格式)稀疏存储,并采取与此有关的优化手段(跳0等),则运算时间可以大为降低;4.逻辑规模越小,得分越高5.加速器对内存访问带宽越小,得分越高6.功耗越小,得分越高输出要求:1.详细的算法解释文档,和算法代码。

请在文档中写明加速亮点。

2.详细的设计文档,和RTL代码(Verilog)。

请在文档中写明低功耗设计点。

3.硬件对上述12个benchmarks的加速性能分析文档。

赛题八: 时序加扰防护的理论分析及攻击。

描述及要求:1.选择AES/DES/SM4中任意一种对称加解密引擎,在FPGA平台实现对对称加解密引擎的时序加扰防护,防护方法包括但不限于随机时钟门控、随机时钟抖动及伪操作等;2.从理论上比较各个加扰防护的防护能力,说明各个防护的优缺点;3.在FPGA平台上选择一种或几种时序加扰防护进行实际攻击测试,攻击可以获得正确的密钥信息。

4.实现的时钟频率不限,但是时序加扰对于性能的影响不能过大。

评审得分点:1.在FPGA平台上实现的时序加扰方法越多、防护能力越强得分越高。

2.不同时序加扰防护比对理论分析清晰,结论越合理得分越高。