关于NOR Flash擦写和原理分析

nor flash program disturb的原理

nor flash program disturb的原理Nor Flash Program Disturb (NFPD) 是指在Nor Flash存储芯片的编程过程中,由于电荷累积和分布不均导致的其它存储位置的擦除或编程干扰现象。

这可能会破坏相邻的存储单元,产生错误写入或删除数据的情况。

本文将详细介绍Nor Flash Program Disturb的原理和其可能引发的问题。

一、Nor Flash存储器简介Nor Flash Memory是一种非易失性存储器,由于其良好的读取速度和快速访问能力而被广泛应用于嵌入式系统和移动设备。

它被分为多个块,而每个块又被划分为多个扇区。

二、Nor Flash编程过程Nor Flash在编程过程中,首先需要将待编程的块进行擦除操作,然后再写入所需的数据。

擦除是将块中的所有单元数据置为“1”,而编程是将指定单元的数据置为“0”。

三、Nor Flash Program Disturb的原理Nor Flash Program Disturb (NFPD) 是由于编程过程中电荷的累积和分布不均所引起的问题。

在Nor Flash存储器中,相邻的存储单元由于物理上的接近,会产生相互影响,当编程操作过程中的原始单元的电荷有限时,相邻单元的电荷也会受到影响。

四、NFPD的影响和可能问题1. 异常编程:由于电荷的分布不均,原始单元编程时,相邻单元可能由于电荷交互而意外编程,导致数据错误或无法预料的结果。

2. 存储单元数据的错误改变:在编程过程中,如果相邻的单元受到干扰,其数据可能被更改或删除,导致数据的不一致和错误。

3. 存储单元的耐久性下降:由于NFPD过程中的电子迁移,相邻存储单元的寿命可能会受到缩短,其中一些存储单元可能会出现更快的老化现象。

五、降低NFPD影响的措施为了降低Nor Flash Program Disturb的影响,可以采取以下措施:1. 错误校验和纠正技术 (ECC):使用ECC技术来检测和纠正数据错误。

NOR Flash擦写和原理分析

1. NOR FLASH 的简单介绍NOR FLASH 是很常见的一种存储芯片,数据掉电不会丢失.NOR FLASH支持Execute On Chip,即程序可以直接在FLASH片内执行(这意味着存储在NOR FLASH上的程序不需要复制到RAM就可以直接运行).这点和NAND FLASH 不一样.因此,在嵌入式系统中,NOR FLASH很适合作为启动程序的存储介质.N OR FLASH的读取和RAM很类似(只要能够提供数据的地址,数据总线就能够正确的给出数据),但不可以直接进行写操作.对NOR FLASH的写操作需要遵循特定的命令序列,最终由芯片内部的控制单元完成写操作.从支持的最小访问单元来看,NOR FLASH一般分为8 位的和16位的(当然,也有很多NOR FLASH芯片同时支持8位模式和是16 位模式,具体的工作模式通过特定的管脚进行选择).对8位的NOR FLASH芯片,或是工作在8-BIT模式的芯片来说,一个地址对应一个BYTE(8-BIT)的数据.例如一块8-BIT的NOR FLASH,假设容量为4个B YTE.那芯片应该有8个数据信号D7-D0 和2个地址信号,A1-A0.地址0x0对应第0个BYTE,地址0x1对应于1BYTE,地址0x2对应于第2个BYTE,而地址0x3则对应于第3 个BYTE.对16位的NOR FLASH芯片,或是工作在16-BIT模式的芯片来说,一个地址对应于一个HALF-WORD(16-BIT)的数据.例如,一块16-BIT的NOR FLASH,假设其容量为4个BYTE.那芯片应该有16 个数据信号线D15-D0 和1个地址信号A0.地址0x0对应于芯片内部的第0个HALF-WORD,地址0x1对应于芯片内部的第1个HALF-WORDFLASH一般都分为很多个SECTOR,每个SECTOR包括一定数量的存储单元.对有些大容量的FLASH,还分为不同的BANK,每个BANK包括一定数目的SEC TOR.FLASH的擦除操作一般都是以SECTOR,BANK或是整片FLASH为单位的.在对FLASH进行写操作的时候,每个BIT可以通过编程由1变为0,但不可以有0修改为1.为了保证写操作的正确性,在执行写操作前,都要执行擦除操作.擦除操作会把FLASH的一个SECTOR,一个BANK或是整片FLASH的值全修改为0xFF.这样,写操作就可以正确完成了.由于NOR FLASH没有本地坏区管理,所以一旦存储区块发生毁损,软件或驱动程序必须接手这个问题,否则可能会导致设备发生异常. 在解锁、抹除或写入N OR FLASH区块时,特殊的指令会先写入已绘测的记忆区的第一页(Page).接着快闪记忆芯片会提供可用的指令清单给实体驱动程序,而这些指令是由一般性闪存接口(CommON FLASH memory Interface, CFI)所界定的. 与用于随机存取的ROM不同,NOR FLASH也可以用在存储设备上;不过与NAND FLASH 相比,NOR FLASH的写入速度一般来说会慢很多.2. NOR Flash的烧写方式以下内容,如无特别说明,处理器指的是ARM 处理器,FLASH 指的都是NOR FLASH.另外,BYTE指的是8-BIT的数据单元,HALF-WORD代表的是16-BIT 的数据单元,而WORD 则代表了32-BIT的数据单元.2.1 处理器寻址ARM 可以说是目前最流行的32位嵌进式处理器.在这里只提一下ARM处理器的寻址,为后面做个展垫.从处理器的角度来看,系统中每个地址对应的是一个BY TE的数据单元.这和很多别的处理器都是一样的.2.2 处理器和NOR FLASH的硬件连接从前面的先容,我们知道从处理器的角度来看,每个地址对应的是一个BYTE 的数据单元.而,NOR FLASH 的每个地址有可能对应的是一个BYTE的数据单元,也有可能对应的是一个HALF-WORD的数据单元.所以在硬件设计中,连接AR M处理器和NOR FLASH时,必须根据实际情况对地址信号做特别的处理.假如ARM处理器外部扩展的是8-BIT的NOR FLASH, 数据线和地址线的连接应该如图1所示. 从图中我们可以看到,处理器的数据信号D0-D7和FLASH 的数据信号D0-D7是逐一对应连接的,处理器的地址信号A0-An和NOR FLA SH的地址信号A0-An 也是逐一对应连接的.假如ARM处理器外部扩展的是16-BIT的NOR FLASH, 地址线必须要错位连接. 图2给了一个ARM处理器和16-BIT NOR FLASH的连接示意图.如图2所示,ARM处理器的数据信号D0-D15和FLASH 的数据信号D0-D15是逐一对应的.而ARM处理器的地址信号和NOR FLASH 的地址信号是错位连接的, ARM的A0悬空,ARM 的A1 连接FLASH 的A0,ARM 的A2连接FLASH的A1,依次类推.需要错位连接的原因是:ARM处理器的每个地址对应的是一个BY TE 的数据单元,而16-BIT 的FLASH 的每个地址对应的是一个HALF-WOR D(16-BIT)的数据单元.为了保持匹配,所以必须错位连接.这样,从ARM处理器发送出来的地址信号的最低位A0对16-BIT FLASH来说就被屏蔽掉了.NOR Flash的烧写方式- 懵懂者- 懵懂者的随便写补充说明:一般来说,ARM处理器内部要设置相应的寄存器,告诉处理器外部扩展的FLASH 的位宽(8-BIT/16-BIT/32-BIT) .这样,处理器才知道在访问的时候如何从FL ASH正确的读取数据;有些ARM处理器内部可以设置地址的错位.对于支持软件选择地址错位的处理器,在连接16-BIT FLASH的时候,硬件上可以不需要把地址线错位.读者设计的时候,请参考MCU的数据手册,以手册为准,以免造成不必要的麻烦;假如处理器支持内部设置地址错位,在实际访问的时候,送出的地址实际上是在MCU内部做了错位处理,其作用是等效于硬件连接上的错位的.上面的描述可能比较抽象,下面让我们来看2个ARM处理器访问16-BIT FLASH的例子:例子1:ARM处理器需要从地址0x0读取一个BYTEARM处理器在地址线An-A0上送出信号0x0;16-BIT FLASH在自己的地址信号An-A0上看到的地址是0x0,然后将地址0 x0对应的16-BIT数据单元输出到D15-D0上;ARM处理器知道访问的是16-BIT的FLASH,从D7-D0上读取所需要的一个B YTE的数据.例子2:ARM处理器需要从地址0x1读取一个BYTEARM处理器在地址线An-A0上送出信号0x1;16-BIT FLASH在自己的地址信号An-A0上看到的地址依然是0x0, 然后将地址0x0对应的16-BIT数据单元输出到D15-D0上;ARM处理器知道访问的是16-BIT的FLASH,从D15-D8 上读取所需要的一个BYTE 的数据.2.3 从软件角度来看ARM 处理器和NOR FLASH 的连接从软件的角度来理解ARM处理器和FLASH的连接.对于8-BIT的FLASH的连接,很好理解,由于ARM处理器和8-BIT FLASH的每个地址对应的都是一个BYTE 的数据单元.所以地址连接毫无疑问是逐一对应的.假如ARM 处理器连接的是16-BIT 的处理器,由于ARM 处理器的每个地址对应的是一个BYTE 的数据单元,而16-BIT FLASH 的每个地址对应的是一个HALF-WORD 的1 6-BIT的数据单元.所以,也毫无疑问,ARM处理器访问16-BIT处理器的时候,地址肯定是要错开一位的.在写FLASH驱动的时候,我们不需要知道地址错位是由硬件实现的,还是是通过设置ARM处理器内部的寄存器来实现的,只需要记住2点:ARM处理器访问8-BIT FLASH的时候,地址是逐一对应的;ARM处理器访问16-BIT FLASH的时候,地址肯定是错位的.2.4 8-BIT FLASH 烧写驱动实例- HY29F040HY29F040是现代公司的一款8-BIT的NOR FLASH.在这个小节里,我们以这个芯片为例子,讲述如何对8-BIT NOR FLASH进行操作.HY29F040的容量为512K-BYTE,总共包括8 个SECTOR,每个SECTOR 的容量是64K-BYTE.该芯片支持SECTOR擦除,整片擦除和以BYTE 为基本单位的写操纵.HY29F040的命令定义如表-1所示.1、位(bit)来自英文bit,音译为“比特”,表示二进制位。

nor flash原理

nor flash原理

Nor Flash是一种非易失性存储器,它采用了NAND闪存和NOR闪存的结合技术。

它的工作原理类似于NOR闪存,但又

具有NAND闪存的高密度和低成本优势。

Nor Flash的存储单元由一对互补的MOSFET(金属-氧化物-

半导体场效应晶体管)构成,其中一个MOSFET称为选择MOSFET,另一个称为传输MOSFET。

传输MOSFET与普通

的NOR闪存单元相似,负责数据传输和读写操作。

选择MOSFET用于选择要读取和写入的存储单元,与传输MOSFET之间共享同一栅极线。

Nor Flash的数据存储是通过在多个存储单元中存储电荷量来

实现的。

将电荷量设置为高电荷表示“1”,低电荷表示“0”。

在

写入数据时,选择MOSFET将所需存储单元暴露给外部电源,并在该单元的传输MOSFET上施加电压。

当传输MOSFET导

通时,电荷被注入或释放到存储单元中,从而改变存储单元的电荷量和存储值。

Nor Flash的读取操作与NOR闪存类似。

选择MOSFET选择

要读取的存储单元,并通过传输MOSFET上的引脚检测存储

单元中的电荷量。

根据电荷量的高低,从而确定存储单元的存储值。

总的来说,Nor Flash利用选择MOSFET和传输MOSFET的组合来实现数据的读写和存储。

这种结构将NAND闪存的高密

度和低成本结合了NOR闪存的高速读取和修改功能,适用于许多应用,如嵌入式系统和存储器设备。

NAND与NOR FLASH的原理及异同

NAND与NOR FLASH的原理与异同!一、存储数据的原理两种闪存都是用三端器件作为存储单元,分别为源极、漏极和栅极,与场效应管的工作原理相同,主要是利用电场的效应来控制源极与漏极之间的通断,栅极的电流消耗极小,不同的是场效应管为单栅极结构,而FLASH为双栅极结构,在栅极与硅衬底之间增加了一个浮置栅极。

[attach]158 [/attach]浮置栅极是由氮化物夹在两层二氧化硅材料之间构成的,中间的氮化物就是可以存储电荷的电荷势阱。

上下两层氧化物的厚度大于50埃,以避免发生击穿。

二、浮栅的重放电向数据单元内写入数据的过程就是向电荷势阱注入电荷的过程,写入数据有两种技术,热电子注入(hot electron injection)和F-N隧道效应(Fowler Nordheim tunneling),前一种是通过源极给浮栅充电,后一种是通过硅基层给浮栅充电。

NOR型FLASH通过热电子注入方式给浮栅充电,而NAND则通过 F-N隧道效应给浮栅充电。

在写入新数据之前,必须先将原来的数据擦除,这点跟硬盘不同,也就是将浮栅的电荷放掉,两种FLASH都是通过F-N隧道效应放电。

三、0和1这方面两种FLASH一样,向浮栅中注入电荷表示写入了'0',没有注入电荷表示'1',所以对FLASH清除数据是写1的,这与硬盘正好相反;对于浮栅中有电荷的单元来说,由于浮栅的感应作用,在源极和漏极之间将形成带正电的空间电荷区,这时无论控制极上有没有施加偏置电压,晶体管都将处于导通状态。

而对于浮栅中没有电荷的晶体管来说只有当控制极上施加有适当的偏置电压,在硅基层上感应出电荷,源极和漏极才能导通,也就是说在没有给控制极施加偏置电压时,晶体管是截止的。

如果晶体管的源极接地而漏极接位线,在无偏置电压的情况下,检测晶体管的导通状态就可以获得存储单元中的数据,如果位线上的电平为低,说明晶体管处于导通状态,读取的数据为0,如果位线上为高电平,则说明晶体管处于截止状态,读取的数据为1。

浅谈NorFlash的原理及其应用

浅谈NorFlash的原理及其应用NOR Flash NOR Flash是现在市场上两种主要的非易失闪存技术之一。

Intel 于1988年首先开发出NOR Flash 技术,彻底改变了原先由EPROM(Erasable Programmable Read-Only-Memory电可编程序只读存储器)和EEPROM(电可擦只读存储器Electrically Erasable Programmable Read - Only Memory)一统天下的局面。

紧接着,1989年,东芝公司发表了NAND Flash 结构,强调降低每比特的成本,有更高的性能,并且像磁盘一样可以通过接口轻松升级。

NOR Flash 的特点是芯片内执行(XIP ,eXecute In Place),这样应用程序可以直接在Flash闪存内运行,不必再把代码读到系统RAM中。

NOR 的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响到它的性能。

NAND的结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。

应用NAND的困难在于Flash的管理需要特殊的系统接口。

性能比较 flash闪存是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。

任何flash 器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。

NAND器件执行擦除操作是十分简单的,而NOR则要求在进行擦除前先要将目标块内所有的位都写为0。

由于擦除NOR器件时是以64~128KB的块进行的,执行一个写入/擦除操作的时间为5s,与此相反,擦除NAND器件是以8~32KB的块进行的,执行相同的操作最多只需要4ms。

执行擦除时块尺寸的不同进一步拉大了NOR和NAND之间的性能差距,统计表明,对于给定的一套写入操作(尤其是更新小文件时),更多的擦除操作必须在基于NOR的单元中进行。

norflash读写原理

norflash读写原理

NorFlash是一种基于NOR门的闪存存储器,常用于嵌入式系统和移

动设备中。

NorFlash读写原理详细如下:

1. NorFlash的存储单元是基于NOR门的,NOR门是一种由两个并

联的晶体管构成的门电路。

这意味着每个存储单元都需要两个晶体管

来读取或写入数据。

2. 由于它使用的是NOR门,Norflash的读操作是直接的。

读操作的

时候,将地址放置于地址总线上,然后该地址将直接映射到存储器单元。

当地址被选中时,数据被从存储单元读取到存储器的输出引脚。

读操作不会影响存储器单元的数据。

3. NorFlash的写操作比读操作复杂。

它需要进行多个步骤,例如擦除,编程和校验。

擦除操作将存储器中的数据全部清除为1。

编程操作将操作码和数据写入存储器中的指定地址。

校验操作用于验证编程操作是

否成功。

4. NorFlash的写操作需要一个称为“写使能控制器”的特殊控制器。

写使能控制器向存储器发出一个信号,告诉存储器将数据写入指定的

地址。

写使能控制器还确保编程操作在操作码和数据被成功编程之后,

存储器单元返回正确的状态值。

总之,NorFlash的读写原理是基于NOR门,并且需要进行多个步骤来完成写操作。

了解NorFlash的读写原理可以帮助我们更好地理解如何在嵌入式系统或移动设备中储存和读取数据。

Flash Memory

typically 5s

Multi Layer Cell Flash

MLC Flash characteristics

The application of Flash Memory

the 32GB SanDisk microSDHD面向智能手机市场, 采用第3代32nm工艺。 3-bit-per-cell NAND flash technology.

2Gb Nor Flash Memory

AMD与富士通公司将各自的NOR闪存业务剥离出来,成 立了合资公司Spansion

Apple-Nanຫໍສະໝຸດ Flash 最大买家

苹果发布2010年第四财季财报, 营收203.4亿美元,同比增67%, 利润44.6亿美元,同比增70%。 iPhone 销量1410万部,同比涨 91.4%; Mac电脑销量389万台,同比涨 27.4%; iPod销量905万部,同比跌11%; iPad销量419万台,环比涨28.4%。

NAND Flash

Nand Flash 阵列结构

Why named NAND?

Nand Flash 擦写方式

Fowler -Nordheim (FN) tunneling. Nand 擦除写入均采用FN 沟道效应。

2Gb Nand Flash

Nor vs Nand

typically 4ms

ipad

iphone 4

Thank you!

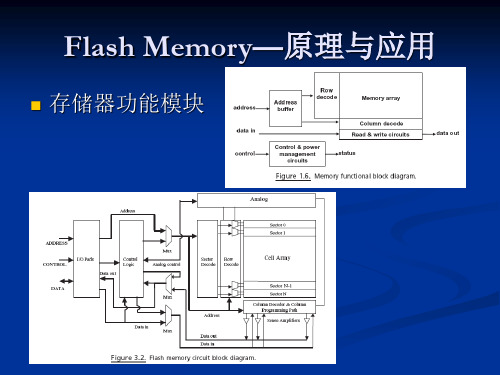

Flash Memory—原理与应用

存储器功能模块

基本单元

信息存储方式

Flash Memory 分类

按读写及擦除方式

NORFLASH工作原理

NORFLASH工作原理Nor Flash 具有像内存一样的接口,它可以像内存一样读,却不可以像内存一样写,Nor Flash 的写、擦除都需要发出特定的命令。

谈到Nor Flash 通常就会涉及到CFI ([Common Flash Interface) 接口,一般 Nor Flash 都支持发命令来读取厂家 ID 和 设备 ID 等基本信息,但并不是所有的 Nor Flash 都支持发命令来获取和芯片本身容量大小、扇区数、擦除块大小等信息。

为了让将来的 Nor Flash 兼容性更好,引进了 CFI 接口,将芯片有关的信息都写入芯片内部,通过 CFI 命令就可以获取这些信息。

Linux 内核中对各种型号的 Nor Flash 都有很好的支持 ,但是其组织复杂,不利于分析。

这里选用 u-boot 里面的 Nor Flash 代码来分析。

代码位于:u-boot-2010.06/board/samsung/smdk2410/flash.c 。

通常内核里面要识别一个 Nor Flash 有两种方法:一种是 jedec 探测,就是在内核里面事先定义一个数组,该数组里面放有不同厂家各个芯片的一些参数,探测的时候将 flash 的 ID 和数组里面的 ID 一一比较,如果发现相同的,就使用该数组的参数。

另一种是 cfi 探测,就是直接发各种命令来读取芯片的信息,比如 ID、容量等。

jedec 探测的优点就是简单,缺点是如果内核要支持的 flash 种类很多,这个数组就会很庞大。

../samsung/smdk2410/flash.c 文件采用的是第一种方法,但是还是有些区别的,内核里面用 jedec 探测一个芯片时,是先通过发命令来获取 flash 的 ID,然后和数组比较,但是 flash.c 中连 ID 都是自己通过宏配置的。

unsigned long flash_init (void){for (i = 0; i < CONFIG_SYS_MAX_FLASH_BANKS; i++){ulong flashbase = 0;//设置 flash_id ,这个标志保存厂家 ID 和 设备 IDflash_info[i].flash_id =#if defined(CONFIG_AMD_LV400)(AMD_MANUFACT & FLASH_VENDMASK) | (AMD_ID_LV400B & FLASH_TYPEMASK); #elif defined(CONFIG_AMD_LV800)(AMD_MANUFACT & FLASH_VENDMASK) | (AMD_ID_LV800B & FLASH_TYPEMASK); #else#error "Unknown flash configured"#endif//设置 flash 大小和扇区数flash_info[i].size = FLASH_BANK_SIZE;flash_info[i].sector_count = CONFIG_SYS_MAX_FLASH_SECT;//对于 flash 的每个扇区,都需要保存扇区的首地址for (j = 0; j < flash_info[i].sector_count; j++){......flash_info[i].start[j] = flashbase + (j - 3) * MAIN_SECT_SIZE;}size += flash_info[i].size; //片外所有flash 的总大小 }//对代码区的扇区设置写保护,这里只是软件的一种设定flash_protect (FLAG_PROTECT_SET, CONFIG_SYS_FLASH_BASE,CONFIG_SYS_FLASH_BASE + monitor_flash_len - 1,&flash_info[0]);//如果环境变量保存在 nor 里面,还需对这些扇区设置写保护flash_protect (FLAG_PROTECT_SET, CONFIG_ENV_ADDR,CONFIG_ENV_ADDR + CONFIG_ENV_SIZE - 1, &flash_info[0]);return size; //返回 flash 大小}flash_init() 函数主要是做一些 flash 的初始化,比如设置 flash 的 ID、大小、扇区数等来构造flash_info_t 结构体,但是从上面的代码可以看出,在该初始化函数中并没有做任何与硬件有关的初始化,所有的值都是通过外部赋值,也就是说我们可以给这些成员变量赋任何我们想要的值,哪怕这些值并不是 flash 真正的参数,虽然这些值并不影响本函数的调用,但是和下面这些函数就有密切关系。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

关于NOR Flash擦写和原理分析

NOR Flash NOR Flash是现在市场上两种主要的非易失闪存技术之一。

Intel 于1988年首先开发出NOR Flash 技术,彻底改变了原先由EPROM(Erasable Programmable Read-Only-Memory电可编程序只读存储器)和EEPROM(电可擦只读存储器Electrically Erasable Programmable Read - Only Memory)一统天下的局面。

紧接着,1989年,东芝公司发表了NAND Flash 结构,强调降低每比特的成本,有更高的性能,并且像磁盘一样可以通过接口轻松升级。

NOR Flash 的特点是芯片内执行(XIP ,eXecute In Place),这样应用程序可以直接在Flash闪存内运行,不必再把代码读到系统RAM中。

NOR 的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响到它的性能。

NAND的结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。

应用NAND的困难在于Flash的管理需要特殊的系统接口。

性能比较 flash闪存是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。

任何flash 器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。

NAND器件执行擦除操作是十分简单的,而NOR则要求在进行擦除前先要将目标块内所有的位都写为0。

由于擦除NOR器件时是以64~128KB的块进行的,执行一个写入/擦除操作的时间为5s,与此相反,擦除NAND器件是以8~32KB的块进行的,执行相同的操作最多只需要4ms。

执行擦除时块尺寸的不同进一步拉大了NOR和NAND之间的性能差距,统计表明,对于给定的一套写入操作(尤其是更新小文件时),更多的擦除操作必须在基于NOR的单元中进行。

这样,当选择存储解决方案时,设计师必须权衡以下的各项因素。

l 、NOR的读速度比NAND稍快一些。

2、NAND的写入速度比NOR快很多。

3 、NAND的4ms擦除速度远比NOR的5s快。

4 、大多数写入操作需要先进行擦除操作。

5 、NAND的擦除单元更小,相应的擦除电路更少。

此外,NAND 的实际应用方式要比NOR复杂的多。

NOR可以直接使用,并可在上面直接运行代码;而NAND需要I/O接口,因此使用时需要驱动程序。

不过当今流行的操作系统对NAND结构的Flash都有支持。

此外,Linux内核也提供了对NAND结构的Flash的支持。

详解 NOR。