基于FPGA的大尺寸LED文字显示屏的一种实现方案

基于FPGA的高级LED文字屏显示系统

a 初 始状 态 赋值 模 块 c n o 的 . ot l r

S 总线 的 d 用 Moe i 做后 仿真 ,根据 功 能主 要是 通过 与 工控 机IA . dl m S 赋 值 , 定显 示 的方式 , 确 数据 截取 的

对 利 用 该 软 件 实现 系统 的设 计调 试 过 加载的硬件特性和逻辑功能仿真硬件 通 信 , 主控 制 模块 进行 初始 状态 的 程, 通过 软 件检 测 F G P A编程 的正 确 功能 . 性 .软 件的 功能 : e用 Map s 载码 流 文件 , . xl 下 u 完 坐 标等 等 . b 数 据接 收 模块 dt acp 的 . a _ cet a 功 能 主 要 是 接 收 由显 示 卡 传 送 的 数 据, 并根 据 主控 制模 块传 送 的控 制字

绚丽 L D 卡输 出 口, C 显 串并 口, 网卡 , O D C 系统 的显示 内容与计算 机监视 器演播 示 阵面 上 显示 出 多色 ,多灰度 , 电子 盘 等众 多接 口, 本身 构成 完整 卡

的P C体系且具有看门狗功能.半长

卡 的总 线一般 是 IA的 , S 它不能 支持 P I 系列 的 C U,一般 情 况 下 使 用 I I P

并 本 设 计是 用 于 同 步 映像 屏 的 显 确 定截 取 的数 据 , 把截 取 的数据 发

A 示 控制 . 根据 各个 模块 的功 能 不同将 给 此 时接 收数 据 的 R M .

功 能选 择按 钮 , 过按 钮选 择输 整 个逻 辑设 计分 为 四部分 .分别 是 : 通 出数 据 的类 型 ,检 测潜 在错 误 . a初 始状 态 赋值模 块 cn o . ot l r

3

o

由于 E/ . / .Xr,所 以 E/ . 从 带 内 S 导 b = ( ) N E N b 可 N / N

基于FPGA的LED大屏幕显示控制器设计

基于FPGA的LED大屏幕显示控制器设计【摘要】描述了一个使用FPGA控制LED点阵屏幕的系统,该系统使用Verilog HDL编制代码,实现了LED屏幕的字符、图像显示与简单的动画效果,在Quartus II平台上通过了编译与仿真。

本系统稳定可靠,性能强。

【关键词】FPGA;LED点阵;动态显示1.引言LED显示技术相比于投影显示、液晶显示、激光显示等其他大屏幕显示技术,有其独特的优越性,例如:高亮度、宽可视角度以及可定制的屏幕外形等。

这些特点使得LED显示屏被广泛应用于工业、信息发布、体育比赛等各个领域。

当今市场上的LED显示系统,通常使用单片机作为主控芯片连接I/O扩展电路来控制LED显示屏。

但是,对于LED大屏幕显示屏来说,要求扫描速度快,而单片机内部的资源较少、运行速度较慢,在很多时候难于满足系统要求。

同时,也使产品的灵活性和稳定性受到一定程度的影响。

FPGA器件具有处理速度快,有大量的可编程逻辑单元和丰富的布线资源,在处理大流量数据应用时具有明显的优势,它的引脚资源丰富,可扩展性强。

因此,基于FPGA实现的大屏幕LED 显示成为目前的应用热点。

2.控制器的系统架构本系统使用的FPGA芯片是Altera公司Cyclone II系列的EP2C35。

该芯片具有33216个逻辑单元、322个引脚,是一个功能十分强大、内部资源十分丰富的高密度FPGA芯片。

系统使用Verilog HDL语言编制系统代码,实现了双色显示屏控制字符显示与简单动画。

本系统由FPGA系统板、74HC595组成的移位寄存器组两组、74HC138组成的行选择信号产生电路、三极管组成的驱动电路以及8块8×8双色点阵组成大屏幕显示单元组成,系统的具体结构如图1所示。

3.功能单元实现本系统的显示控制原理是采用动态行扫描显示,这也是本系统显示关键技术。

具体实施方法如下:首先通过移位寄存器组向显示模块的列端输出相应行的数据,然后使用译码电路点亮对应的行;根据扫描频率,再切换成下一行的数据,再点亮对应行。

用FPGA实现大屏幕LED显示屏的控制

引言目前,市场上的中小规模LED显示系统,一般采用传统的单片机作为主控芯片。

对LED大屏幕显示屏来说,由于数据传输量大,要求扫描速度快,而单片机内部的资源较少、运行速度较慢,难于满足系统要求。

以FPGA作为控制器,一方面,FPGA采用软件编程实现硬件功能,速度较快;另一方面,它的引脚资源丰富,可扩展性强。

因此,用单片FPGA和简单的外围电路就可以实现大屏幕LED显示屏的控制,无需另外设计汉字库,具有集成度高、稳定性好、设计灵活和效率高等优点。

1 系统总体结构LED大屏幕显示系统由上位机(PC机)、单片机系统、FPGA控制器、LED 显示屏的行列等模块组成,如图1所示。

上位机负责汉字、字符等数据的采集与发送。

单片机系统与上位机之间以异步串行通信工作方式,通过串行端口从上位机获得已完成格式转换的待显示的图形点阵数据,并将其存入EEPROM存储器。

之后通过FPGA控制器,将存储器的显示数据还原到LED显示屏。

扫描控制电路采用芯片CyclONeEP1C6,利用VHDL语言编程实现,采用1/16扫描方式,刷新频率在60Hz以上。

本文着重介绍2561024的单色图文显示屏的FPGA控制模块。

2 LED显示屏基本工作原理对大屏幕LED显示屏来说,列显示数据通常采用的是串行传输方式,行采用1/16的扫描方式。

图2为1632点阵屏单元模块的基本结构,列驱动电路采用4个74HC595级联而成。

在移位脉冲SRCLK的作用下,串行数据从74HC595的数据端口SER一位一位地输入,当一行的所有32列数据传送完后,输出锁存信号RCLK并选通行信号Y0,则第1行的各列数据就可按要求显示。

按同样的方法显示其余各行,当16行数据扫描一遍(即完成一个周期)后,再从第1行开始下一个周期的扫描。

只要扫描的周期小于20ms,显示屏就不闪烁。

2561024大屏幕显示屏由1632个的1632点阵屏级联而成。

为了缩短控制系统到屏体的信号传输时间,将显示数据分为16个区,每个区由161024点阵组成,每行数据为1024/8=128字节,显示屏的像素信号由LED显示屏的右侧向左侧传输移位,把16个分区的数据存在同一块存储器。

基于FPGA的大屏幕LED点阵显示系统设计

基于FPGA的大屏幕LED点阵显示系统设计LED屏早在60年代就已出现,但直到90年代中期,才出现了全彩屏,该技术近年的价格已有了很大的降幅,分辨率也有了很大的改善。

对于视频来说,LED屏的低分辨率表现性能良好。

平常看到LED屏的分辨率与电脑显示器的分辨率是差不多的。

LED 彩色显示大屏是室外显示大屏中用的最多的,是公认的室外大型显示屏中最值得发展的产业,LED 屏以其高亮度、长使用寿命更胜一筹。

与LCD 相比,LED屏播放视频时的响应速度更快,亮度更高。

与电子发射显示器相比,LED制造更简单。

与OLED相比,LED技术更成熟。

总之,LED 显示以其得天独厚的优势占据了高分辨率视频显示市场。

本文设计的基于FPGA的大屏幕LED点阵显示系统处理数据更快、存储量更大。

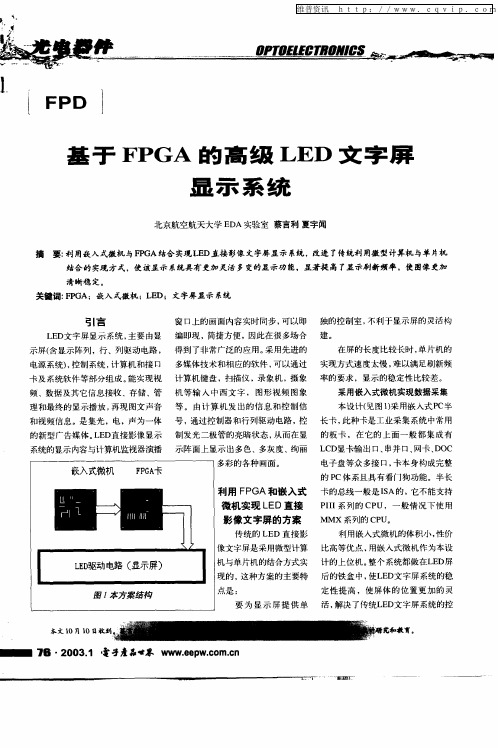

一、接收卡控制系统的总体方案设计如图1所示,视频数据通过DVI 接口传给FPGA1,进行分辨率的切换和显示区域的选择以及信号的反伽码矫正,通过网络传输给接收卡的FPGA2,通过FPGA2 进行数据的缓存,灰度控制以及行扫描和列驱动功能。

接收卡接收的是DVI 传给FPGA1,经FPGA1 处理后的数据。

在FPGA2 内部还要进行数据处理,处理要达到的目标:(1)数据能在LED 屏幕上分区显示;(2)256 灰度级屏幕大小:256*800。

(一)灰度实现方案的选择采用专用驱动芯片BHL2000来控制LED显示点阵,其内部自动有灰度控制电路。

BHL2000是一块专门用于LED 扫描和驱动的高性能室外屏室内屏通用的专用集成电路。

BHL2000 芯片对LED 点阵的灰度采用占空比的调制方式并接受8 位并行灰度脉宽宽度与灰度数据值成正比,图像数据存储容量为32*16*8 比特,数据输入扫描与数据输出扫描独立,控制系统结构简单。

专用芯片与通用芯片相比有它独特的特点,专用驱动芯片内部有SRAM,输出时恒流控制。

LED 显示效果更好,灰度实现简单,容易控制,为以后的扩展使用打下良好的基础。

基于Actel FPGA的LED显示屏控制方案

Actel 基于Flash 架构的FPGA 讲座(29)2011.4LED(Light Emitting Diode)大屏幕作为现代信息发布的重要媒体,正受到社会各界尤其是商业界和广告界的极大重视,被广泛应用于工业、交通、商业、广告、金融、体育比赛、模拟军事演习、电子景观等领域。

随着科技的进步,全彩LED 显示屏(RGB 三基色)逐渐得到普及应用。

本方案采用Actel 的FPGA 实现对彩色LED 屏的控制,对于系统的可靠性大大增强,而且低成本的单芯片大大减轻了系统的成本。

1.概述(1)功能概述选择FPGA 实现LED 全彩屏的控制,主要考虑系统的性能需求,系统的升级需要以及系统的设计成本等因素。

现代社会对信息显示效果的高要求,以及视频数据量的加大,对显示控制器提出了挑战,如图 1所示。

本文实现的LED 全彩屏主要实现了以下功能:● 保证全彩LED 显示屏显示颜色不失真;● 能够实现256级灰度;● 能正确显示文字、图片、动画等信息;●可以接收PC 机输出的DVI 数据流实时显示。

(2)系统框图控制器主要完成对LED 扫描板的控制和显示,其中包括色度控制、灰度控制、数据重构以及存储形式、扫描方式的基于Actel FPGA的LED显示屏控制方案图2 LED显示屏控制器功能框图图1 LED显示屏应用示例表1 数据对应点亮时间图3 数据位灰度权值选择等方面。

控制器的功能框图如图 2所示。

2.各功能模块介绍控制器实现的主要难点在于其灰度的控制。

利用人眼的视觉效应,我们知道,只要刷新频率足够高不产生LED 器件闪烁的现象时,LED 器件点亮的时间越长,显示的亮度就越强。

为此我们将使用LED 器件亮灭时间的占空比波形来控制灰度级别。

下面我们分别介绍在8场扫描和19场扫描方式下的灰度控制。

(1)8场扫描模块8场扫描方式是针对串行驱动LED 显示屏而提出的。

以最常见的8bit 位宽的显示数据来说,我们分8次显示,第一次将8位数据的第0位显示在LED 屏上,第2次将8位数据的第1位显示在LED 显示屏上,这样重复操作,直至将8位数据全部显示在LED 显示屏上。

基于FPGA的大尺寸LED文字显示屏的一种实现方案

1 前言在现代生活中,越来越多的LED文字屏被用于广告和信息的发布。

使用文字屏发布消息具有及时、醒目的优点,因此其应用的范围也越来越广。

目前的文字屏主要有两种实现方式。

第一种方式:由计算机(通常是工控机)来对屏幕显示图像进行组织,并将其发送到扫描电路。

扫描电路只负责对文字屏进行刷新。

两部分的分工明确,不失为一种好的实现方式。

但是这种方式必须使用工控机,从而使成本上升。

第二种方式:使用单片机完成通讯、电路的刷新,对显示内容进行组织,因此单片机的任务很重。

在有的设计中使用了多单片机的设计,尽管如此,对于较大的文字屏,单片机的处理速度还是显得不够,而且单片机之间的协调也成了一个麻烦的问题。

因此,必须对此方案进行改进。

2 文字屏原理文字屏是由发光二级管阵列组成。

对于单色的文字屏,一个发光管代表一个像素;对于双色的文字屏,两个发光二级管代表一个像素;对于全彩色的文字屏,三个发光二级管代表一个像素。

发光二级管一般由串行移位寄存器驱动。

如果驱动能力不足,还需要加接其它驱动电路。

在采用扫描方式进行显示时,每行有一个行驱动器,各行的同名列共用一个列驱动器,由行译码器给出的行选通信号,从第一行开始,按顺序依次对各行进行扫描。

另一方面,根据各列锁存的数据,确定相应的列驱动器是否将该列点亮。

数据的传递采用串行传输的方基于FPGA的大尺寸LED文字显示屏的一种实现方案黄夔夔,夏宇闻(北京航空航天大学 EDA实验室,北京 100000)摘要:介绍一种使用三万门规模的FPGA和单片机相结合的方法来实现大尺寸LED文字显示屏控制器的设计方案。

通过对比单片机和FPGA实现的逻辑电路在电气性能上的差异,可以了解合理地使用FPGA逻辑来加强单片机控制器,可以大幅度地提高系统的性能。

关键词:FPGA;单片机;Verilog HDL;文字屏;LED中图分类号:TP273 文献标识码:A 文章编号:1003-353X(2002)10-0024-05A scheme of FPGA based large size LEDdisplay for charactersHUANG Kui-kui,XIA Yu-wen(Beijing University of Aero. & Astro.;Beijing 100000,China)Abstract:A scheme of large size LED display for characters, which is based on a FPGAenhanced MCU is introduced in this paper. How to use FPGA reasonably to strengthen MCU, andincrease the performance of digital system dramatically is also introducted in this paper.Key words:FPGA;MCU;Verilog HDL;display;LED半导体技术第27卷第10期二OO二年十月24Semiconductor Technology Vol. 27 No. 10October 2002252.2 FPGA内部的电路结构数据和命令接收电路用于从单片机接收由单片机转发的来自上位机的数据和命令。

基于FPGA的LED显示屏控制方案

基于FPGA的LED显示屏控制方案概述随着需求的增加,许多电子设备和系统需要具有更高的性能,并且需要更高效的数据处理。

这些设备和系统需要实现更多的功能,需要数据存储更可靠,并需要更快速地处理数据。

现在有许多解决方案,其中包括基于FPGA的解决方案。

本文将讨论基于FPGA的LED显示屏控制方案。

FPGA概述FPGA是一种可编程逻辑门阵列(PLA),其在电子领域有着广泛应用。

与传统的ASIC(特定应用集成电路)不同,FPGA具有可编程的门电路。

因此,FPGA的功能可以在设计时通过编程进行定制化。

FPGA的应用范围很广泛,包括通信、计算机、嵌入式系统等等。

LED显示屏概述LED显示屏主要由LED点阵组成,其在各种场合都有广泛的应用。

例如:室内的广告牌、室外的公告牌、舞台背景幕等等。

在这些应用中,LED显示屏可以显示图像、文字和动态影像等各种内容。

此外,LED显示屏也可以用于显示环境温度、湿度或其他各种数据。

基于FPGA的LED显示屏控制方案基于FPGA的LED显示屏控制方案可用于设计各种LED显示屏,下面是实现这个目标的基本步骤:1. FPGA系统设计FPGA系统模块化设计需要采用标准的设计方法,使用VHDL或Verilog HDL等基本的设计语言,进行逻辑功能的实现。

通常这些模块包括时钟模块、程序存储模块、输入输出模块、控制器模块等。

2. 帧控制器设计基于FPGA的LED显示屏需要一个单独的控制器模块来完成任务。

FPGA的设计人员需要设计此控制器模块。

在控制器中,我们可以采用一种帧的高速重复显示,这可以使用同一模块来完成大部分图像操作。

3. 显示控制器设计显示控制器用于执行具体的显示功能,在LED驱动器下进行控制,并为数据的输出提供信号。

例如,如果我们要做一个汽车行车记录仪,我们可以将控制器模块中的显存用于存储数据,该数据将由LED显示模块驱动。

4. 驱动器设计LED驱动器是一个必要的模块,它用于将信号转换为LED点阵中的亮度(即灰度)控制。

基于FPGA+MCU的大型LED显示屏系统

基于FPGA+MCU的大型LED显示屏系统

本系统考虑对于传输视频数据大小和驱动LED大屏幕刷新频率的要求,LED发送卡、接收卡均采用FPGA作为核心处理器,笔者选择Xilinx公司基于90nm工艺制造的XC3S250E-FTG256,内有25万逻辑门,最高频率可以达到600MHz,完全可以满足系统速度的要求在系统中作为扫描控制单元,同时以MCU芯片为主控制单元。

采用该方案可以有效简化显示屏的电路结构,从而提高了整个控制系统的灵活性和可靠性。

1 系统的组成和工作原理

该系统采用89C51单片机和SDRAM 组成控制中心,由基于Xilinx公司的FPGA的90nm工艺制造的XC3S250E-FTG256和RAM 组成扫描控制模块,以FLASH作为存储器模块,采用以太网传输数据,组成LED屏的控制系统。

系统结构如图1所示。

其工作原理为:主机通过TFTP协议将图片传输给系统以太网接口模块,以太网接口模块解析协议,接收图片数据,然后将数据传输给MCU,MCU 将接收到的数据写入存储模块NAND FLASH.在显示时,MCU读取FLASH 中的数据,通过SPI接口将数据传输给FPGA扫描控制模块,经扫描控制模块处理后传输到LED屏幕上显示。

图1 基于FPGA和MCU的LED显示屏控制系统框图。

用FPGA设计LED汉字滚动显示器

摘要:本文主要讨论了使用EDA工具设计汉字滚动显示器的技术问题。

文中首先描述了基于现场可编程门阵列(FPGA)的硬件电路;然后研究了在8×8LED发光二极管点阵上显示滚动汉字的原理,并给出了基于ALTERA的参数化模型库LPM描述其功能的VHDL语言程序设计;最后对使用EDA工具软件加工被显示数据文件的方法进行了讨论。

采用传统方法设计的汉字滚动显示器,通常需要使用单片机、存储器和制约逻辑电路来进行PCB(印制电路板)板级的系统集成。

尽管这种方案有单片机软件的支持较为灵活,但是由于受硬件资源的限制,未来对设计的变更和升级,总是难以避免要付出较多研发经费和较长投放市场周期的代价。

随着电子设计自动化(EDA)技术的进展,基于可编程ASIC器件的数字电子系统设计的完整方案越来越受到人们的重视,并且以EDA技术为核心、的能在可编程ASIC器件上进行系统芯片集成的新设计方法,也正在快速地取代基于PCB板的传统设计方式。

如何使用EDA工具设计电子系统是人们普遍关心的问题。

在EDA工具软件MAX+PLUS Ⅱ的支持下,本设计通过了编译、适配和软件仿真验证。

最后用载入真实实验系统的硬件实验证明了它的正确性。

硬件设计为了简化讨论,本文只研究在单个8×8 LED 发光二极管点阵上滚动显示多汉字信息的问题。

图1给出的就是一个使用美国ALTERA公司10K系列FPGA设计的可支持滚动显示多汉字信息的通用硬件电路。

在图中,标准JTAG接口与PC机并口相连,用于下载设计数据至FPGA中;LED点阵的data线由FPGA的I/O线串300Ω限流电阻后驱动,而sw线直接由FPGA的I/O 线驱动。

LED点阵采用扫描式工作方式,控制sw线的循环扫描信号为低电平有效,显示数据data为高电平有效。

由于ALTERA的10K10LC84-4芯片内部有足够的RAM资源,所以本设计没有采用外部RAM。

另外,图中的配置EPROM为可选件,只有当要求汉字滚动显示器脱机运行时才需要采用。

基于FPGA的LED大屏幕控制系统的设计实现

基于FPGA的LED大屏幕控制系统的设计实现相比于液晶显示、投影显示等其他大屏幕显示技术,显示技术有其独特的优越性:高亮度、宽可视角度、丰盛的颜色以及可定制的屏幕外形。

这些特点使得LED显示屏被广泛应用于工业、交通、商业广告、信息发布、体育竞赛等各个领域。

LED大屏幕控制系统是一个融合计算机控制技术、视频技术、光技术、通信技术的综合系统。

当前主流的LED大屏幕控制系统多以或FPGA结合其他芯片为主控芯片。

目前LED大屏幕正朝着显示面积更大、显示亮度更高、色彩更艳丽的方向进展。

这些都给LED大屏幕控制系统提出了新的挑战。

本文基于公司的低成本Cyclone II系列芯片EP2CQ208C设计了LED大屏幕控制系统,在传统的SDRAM缓存技术上,提出了优化的SDRAM乒乓式缓存技术并具体阐述了反γ校正、色彩调整、灰度级调整等在FPGA 中的实现。

本系统终于实现了最大1 280×1 024辨别率、最低240 Hz 刷新率的超大LED屏幕显示。

同时可以通过PC机上软件对LED屏幕举行亮度、对照度、灰度级等参数的灵便调整,得到越发细腻的显示画面。

1 系统结构本文所设计的LED大屏幕控制系统结构1所示,囫囵系统分为发送卡和接收卡两部分。

以Altera公司的EP2CQ208C作为主控芯片,DVI数据解码选用了TI公司的TFP201A(最高支持SXGA),数据缓存选用了Samsung的K4S643232C,千兆以太网芯片选用了Realtek公司的RTL8212(双端口千兆物理层芯片)。

本系统的数据流分为控制数据和显示数据。

控制数据由PC机上的软件发出,发送卡的FPGA接收控制数据,判定是控制发送卡还是控制接收卡的数据,假如是控制接收卡,则通过千兆网络将数据发送至接收卡。

TFP201A从DVI接口解码出显示数据后由FPGA缓存入SDRAM,然后在第1页共4页。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基 于 F GA的 大 尺 寸 L 字 P D文 E

显 示 屏 的一种 实现 方案

黄 夔 夔 , 夏 宇 闻

( 京航 空航 天 大 学 E 北 DA 实验 室 ,北京 1 0 0 0 0 0)

摘 要 :介 绍 一 种 使 用 三 万 门 规 模 的 F GA 和 单 片 机 相 结 合 的 方 法 来 实 现 大 尺 寸 LE 文 字 显 示 屏 控 制 器 P D

A c m e o s he f FPGA s d l di pl y f r c a a t r s a o h rce s

H U AN G uik , X I U. e K . ui A Y w n

( e i nvr t o A r. s o B in 0 00C i ) B in U i sy f e &A t . e i 100,hn jg ei o f; j g a

Absr c : A c e e o a g i e LED i p a o h r c e s ta t s h m fl r e sz d s l y f r c a a t r ,wh c s b s d o GA i h i a e n a FP

对 屏 幕 显 示 图像 进 行 组 织 , 并 将 其 发 送 到 扫 描 电 路 。扫 描 电路 只 负责对 文 字屏 进行 刷新 。两部 分 的 分 工 明确 ,不 失为 一 种好 的实 现方 式 。但是 这 种方

式 必 须 使 用 工 控 机 , 从而 使 成 本 上 升 。 第 二 种方 式 :使 用单 片机 完 成通 讯 、电路 的刷 新 ,对 显 示 内容 进 行 组 织 , 因此 单 片机 的任 务 很

法 ,将 列 数据 一位 一位 的传往 列驱 动 器 。当一 行 的

22 P . F GA内部 的 电路 结构 数 据和 命令 接收 电路 用 于从 单片机 接 收 由单片 机 转 发 的来 自上位 机 的数 据和 命 令 。数据 将 直接 写 入外 部 存储 器 , 而 命 令 字 转 送 到 中央 控 制 逻 辑 电 路 。该 电路 根据 命 令 的类 型 去控 制行 列扫 描逻 辑 电 路 ,使其 计算 出正确 的数 据地 址 ,并将 该地 址 送 下 级 电路 ,由下级 电路 去读 取数 据 。读 出 的数据 包 括 两页 画面 的数 据 ,因此 ,在将 数据 送 驱动 电路 前 需 要 根 据 来 自选 通逻 辑 的命 令将 其 中一 个数 据 选 出。

第 一 种 方 式 : 由计 算机 ( 常 是 工 控 机 )来 通

文字 屏 ,一个 发 光管代 表 一个 像素 ;对 于双 色 的文

字屏 ,两个 发 光二 级管 代 表一个 像 素 ;对 于 全彩 色 的文 字屏 ,三 个发 光 二级管 代表 一 个像 素 。发光 二 级管 一般 由串行 移位 寄存 器驱 动 。如 果驱 动 能力 不 足 ,还 需要 加接 其 它驱 动 电路 。在 采用 扫 描 方式进 行 显 示 时,每行 有 一个 行驱 动器 ,各 行 的 同名列 共 用 一 个 列驱 动 器 , 由行 译 码 器给 出 的行选 通 信 号 , 从 第 一行 开始 ,按顺 序 依次对 各 行进 行扫 描 。另 一 方 面 ,根 据 各列 锁存 的数 据 ,确 定 相应 的 列驱 动器

重 。在有 的设计 中 使用 了多 单片 机 的设 计 ,尽管 如

此 ,对 于较 大 的文 字屏 ,单 片机 的处 理速 度还 是 显

2 半 导体技 术 第 2 4 7| I o囊 ‘i

是 否 将 该 列 点亮 。 数据 的传 递 采 用 串行 传 输 的 方

二 o o 二 牟 十 月

维普资讯

e ha e CU s i r uc d i hi pe . o o us n nc d M i ntod e n t spa r H w t e FPGA e on bl o s r n he CU ,a d r as a y t te gt n M n i cr a e he pe f m a eofd g t ls t m r m a i a l s a s ntod t d i hi pe . n e s t r or nc i ia yse d a tc ly i lo i r uc e n t spa r

Ke r  ̄ FP y wo d GA; CU; rl g HDL; ip a ; D M Ve io d s l y LE

得 不够 ,而 且单 片机 之 间 的协 调 也成 了一 个 麻烦 的

1 前 言

在 现代 生活 中, 来越 多 的L D文字 屏被 用 于 越 E

问题 。 因此 , 必 须 对 此 方 案 进 行 改 进 。

的设 计 方案 。通过 对 比单 片机 和 F GA实 现 的逻辑 电路在 电气 性 能上 的差 异 ,可 以了解 合 理 地使 用 F GA P P 逻 辑 来 加 强 单 片机 控 制 器 , 可 以 大 幅 度 地 提 高 系 统 的性 能 。 关 键 词 :F GA; 单 片 机 ;Ve io HDL; 文字 屏 ;LE P rl g D 中图分 类 号 :T 2 3 P 7 文献 标 识码 :A 文章 编 号 :l 0 - 5 X( 0 2 l - 0 4 0 0 33 3 2 0 )00 2 -5

广 告和 信 息 的 发 布 。 使 用 文 字 屏 发 布 消 息 具 有 及 时 、醒 目的优 点 , 因此 其 应 用 的范 围也越 来 越 广 。

2 文 字 屏 原 理

文字屏 是 由发光 二级 管 阵列组 成 。对于 单色 的

目前 的 文字 屏 主 要有 两 种 实 现 方式 。