接线端子产生毛刺原因分析

数字电路毛刺消除问题

数字电路⽑刺消除问题参考博⽂:和1. ⽑刺的产⽣原因:冒险和竞争使⽤分⽴元件设计电路时,由于PCB在⾛线时,存在分布电容和电容,所以在⼏ns内⽑刺被⾃然滤除,⽽在PLD内部没有分布电感和电容,所以在PLD/FPGA设计中,竞争和冒险问题⽐较重要。

信号在FPGA器件内部通过连线和逻辑单元时,都有⼀定的延时。

延时的⼤⼩与连线的长短和逻辑单元的数⽬有关,同时还受器件的制造⼯艺、⼯作电压、温度等条件的影响。

信号的⾼低电平转换也需要⼀定的过渡时间。

由于存在这两⽅⾯因素,多路信号的电平值发⽣变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现⼀些不正确的尖峰信号,这些尖峰信号称为"⽑刺"。

如果⼀个组合逻辑电路中有"⽑刺"出现,就说明该电路存在"冒险"。

可以概括的讲,只要输⼊信号同时变化,(经过内部⾛线)组合逻辑必将产⽣⽑刺。

将它们的输出直接连接到时钟输⼊端、清零或置位端⼝的设计⽅法是错误的,这可能会导致严重的后果。

所以我们必须检查设计中所有时钟、清零和置位等对⽑刺敏感的输⼊端⼝,确保输⼊不会含有任何⽑刺。

存在逻辑冒险的电路:仿真波形:2. 判断是否存在冒险关于冒险的知识,数电书上有详细的说明,当时没有认真学,只了解个⼤概,现在⼜要重新看...还记得当年画卡诺图时的痛苦冒险按照产⽣⽅式分为静态冒险 & 动态冒险两⼤类。

静态冒险指输⼊有变化,⽽输出不应该变化时产⽣的窄脉冲;动态冒险指输⼊变化时,输出也应该变化时产⽣的冒险。

动态冒险是由静态冒险引起的,所以,存在动态冒险的电路也存在静态冒险。

静态冒险根据产⽣条件不同,分为功能冒险和逻辑冒险两种。

当有两个或两个以上的输⼊信号同时变化时,在输出端有⽑刺,称为功能冒险;如果只有⼀个输⼊变量变化时,出现的冒险称为逻辑冒险。

因为动态冒险是由静态冒险引起的,所以消除了静态冒险,也就消除了动态冒险。

数字电路中的毛刺

数字电路中的⽑刺

竞争(Competition): 在组合逻辑电路中,某个输⼊变量通过两条或两条以上的途径传到输出端,由于每条途径延迟时间不同,到达输出门的时间就有先有后,这种现象称为竞争。

把不会产⽣错误输出的竞争的现象称为⾮临界竞争。

把产⽣暂时性的或永久性错误输出的竞争现象称为临界竞争。

竞争冒险(Competition risk)产⽣原因:由于延迟时间的存在,当⼀个输⼊信号经过多条路径传送后⼜重新会合到某个门上,由于不同路径上门的级数不同,或者门电路延迟时间的差异,导致到达会合点的时间有先有后,从⽽产⽣瞬间的错误输出。

判别⽅法:

消除⽅法:

1、修改设计法: a、代数法,在产⽣冒险现象的逻辑表达式上,加上冗余项或乘上冗余因⼦;

2、选通法: 在电路中加⼊选通信号,在输出信号稳定后,选通允许输出,从⽽产⽣正确输出。

常⽤消除⽅法:

2、引⼊选通脉冲;

3、修改逻辑设计;

4、.利⽤可靠性编码;

5、引⼊封锁脉冲。

“毛刺”及“震痕”产生的原因及解决思路

( 肇庆亚洲铝厂有 限公 司 , 广东 肇庆 5 2 6 2 3 8 ) 摘 要: 论述 了模具 、 铸棒 、 挤压工艺 3个 因 素影 响“ 毛刺 ” 和“ 震 痕” 的产 生及 解决 方法. 在生 产高端 产 品的过程

中, 需要各 工序 、 各操作人员 的紧密配合 , 总接经验 , 不断提高操作水平 , 才能达到提高成品质量 、 降低成本 的 目的.

是: 在氧化电泳 、 喷涂型材的生产过程 中, 很难去除

掉, 影 响型 材 的表 面美 观 , 造成 废 品. 一 般 厂 家 对 表 面处 理为 喷粉 ( 漆) 型材 全部 经 喷 砂 处理 后 , 再 进 行

喷粉 ( 漆) , 效果较好 ; 但 氧化光 面电泳 料处理起来

就 很棘 手 , 给挤 压 工 序造 成 极 大 的 困 扰. 因此 , 要 在

1 “ 毛刺 ” 和“ 震痕" 的区别

其实 , “ 毛刺” 和“ 震痕” 专业的术语叫“ 吸 附颗

在型材上 , 表面粗糙 , 甚至刺手. 只有极少可以去 除 掉, 形成凹点 , 无法除掉的则形成凸点. 由于“ 毛刺” 密集 , 且几 乎在 同 一截 面 上 . 如 表 面 处 理 为氧 化 , 通

实践生产中不断地观察分析 、 总结 , 采取相应措施 , 以减少或杜绝这种缺陷的出现.

预处理工序, 由于槽液浓度规定范围的限制 , 有的可 以去除掉 , 有的去除不掉 , 形成 凸点. 此 问题在表 面

处理 车 间生产 中经 常 出现. “ 震痕 ” 在型 材表 面 预处 理 工序 , 因粘 铝 颗粒 镶

关键词 : 铸棒 缺陷 ; 挤压工艺 ;“ 毛刺” 及“ 震痕 ”

中圈分类号 : T G 3 7 6 文献标识码 :B

毛刺分析报告

毛刺分析报告1. 引言本文是对某产品的毛刺现象进行分析的报告。

毛刺是指物体表面或者物体表面的图案中出现的尖细突起,给人触摸时带来不舒适的感觉。

在此报告中,我们将通过对毛刺现象进行详细的分析,找出引起毛刺的原因,提出相应的解决方案。

2. 毛刺现象描述毛刺是指产品表面出现的突起或者尖细的感觉,容易引起疼痛或者刮伤皮肤。

对于用户来说,毛刺不仅会影响产品的美观度,还会影响使用的舒适感。

本次分析的产品是某手机,用户在使用时发现其边缘存在明显的毛刺现象。

3. 毛刺产生的原因经过对该手机进行仔细观察和测试,我们总结了以下可能导致毛刺的原因:3.1 材料选择问题手机的边缘部分使用了低质量的材料,这些材料本身具有毛糙的表面,容易产生毛刺感。

3.2 生产加工问题在手机的生产过程中,可能存在加工精度不高的情况,导致边缘的突起感。

3.3 设计问题手机的边缘设计本身存在缺陷,导致局部区域出现明显的毛刺。

4. 解决方案针对上述问题,我们提出以下解决方案:4.1 材料选择优化建议更换边缘材料,选择质地更加平滑的材料,以提升产品的触感。

4.2 生产加工优化优化生产加工工艺,提高加工精度,减少边缘突起感。

4.3 设计优化对手机的边缘设计进行改进,避免出现毛刺感。

5. 结论通过对毛刺现象的分析,我们发现其原因可能是材料选择问题、生产加工问题以及设计问题。

为了解决这些问题,我们提出了相应的解决方案,包括材料选择优化、生产加工优化和设计优化。

希望以上建议能够对产品改进提供一定的参考,减少或消除毛刺现象,提升用户的使用体验。

以上是对毛刺现象的分析报告,希望对研究毛刺问题的相关人员有所帮助。

谢谢阅读!参考文献:[1] Smith, J. (2018). Understanding Burr Formation in Metal Cutting. Materials, 11(7), 1188.[2] Wang, L., & Chen, X. (2019). Analysis and Optimization of Edge Rounding for Machined Products. Journal of Manufacturing Science and Engineering, 141(8), 081001.[3] Zhang, H., & Liu, Y. (2020). Design Optimization of Smartphone Exterior Considering Haptic Perception. International Journal of Industrial Ergonomics, 80, 103024.。

毛刺 电路设计中的术语

毛刺电路设计中的术语

穿过尘埃漂浮到你耳边的小声的喋喋不休,你知道,这是你一句不离电路设计的术语“毛刺”。

毛刺是指电路中由于制造工艺不足或元件无意触发的门面,其危害是由于它的无法预测的特性并在电路运行时不断地改变,这给电路调试和设计带来了不小的挑战。

由于毛刺的存在,电路调试时间变长,而且不可预测性是其最大的危害,它可能会破坏电路功能,甚至有可能烧毁电路。

因此,毛刺需要设计师仔细考虑并采取措施去消除它,保证电路的稳定性和正常运行。

消除毛刺的常见方法有很多,比如,接地完善,因为在两个电源相连的地方,就可能产生毛刺;还有电容和电感,能够抑制持续时间较短且强度较大的毛刺;另一种比较常见的手段是增加门面稳定性,延长门面时间,使毛刺变得更加稳定。

除了上述介绍的常见方法,也可以采取更高级的方法,比如用软件去实现正确的状态,或者采用超低噪音的元件,以达到最佳的抑制余波的结果,最后确保电路的准确性和可靠性。

总之,毛刺是电路设计中一个很棘手的问题,它的存在会严重影响电路的调试和运行,为了保证电路正常运行,我们需要综合考虑多重因素去进行抑制和消除毛刺。

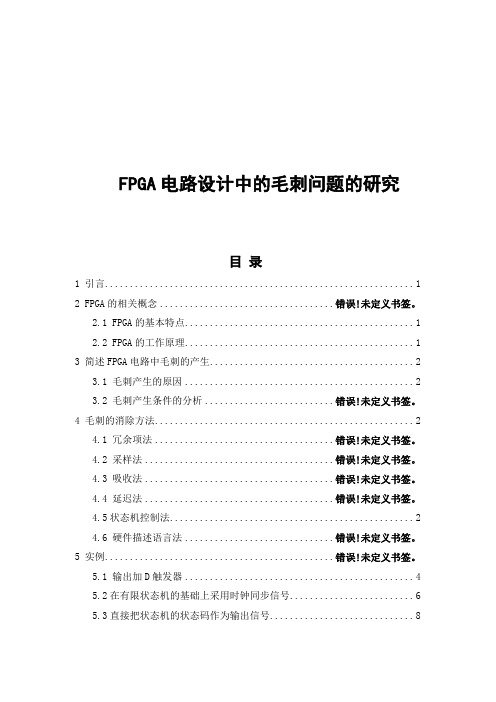

电路设计中的毛刺问题的研究

FPGA电路设计中的毛刺问题的研究目录1 引言 (1)2 FPGA的相关概念.................................. 错误!未定义书签。

2.1 FPGA的基本特点 (1)2.2 FPGA的工作原理 (1)3 简述FPGA电路中毛刺的产生 (2)3.1 毛刺产生的原因 (2)3.2 毛刺产生条件的分析......................... 错误!未定义书签。

4 毛刺的消除方法 (2)4.1 冗余项法................................... 错误!未定义书签。

4.2 采样法..................................... 错误!未定义书签。

4.3 吸收法..................................... 错误!未定义书签。

4.4 延迟法..................................... 错误!未定义书签。

4.5状态机控制法 (2)4.6 硬件描述语言法............................. 错误!未定义书签。

5 实例............................................. 错误!未定义书签。

5.1 输出加D触发器 (4)5.2在有限状态机的基础上采用时钟同步信号 (6)5.3直接把状态机的状态码作为输出信号 (8)6 结语 (10)参考文献 (11)致谢 (12)FPGA电路设计中的毛刺问题的研究摘要:目前,FPGA器件已经越来越广泛地应用在数字电路设计等领域,但它的毛刺问题却成为一个影响其可靠性和精确性的重要因素。

本文探讨了毛刺产生的原因及产生的条件,以计数器和乘法器为例对解决方案进行了深入具体地分析,总结了多种不同的解决方法,并且通过仿真说明这几种方法能够有效地消除或在一定程度上减少数字电路设计中出现的毛刺。

接线端子常见的致命故障及预防措施

接线端子常见的致命故障及预防措施接线端子是电气设备中重要的连接部件之一,其质量安全直接关系到设备的正常运行和人身安全。

常见的接线端子致命故障有线路松动、短路、烧毁等问题,下面将详细介绍这些问题的原因及预防措施。

一、线路松动问题。

线路松动可能导致接线端子之间的接触不良,进而引发电气设备的故障。

这种情况的原因往往是由于电器设备使用时间长、接线端子锁紧螺母松动或是电器设备受到机械振动导致的。

预防措施:1.定期检查电器设备中的接线端子,对于有松动的连接,应及时进行紧固处理,以确保接触良好。

2.可在接线端子旁边加装防松螺母,并且定期检查和紧固。

二、短路问题。

短路是指两个或者多个导线之间接触到了彼此或接触到其他的导体或外壳,引起两个不同电位之间的瞬间短路,产生电弧而导致电器设备故障。

预防措施:1.设计时应合理布置导线,避免导线的交叉和重叠,尽量减少导线之间的距离,避免短路的发生。

2.在导线之间加装隔离套管或绝缘带进行隔离,防止导线之间的直接接触。

3.在接线端子上使用绝缘材料,例如,绝缘套管、绝缘盖子等,提高接线端子的绝缘性能。

三、烧毁问题。

接线端子烧毁通常是由于接线端子内部接触不良、接触电阻过大、使用电流超过额定电流等原因引起的。

这种情况会严重影响设备的正常使用,造成设备损坏甚至触电事故。

预防措施:1.选择质量可靠的接线端子,具有良好的导电性和导热性能,并能承受相应电流的额定负荷,避免接线端子过载。

2.定期检查接线端子的状态,如发现有接线端子发热等异常情况,应及时进行处理,以避免短路和烧毁。

3.使用专业的工具和技术进行接线端子的安装,确保接线的牢固。

综上所述,接线端子的常见致命故障包括线路松动、短路和烧毁,可能导致电器设备故障和触电事故。

对于这些故障,我们可以通过定期检查、紧固、使用适当的绝缘材料、布线合理以及选择质量可靠的接线端子等预防措施来降低发生概率,保障设备的正常运行和人身安全。

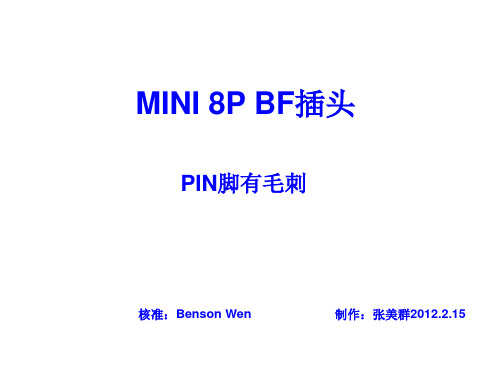

MINI 8P BF插头 PIN脚有毛刺 异常分析9D

核准:Benson Wen

制作:张美群2012.2.15

一、不良现象

• 2/15接客户反馈在进料检验时发现有产品锡脚有毛刺不良, 此不良可能会影响SMT打件后短路。

二、原因分析

1、经查证分析,此不良是Insert moding时因端子未完全放入模 具PIN槽内,在模具合模时有压端子边缘现象,导致端子被压 出毛刺;

四、改善、预防对策

• 2、对Insert moding模具锡脚PIN槽边缘,在每天上班前用纤 维油石进行抛光,使端子放入时容易进入槽内;

四、改善、预防对策

• 3、宣导检验人员依最新的《QC工程图》执行检验工作, 加入对锡刺等不良的管控。

五、改善效果确认

• 1、2/16新交货产品,客户进料检验合格PASS,待继续踪; • 2、Insert moding 模具已改善OK。

端子未放到槽内,合模 时会压出锡刺。

二、原因分析

2、此毛刺是合模时压端子边缘,将镀层(SN)压成毛刺,用高 温(260度)进行接触,可被融化,可确定是被模具压出的锡 毛边。

二、原因分析

3、现场人员在检验过程有发现此不良,但看其在折完料后与锡 脚紧靠,没有搭接和可移动的可能便没有拦截。

三、临时措施

1、此批67.2K退回处理; 2、退货67.2K及厂内库存16.8K全部HOLD;待处理; 3、增加毛刷清洁锡脚上的锡刺;

三、临时措施

4、用CCD放大检查锡脚上的毛丝和锡刺。

四、改善、预防对策

• 1、Insert moding在放好端子后务必100%用铁块治具先预压 端子,保证端子完全在模具PIN槽内;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

接线端子产生毛刺原因分析

接线端子的好坏不仅在于良好的导电和绝缘材质,还在于产品外观。

产品外观一方面取决于接线端子产品的形状,另一方面取决于产品的边缘。

通常来说,接线端子生产商大都不会在形状上出问题,形状规则、材料完整即可;对于好的接线端子,产品边缘应该是光滑、平整的,没有多余的材料。

联捷销售人员在与顾客交谈中发现有些顾客竟误将劣质端子当做好的接线端子,颇为咋舌。

产品的外边缘,折角处,缝隙出经常出现多余的边缘,或者边缘不整齐,这种情况我们通常称作产品出毛刺或者非边。

接线端子非边现象是产品低档和低质的标志,在生产中应该引起注意。

接线端子产生毛刺的原因是什么,我们应该如何在生产中杜绝毛刺的产生从而提高产品的档次和质量呢?

原因不外乎两点:模具和生产过程。

首先是模具的设计,在模具的设计中我们需要模具设计师设计出最优秀的图纸。

其次,在模具的制造中,我们需要用最好的材料,鉴于冶炼技术的限制,国内铁无论是在硬度还是强度上还都不能匹敌进口铁。

使用强度低的铁作为模具的主体材料时,通常在使用50万次左右就会出现明显的毛刺,所以联捷电气采用的模具铁是进口而且强度极高,在材料上杜绝了产品问题的出现。

其次是模具的加工工艺,在模具的加工工艺中一般有电脉冲,电子打光等,提高了模具的精准性。

其次,是我们的生产阶段。

生产中,很多工人都会急于把产品打满,所以在一开始就把注塑机的压力调到很高,但是这样对模具是有害的,长时间的*力通常会使模具变形,影响产品的质量,同时也浪费了电能。

带有毛刺的接线端子不仅影响产品美观,生产时还可能影响下道工序的定位,干扰工件测量精度,在进行电气连接时很可能对下一级电路产生影响。

所以买家在进行接线端子选购时应该仔细检查端子外观,避免上述现象发生。