modelsim时序仿真

用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)

用ModelSimSE进行 功能仿真和时序仿真的方法 (ALTERA篇)黄俊April 2007用ModelSim SE进行功能仿真和时序仿真的方法 (ALTERA篇)软件准备(1) QuartusII,本文截图是QuartusII 6.1界面的。

我个人认为,如果是开发StratixII或CycloneII或MAXII,用QuartusII6.0+SP1+SP2比较稳定。

(2) ModelSim SE. ALTERA仿真库要已经装好,安装仿真库的笔记已记录于《在ModelSimSE中添加ALTERA仿真库的详细步骤》中。

我电脑上装的是ModelSim SE6.1b。

例子程序的制作先在Quartus II里生成一个例子程序,以方便介绍三种仿真的方法。

步骤如下:1、新建一个工程(Project),工程名取lpm_shift, 器件选CycloneII EP2C5Q208C, 第三方的工具暂时都不选。

2、菜单栏上ToolsÆMegaWizard Plug-In Manager, 点Next,在storage中选LPM_SHIFTREG,输出文件格式根据习惯选一种语言,在这里以Verilog的为例,在右边的output file名字中加上lpm_shift。

点Next。

3、这个例子是做一个移位寄存器,调用lpm库,和cycloneII元件库,也正好可以作为对前面建好的ALTERA库的一个验证。

点可以查到该模块的使用说明和详细介绍。

移位寄存器比较简单,就不用细看了。

如下图设置.点Next.4、加上一个异步清零端,点Next,再点Next,最后点Finish.Add/Remove Files in Project…,6、点图标,选中生成的lpm_shift,点打开再点Add都加到项目中去。

7、在这里直接把lpm_shift.v当成顶层文件,就不需要再例化它了。

8、下面写一个简单的TestBench.a)Quartus II工具栏上点图标,选Verilog HDL;b)点,设文件名为top_tb;c)如下所述写一个简单的TestBench.(例子见附件)开始仿真z ModelSim仿真有很多种流程,下面我采用个人感觉比较好一个流程进行仿真验证:基于工程(Project)的流程Step1 新建一个工程Step2 添加文件到工程中去Step3 编译设计文件Step4 启动仿真器,指定顶层设计单元Step5 查看和调试结果z对的设计有三个阶段的仿真。

利用ModelSim实现时序仿真

1) 打开一个工程文件。

2) 打开Settings设置栏,选择EDA Tools Settings下的Simulation栏。

在右边出现的设置栏中将“Toolname”的下拉菜单选择“ModelSim(Verilog)”(如果工程用VHDL语言实现,则可以选择“ModelSim(VHDL)”;如果ModelSim使用的是for Altera的专用版本,则可以选择“ModelSim-Altera(Verilog)”或“ModelSim-Altera(VHDL)”)。

另外在设置栏中还有其他的核选框。

1. 如果选中“Maintain hierarchy”,则表示在做时序仿真时就能看到像在功能仿真的工程文件层次结构,可以找到定义的内部信号。

因为在做后仿时,源文件中的信号名称已经没有了,被映射为软件综合后自己生成的信号名,观察起来很不方便。

这个设置与ISE里综合右键属性的Keep Hierarchy选择YES的功能是一样的。

2. 如果选中“Generate netlist for functional simulation only”,则表示只能做功能仿真。

3) 点击“Start Compilation”按钮编译工程,完成之后在当前的工程目录下可以看到一个名为“Simulation”的新文件夹,下面的“ModelSim”文件夹下包括仿真需要的.vo网表文件和包含延迟信息的.sdo 文件。

4) 打开ModelSim软件(或者在Quartus下“Settings->EDA Tools Setting->Simulation”出现的设置栏中选中“Run this tool automatically after compilation”,直接从Quartus下调用ModelSim软件),可以在当前工程目录下新建一个Project。

在Project标签栏内点击右键,出现在快捷菜单中选择“Add toProject->Existing File…”。

Modelsim SE 进行时序仿真及altera库的添加

4.编译库

在主菜单中选【compile】→【compile】命令,对altera_primitives.v进行编译。

VHDL文件编译有所不同,LPM库的220model.vhd和220pack.vhd可以同时编译,MegaFunction库的先编译altera_mf_components.vhd文件,后编译altera_mf.vhd文件,Primitiv库先编译altera_primitive_components.vhd文件,后编译altera_primitive.vhd文件,元件库,如cyclone II库先编译cycloneii_atoms.vhd文件,后编译cycloneii_components.vhd文件,如果是其他系列的元件库则只要把对应的cycloneii改成其他系列的名称即可,如cyclone库则文件改为cyclone_atoms.vhd、cyclone_components.vhd或cyclone_atoms.v。

网上的很多教程都是把这些文件一起编译,这样适用于Verilog和VHDL混合仿真,但如果只用一种语言,如Verilog则完全没必要全部编译。这几个文件可分为Verilog组:220model.v、altera_mf.v、altera_primitives.v、cycloneii_atoms.v和VHDL组:220model.vhd、220pack.vhd、altera_mf.vhd、altera_mf_components.vhd,altera_primitives.vhd,altera_primitives_components.vhd,cycloneii_atoms.vhd,cycloneii_components.vhd。

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法

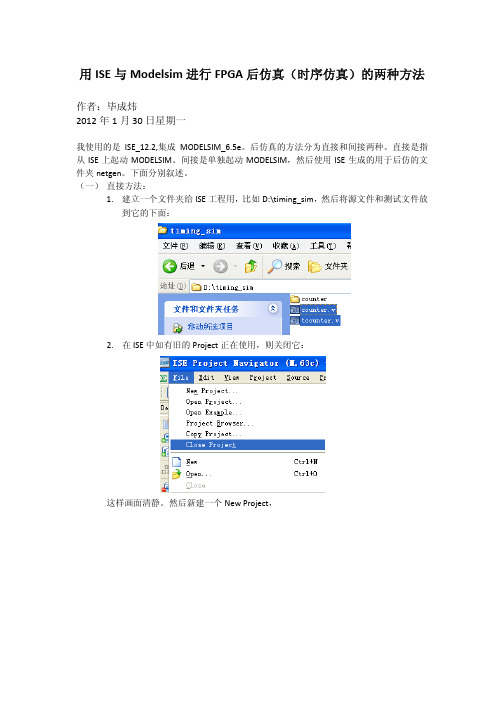

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法作者:毕成炜2012年1月30日星期一我使用的是ISE_12.2,集成MODELSIM_6.5e。

后仿真的方法分为直接和间接两种。

直接是指从ISE上起动MODELSIM。

间接是单独起动MODELSIM,然后使用ISE生成的用于后仿的文件夹netgen。

下面分别叙述。

(一) 直接方法:1.建立一个文件夹给ISE工程用,比如D:\timing_sim,然后将源文件和测试文件放到它的下面:2.在ISE中如有旧的Project正在使用,则关闭它:这样画面清静。

然后新建一个New Project,点Next,选好器件和仿真器:点Next,点Finish.为了能够在ISE中直接唤起MODELSIM,还需要一些设置,主要是两处:双击器件:保证下图红圈处选中你要的仿真器:点OK后,在主菜单中点:保证在红圈处指定好MODELSIM执行文件所在的位置编译仿真库可以在这里双击Compile HDL Simulation Libraries,也可以在C:\Xilinx\12.2\ISE_DS\ISE\bin\nt下面找到,双击它,注意红圈处所标的是你的ISE版本所支持的MODELSIM版本,不能低于它。

否则仿真过程可能出问题。

点Next,点Next,选定你针对什么器件编译仿真库,点Next,点Next,注意,ISE可能最初不带modelsim.ini,它在此步会自动生成这个文件,并且是可写的,即它的“只读”属性是已经自动去掉的。

生成仿真库的映射关系自动写入了ISE的这个modelsim.ini,位于C:\Xilinx\12.2\ISE_DS\ISE\bin\nt,但是,它并不会自动去更新MODELSIM软件的modelsim.ini,而且MODELSIM使用的是它自己的modelsim.ini,位于C:\modeltech_6.5e。

所以需要把ISE的modelsim.ini中的映射关系再COPY到MODELSIM自己的modelsim.ini中。

modelsim时序仿真最低时间间隔

modelsim时序仿真最低时间间隔

当我们进行数字电路设计时,时序仿真是必不可少的一步。

而在进行时序仿真时,我们需要注意一个重要的参数,即仿真的最低时间间隔。

在ModelSim中,最低时间间隔是指仿真时刻的最小精度,也就是仿真的时间分辨率。

这个参数的设置对于仿真结果的准确性和精度至关重要。

在进行时序仿真时,我们需要考虑到电路中各个信号的传输延迟和时序关系。

如果时间间隔设置得过大,仿真结果可能会出现误差,无法准确反映电路的真实行为。

而如果时间间隔设置得过小,不仅会增加仿真的计算量,还可能导致仿真时间过长,甚至无法完成仿真。

所以,在设置最低时间间隔时,我们需要根据电路的复杂程度和仿真的需求来进行选择。

一般来说,对于大多数数字电路设计,设置一个合适的最低时间间隔就能够满足仿真需求。

在实际操作中,我们可以根据经验来选择一个合适的时间间隔,然后通过观察仿真结果的准确性和稳定性来进行调整。

总的来说,时序仿真的最低时间间隔对于仿真结果的准确性和精度有着重要的影响。

合理设置最低时间间隔可以提高仿真的效率和准确性,从而更好地验证和优化数字电路设计。

在使用ModelSim进行时序仿真时,我们应该根据电路的特点和仿真需求来选择合适的时间间隔,以获得准确而高效的仿真结果。

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法

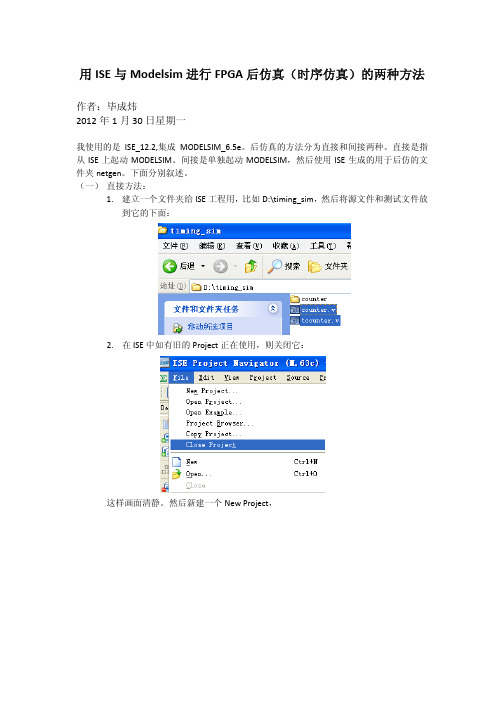

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法作者:毕成炜2012年1月30日星期一我使用的是ISE_12.2,集成MODELSIM_6.5e。

后仿真的方法分为直接和间接两种。

直接是指从ISE上起动MODELSIM。

间接是单独起动MODELSIM,然后使用ISE生成的用于后仿的文件夹netgen。

下面分别叙述。

(一) 直接方法:1.建立一个文件夹给ISE工程用,比如D:\timing_sim,然后将源文件和测试文件放到它的下面:2.在ISE中如有旧的Project正在使用,则关闭它:这样画面清静。

然后新建一个New Project,点Next,选好器件和仿真器:点Next,点Finish.为了能够在ISE中直接唤起MODELSIM,还需要一些设置,主要是两处:双击器件:保证下图红圈处选中你要的仿真器:点OK后,在主菜单中点:保证在红圈处指定好MODELSIM执行文件所在的位置编译仿真库可以在这里双击Compile HDL Simulation Libraries,也可以在C:\Xilinx\12.2\ISE_DS\ISE\bin\nt下面找到,双击它,注意红圈处所标的是你的ISE版本所支持的MODELSIM版本,不能低于它。

否则仿真过程可能出问题。

点Next,点Next,选定你针对什么器件编译仿真库,点Next,点Next,注意,ISE可能最初不带modelsim.ini,它在此步会自动生成这个文件,并且是可写的,即它的“只读”属性是已经自动去掉的。

生成仿真库的映射关系自动写入了ISE的这个modelsim.ini,位于C:\Xilinx\12.2\ISE_DS\ISE\bin\nt,但是,它并不会自动去更新MODELSIM软件的modelsim.ini,而且MODELSIM使用的是它自己的modelsim.ini,位于C:\modeltech_6.5e。

所以需要把ISE的modelsim.ini中的映射关系再COPY到MODELSIM自己的modelsim.ini中。

Modelsim的功能仿真和时序仿真

FPGA 设计流程包括设计输入,仿真,综合,生成,板级验证等很多阶段。

在整个设计流程中,完成设计输入并成功进行编译仅能说明设计符合一定的语法规范,并不能说明设计功能的正确性,这时就需要通过仿真对设计进行验证。

在FPGA 设计中,仿真一般分为功能仿真(前仿真)和时序仿真(后仿真)。

功能仿真又叫逻辑仿真,是指在不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证;而时序仿真是在布局布线后进行,它与特定的器件有关,又包含了器件和布线的延时信息,主要验证程序在目标器件中的时序关系。

在有些开发环境中,如Xilinx ISE 中,除了上述的两种基本仿真外,还包括综合后仿真,转换(post-translate)仿真,映射后(post-map)仿真等,这样做完每一步都可进行仿真验证,从而保证设计的正确性。

ModelSim 是Mentor Graphics 子公司MentorTechnology 的产品,是当今最通用的FPGA 仿真器之一。

ModelSim 功能强大,它支持FPGA 设计的各个阶段的仿真,不仅支持VHDL 仿真,Verilog仿真,而且支持VHDL 和Verilog 混合仿真。

它不仅能做仿真,还能够对程序进行调试,测试代码覆盖率,对波形进行比较等。

ModelSim 有很多版本,像ModelSim/SE 是首要版本,除此之外还有ModelSim/XE 和ModelSim/AE,分别是为Xilinx 公司和Altera 公司提供的OEM 版,其中已包含各公司的库文件,故用特定公司OEM 版进行仿真时就不需编译该公司的库了。

用ModelSim 进行功能仿真进行功能仿真首先要检查设计的语法是否正确;其次检查代码是否达到设计的功能要求。

下文主要介绍仿真步骤和测试激励的加载。

仿真步骤(1)建立库并映射库到物理目录因为用ModelSim 进行仿真是建立在仿真库的基础上的(此处进行的是功能仿真,因而不用编译特定厂商的库),所以首先要建立库并把库映射到实际的物理路径。

modelsim实验教程

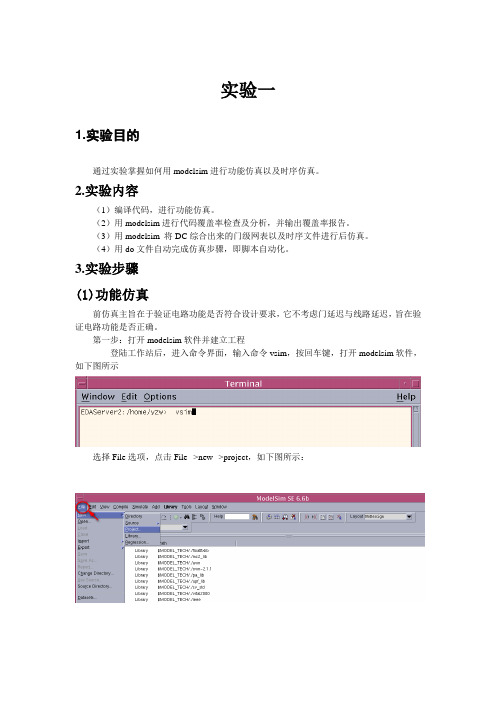

实验一1.实验目的通过实验掌握如何用modelsim进行功能仿真以及时序仿真。

2.实验内容(1)编译代码,进行功能仿真。

(2)用modelsim进行代码覆盖率检查及分析,并输出覆盖率报告。

(3)用modelsim 将DC综合出来的门级网表以及时序文件进行后仿真。

(4)用do文件自动完成仿真步骤,即脚本自动化。

3.实验步骤(1)功能仿真前仿真主旨在于验证电路功能是否符合设计要求,它不考虑门延迟与线路延迟,旨在验证电路功能是否正确。

第一步:打开modelsim软件并建立工程登陆工作站后,进入命令界面,输入命令vsim,按回车键,打开modelsim软件,如下图所示选择File选项,点击File-->new-->project,如下图所示:然后弹出如下界面,需要给所建立的工程起名,为了方便管理,工程名可以与顶层模块名字相一致。

Project Location 一栏表示的是工程所在目录,work代表工作库,里面包含所有编译过的文件。

输入工程名,并确定了工程所在位置后,点OK。

第二步:加入源文件并编译建立好工程后,会弹出下图所示窗口,可以选择Create New File来在modelsim中直接编辑代码文件,也可以选择Add Existing File加入已有的源文件。

也可以通过选择File-->new-->source来编辑源文件,如下图所示:加入源文件后,可以鼠标选择源文件,点击右键Compile-->Compile Selected来编译源文件。

也可以点击直接编译源文件。

选择,可以编译工程里面所有的源文件。

在Transcript窗口中可以查看编译结果。

如果有错误,可以双击错误提示,改正错误,再编译。

第三步:仿真源文件编译成功证明源代码没有语法错误,启动仿真器对源文件进行仿真。

选择Simulate-->Start Simulation或者点击按钮,会弹出一个选择框,将Enable Optimization 选项勾掉,这是仿真优化选项,会对时钟等进行优化,在功能仿真阶段不需要优化时钟,在后续布局布线中会对其进行优化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

利用ModelSim SE6.0C实现时序仿真

时间:2007-04-05 来源: 作者: 点击:2743 字体大小:【大中小】

1) 打开一个工程文件。

2) 打开Settings设置栏,选择EDA Tools Settings下的Simulation栏。

在右边出现的设置栏中将“Tool name”的下拉菜单选择“ModelSim(Verilog)”(如果工程用VHDL语言实现,则可以选择“ModelSim(VHDL)”;如果ModelSim使用的是for Altera的专用版本,则可以选择“ModelSim-Altera(Verilog)”或“ModelSim-Altera(VHDL)”)。

另外在设置栏中还有其他的核选框。

1.如果选中“Maintain hierarchy”,则表示在做时序仿真时就能看到像在功能仿真的工

程文件层次结构,可以找到定义的内部信号。

因为在做后仿时,源文件中的信号名

称已经没有了,被映射为软件综合后自己生成的信号名,观察起来很不方便。

这个

设置与ISE里综合右键属性的Keep Hierarchy选择YES的功能是一样的。

2.如果选中“Generate netlist for functional simulation only”,则表示只能做功能仿真。

3) 点击“Start Compilation”按钮编译工程,完成之后在当前的工程目录下可以看到一个名为“Simulation”的新文件夹,下面的“ModelSim”文件夹下包括仿真需要的.vo网表文件和包含延迟信息的.sdo文件。

4) 打开ModelSim软件(或者在Quartus下“Settings->EDA Tools Setting->Simulation”出现的设置栏中选中“Run this tool automatically after compilation”,直接从Quartus下调用ModelSim软件),可以在当前工程目录下新建一个Project。

在Project标签栏内点击右键,出现在快捷菜单中选择“Add to Project->Existing File…”。

加入当前工程目录的

“\Simulation\ModelSim\”路径下的.vo文件、TestBench文件和对应当前工程所选择器件的网表文件。

比如:当前工程选择的器件是Cyclone系列,Quartus安装目录在“C:\altera”路径下。

因此需要在“C:\altera\quartus50\eda\sim_lib”路径下找到“cyclone_atom.v”的网表文件导入到ModelSim下的Project。

如果是其他器件亦是如此,只要在此目录下找到对应有“_atom”后缀的.v文件。

当然整个大前提是ModelSim SE版本已经加入了Alterta的仿真库,不过ModelSim-Altera版本就不会存在这样的问题。

5) 在出现的Project标签栏的快捷菜单中选择“Add to Project->Simulation Configuration”,会出现如上图所示的名为“Simulation1”的仿真配置。

右键点击选择“Properties”,弹出的“Simulation Properties”对话框中有几个标签栏。

在“Design”标签栏内需要选择仿真的文件,也就是TestBench文件。

在“SDF”标签栏内需要选择包含延迟信息的文件,即Quartus下生成的.sdo文件。

这里建议将.sdo文件与ModelSim的工程文件(.mpf文件)放在同一个目录下,不然ModelSim会报类似无法读取.sdo文件的错误。

当加入.sdo文件时,需要在如下图所示的“Apply to Region”的编辑框内填写延迟信息文件作用的区域。

举个例子来说明:

1.TestBench文件中定义了测试文件的Module名称为ConvEncdTestBnch。

2.TestBench文件中调用待测顶层文件的实例名为top_encode_1。

(top_encode

top_encode_1(clk, rst, dataIn, serialData, parData);这是TestBench文件中调用顶层的语句)

3.所以在作用区域内需要填写“/ConvEncdTestBnch/top_encode_1”。

6) 右键点击名为“Simulation1”的仿真配置,快捷菜单中选择“Execute”命令,执行仿真。

7) 指定延时文件sdo 路径时,特别注意“域”的指定,否则用户会在timing 仿真中报load error “can’t find instance file”. 指定的域可以从sim标签页查看sim 的top 层,或要仿真的对象。

另外,时序仿真时,一定要记住要把顶层top.v 用top.vo 替换。

同时要确保预编译的库中每个库的名字必需遵循altera的要求,比如:cylcone 的device 库必需命名为cycclone, maxii 的device命名为maxii, flex10Ke 和acex1K 都命名为flex10Ke,详细查看文档附件。

Simulation.pdf

8) 提供一个testbench 的模板。

利用ModelSim SE6.0C实现功能仿真

功能仿真流程比较简单,一般不会出现什么问题,这里不再多述。