半导体制程概论chapter3

半导体制程简介PPT课件讲义教材

高温电弧炉还原

无水氯化氢

馏

纯

化

3-7cm块状硅块 (99.9…9%)

多晶硅棒

SiHCl3

敲碎

氢气还原及CVD法

单晶生长技术

◆ 柴氏长晶法 : 82.4% ◆ 磊晶法 : 14.0% ◆ 浮融带长晶法 : 3.3% ◆ 其它 : 0.2%

(1993年市场占有率)

长晶程序(柴式长晶法)

硅金属及掺杂质的融化 颈部 (Meltdown)

半导体制程简介

半导体制造流程

Front-End 晶圆制造 晶圆针测

Back-End

封装

测试

晶粒(Die)

成品

半导体制程分类

◆ I. 晶圆制造 ◆ II.晶圆处理 ◆ III.晶圆针测 ◆ IV.半导体构装 ◆ V.半导体测试

I.晶圆制造

晶圆制造流程

晶圆材料

多晶硅 原料制造

单晶 生长

晶圆 成形

(C)

已显影光阻 (E)

薄膜

二氧化硅

晶圆

显影

(D)

(F)

晶圆 蚀刻

晶圆 离子植入

参杂物

晶圆 去除光阻

IC制程简图(三)

(G)

金属层

(I)

晶圆

金属沉积

(H)

(J)

晶圆 微影制程

晶圆 金属蚀刻

晶圆 去除光阻

III.晶圆针测

晶圆针测示意图

探针卡 针测机

晶圆针测流程图

晶圆生产 Wafer processing

◆ 晶棒黏着 ◆ 切片 ◆ 晶圆清洗 ◆ 规格检验

内径切割机

晶边圆磨(Edge contouring)

◆ 目的

防止晶圆边缘碎裂 防止热应力之集中 增加光阻层在边缘之平坦度

半导体制程简=PPT课件

– 另外,在去除光 阻止后,通常还 需要有一步清洗, 以保证晶园表面 的洁净度。

-

30

2.7 金属蚀刻

• Metal Etch

– 金属蚀刻用于制作芯片中的金属导线。 – 导线的形状由Photo制作出来。 – 这部分工作也使用等离子体完成。

-

31

2.8 薄膜生长

– Develop & Bake

• 曝光完毕之后,晶园送回Track进行显影,洗掉被曝 过光的光阻。

• 然后再进行烘烤,使没有被洗掉的光阻变得比较坚硬 而不至于在下一步蚀刻的时候被破坏掉。

-

24

2.4 酸蚀刻

• Acid Etch

– 将没有被光阻覆盖的薄膜腐蚀掉,是酸蚀刻的 主要任务。

– 蚀刻完毕之后,再将光阻洗去。

• 一般而言通常使用 正光阻。只有少数 层次采用负光阻。

-

20

• 曝光

– Exposure

• 曝光动作的目的是将光罩上的图形传送到晶园上。 • 0.13um,0.18um就是这样做出来的。 • 曝光所采用的机台有两种:Stepper和Scanner。

-

21

• 左图是当今 市场占有率 最高的ASML 曝光机。

半导体制程简介

——芯片是如何制作出来的

-

1

基本过程

• 晶园制作 – Wafer Creation

• 芯片制作 – Chip Creation

• 后封装 – Chip Packaging

-

2

第1部分 晶园制作

-

3

1.1 多晶生成

• Poly Silicon Creation 1

– 目前半导体制程所使用的主要原料就是晶园 (Wafer),它的主要成分为硅(Si)。

第三章半导体制造工艺简介ppt课件

3 工艺流程

❖ 以上工艺重复、组合使用,就形成集成电路 的完整制造工艺。

❖ 光刻掩模版〔mask):版图完成后要交付给 代工厂,将版图图形转移到晶圆上,就需要 经过一个重要的中间环节——制版,即制造 一套分层的光刻掩膜版。

3 工艺流程

❖ 制版——光刻掩膜版就是讲电路版图的各个 层分别转移到一种涂有感光材料的优质玻璃 上,为将来再转移到晶圆做准备,这就是制 版。

扩散和离子注入的对比

离子注入

注入损伤

❖ 注入损伤:带有能量的离子进入半导体衬底, 经过碰撞和损失能量,最后停留下来。

❖ 电子碰撞:电子激发或新的电子空穴对产生 ❖ 原子核碰撞:使原子碰撞,离开晶格,形成

损伤,也称晶格无序

晶格无序

退火

❖ 由于离子注入所造成的损伤区及无序团,使 迁移率和寿命等半导体参数受到严重影响。

化学气相淀积

❖ CVD技术具有淀积温度低、薄膜成分和厚度 易于控制、均匀性和重复性好、台阶覆盖优 良、适用范围广、设备简单等一系列优点。 利用CVD方法几乎可以淀积集成电路工艺中 所需要的各种薄膜,例如掺杂或不掺杂的 sio2 、多晶硅、非晶硅、氮化硅、金属(钨、 钼)等。

❖ 作用:外延层,二氧化硅膜,多晶硅膜,氮 化硅膜

3.2 工艺流程

❖ 材料制备

1 制造工艺简介

❖ (a〕n型硅晶片原材料〔b〕氧化后的晶片

1 制造工艺简介

❖ (c〕涂敷光刻胶〔d〕光刻胶通过掩膜版曝 光

1 制造工艺简介

❖ (a〕显影后的晶片〔b〕SiO2去除后的晶片 ❖ 氧化工艺

1 制造工艺简介

❖ (c〕光刻工艺处理后的晶片 ❖ (d〕扩散或离子注入形成PN结 ❖ 光刻和刻蚀工艺;扩散和离子注入工艺

复旦半导体工艺教材Chapter-3

➢ Local Oxidation of Silicon (LOCOS) ➢ Modified LOCOS ➢ Non-LOCOS isolation

III. Basic structure and advantage of CMOS

CMOS inverter—basic element of CMOS IC

VI

NMOS PMOS VO

IDD

VI<VTN

Off

On

VDD

0

VI>VDD-VTP

On

Off

0

0

VTN<VI< VDD-VTP Trans. Trans. Trans. 0

MISFET structure of Lilienfeld: Al/Al2O3/CuS Substrate: CuS (semiconductor)

Dielectric gate: Al2O3 (10-4 mm) Gate electrode: Al (100V)

CuS

D

S

Electric field: 100V/10-4mm=107V/cm

➢ Stable and uniform threshold voltage (VT) ➢ Large and stable driving current (ID)-high surface carrier mobility ➢ Low leakage/sub-threshold current ➢ Large transconductance (gm=dID/dVG) ➢ High switching speed/low RC product ➢ Long-term reliability ➢ Low voltage, low power operation

半导体制程概论

分解

e-

A

B

分子

自由基

B A

e-

電漿蝕刻

• 氧化物蝕刻製程,在電漿中使用CF4 產生氟(F)的自由基e + CF4 CF3 + F + e 4F + SiO2 SiF4 + 2O

半导体制程概论

目標

• 列出至少三種使用電漿的IC製程 • 列出電漿中重要的三種碰撞 • 描述平均自由徑 • 解釋電漿在蝕刻和化學氣相沉積製程的好處 • 說出至少兩種高密度電漿系統

討論的主題

• 什麼是電漿? • 為什麼使用電漿? • 離子轟擊 • 電漿製程的應用

電漿製程的應用

• 化學氣相沉積 • 蝕刻 • 物理氣相沉積 • 離子佈植 • 光阻剝除 • 製程反應室的的乾式清洗

• 電子和中性原子或分子碰撞 • 把軌道電子「敲離」核的束縛

離子化

• 游離碰撞產生電子和離子 • 維持電漿的穩定

e- + A

A+ + 2 e-

離子化的說明

原子核

原子核

自由電子入射 撞擊軌道電子

軌道電子

兩個自由電子

激發-鬆弛

e- + A

A* + e-

A* A + hn (光)

• 不同的原子/分子有不同的頻率,也就是為什麼不同的氣體會發出不同的顏色.

氮化鈦分子從鈦靶表面濺射出來而使之沉積在晶圓表面

表7.1 矽烷的分解

碰撞

副產品

形成所需的能量

e- + SiH4

SiH2 + H2 + eSiH3 + H + eSi + 2 H2 + eSiH + H2 + H + eSiH2* + 2H + eSi* + 2H2 + eSiH2+ + H2 + 2 eSiH3+ + H + 2 eSi+ + 2H2 + 2 eSiH+ + H2 + H + 2 e-

半导体制程及原理概述

製程及原理概述半導體工業的製造方法是在矽半導體上製造電子元件(產品包括:動態記憶體、靜態記億體、微虛理器…等),而電子元件之完成則由精密複雜的積體電路(Integrated Circuit,簡稱IC)所組成;IC之製作過程是應用晶片氧化層成長、微影技術、蝕刻、清洗、雜質擴散、離子植入及薄膜沉積等技術,所須製程多達二百至三百個步驟。

隨著電子資訊產品朝輕薄短小化的方向發展,半導體製造方法亦朝著高密度及自動化生產的方向前進;而IC製造技術的發展趨勢,大致仍朝向克服晶圓直徑變大,元件線幅縮小,製造步驟增加,製程步驟特殊化以提供更好的產品特性等課題下所造成的良率控制因難方向上前進。

半導體業主要區分為材料(矽品棒)製造、積體電路晶圓製造及積體電路構裝等三大類,範圍甚廣。

目前國內半導體業則包括了後二項,至於矽晶棒材料仍仰賴外國進口。

國內積體電路晶圓製造業共有11家,其中聯華、台積及華邦各有2個工廠,總共14個工廠,目前仍有業者繼紙擴廠中,主要分佈在新竹科學園區,年產量逾400萬片。

而積體電路構裝業共有20家工廠,遍佈於台北縣、新竹縣、台中縣及高雄市,尤以加工出口區為早期半導體於台灣設廠開發時之主要據點。

年產量逾20億個。

原理簡介一般固體材料依導電情形可分為導體、半導體及絕緣體。

材料元件內自由電子濃度(n值)與其傳導率成正比。

良好導體之自由電子濃度相當大(約1028個e-/m3),絕緣體n值則非常小(107個e-/m3左右),至於半導體n值則介乎此二值之間。

半導體通常採用矽當導體,乃因矽晶體內每個原子貢獻四個價電子,而矽原子內部原子核帶有四個正電荷。

相鄰原子間的電子對,構成了原子間的束縛力,因此電子被緊緊地束縛在原子核附近,而傳導率相對降低。

當溫度升高時,晶體的熱能使某些共價鍵斯鍵,而造成傳導。

這種不完全的共價鍵稱為電洞,它亦成為電荷的載子。

如圖1.l(a),(b)於純半導體中,電洞數目等於自由電子數,當將少量的三價或五價原子加入純矽中,乃形成有外質的(extrinsic)或摻有雜質的(doped)半導體。

半导体概论

半导体生产流程所谓的半导体,是指在某些情况下,能够导通电流,而在某些条件下,又具有绝缘体效用的物质;而至于所谓的IC,则是指在一半导体基板上,利用氧化、刻蚀、扩散等方法,将众多电子电路组成各式二极管、晶体管等电子组件,作在一微小面积上,以完成某一特定逻辑功能(例如:AND、OR、NAND等),进而达成预先设定好的电路功能。

自1947年12月23日第一个晶体管在美国的贝尔实验室(Bell Lab)被发明出来,结束了真空管的时代,到1958年TI开发出全球第一颗IC成功,又意谓宣告晶体管的时代结束,IC的时代正式开始。

从此开始各式IC不断被开发出来,集成度也不断提升。

从小型集成电路(SSI),每颗IC包含10颗晶体管的时代;一路发展MSI、LSI、VLSI、ULSI;MSI(Middle-scale integration)中等规模集成电路;LSI(Large-scale integration)大规模集成电路;VLSI(Very-Large-scale integration)甚大规模集成电路;ULSI(Ultra-Large-scale integration)超大规模集成电路再到今天,短短50年时间,包含千万个以上晶体管的集成电路已经被大量生产,并应用到我们的生活的各领域中来,为我们的生活带来飞速的发展。

不能想象离开半导体产业我们的生活将会怎样,半导体技术的发展状况已成为一个国家的技术状况的重要指针,电子技术也成为一个国家提高国防能力的重要途径。

半导产品类别目前的半导体产品可分为集成电路、分离式组件、光电半导体等三种。

A.集成电路(IC),是将一电路设计,包括线路及电子组件,做在一片硅芯片上,使其具有处理信息的功能,有体积小、处理信息功能强的特性。

依功能可将IC分为四类产品:内存IC、微组件、逻辑IC、模拟IC。

B.分离式半导体组件,指一般电路设计中与半导体有关的组件。

常见的分离式半导体组件有晶体管、二极管、闸流体等。

【2017年整理】图解半导体制程概论

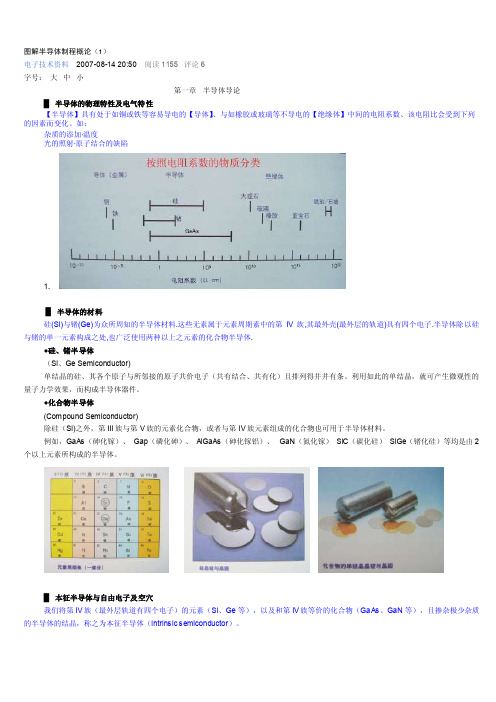

图解半导体制程概论(1)电子技术资料 2007-08-14 20:50 阅读1155 评论6字号:大中小第一章半导体导论█半导体的物理特性及电气特性【半导体】具有处于如铜或铁等容易导电的【导体】、与如橡胶或玻璃等不导电的【绝缘体】中间的电阻系数、该电阻比会受到下列的因素而变化。

如:杂质的添加·温度光的照射·原子结合的缺陷1.█半导体的材料硅(Si)与锗(Ge)为众所周知的半导体材料.这些无素属于元素周期素中的第IV族,其最外壳(最外层的轨道)具有四个电子.半导体除以硅与锗的单一元素构成之处,也广泛使用两种以上之元素的化合物半导体.●硅、锗半导体(Si、Ge Semiconductor)单结晶的硅、其各个原子与所邻接的原子共价电子(共有结合、共有化)且排列得井井有条。

利用如此的单结晶,就可产生微观性的量子力学效果,而构成半导体器件。

●化合物半导体(Compound Semiconductor)除硅(Si)之外,第III族与第V族的元素化合物,或者与第IV族元素组成的化合物也可用于半导体材料。

例如,GaAs(砷化镓)、Gap(磷化砷)、AlGaAs(砷化镓铝)、GaN(氮化镓)SiC(碳化硅)SiGe(锗化硅)等均是由2个以上元素所构成的半导体。

█本征半导体与自由电子及空穴我们将第IV族(最外层轨道有四个电子)的元素(Si、Ge等),以及和第IV族等价的化合物(GaAs、GaN等),且掺杂极少杂质的半导体的结晶,称之为本征半导体(intrinsic semiconductor)。

●本征半导体(intrinsic semiconductor)当温度十分低的时候,在其原子的最外侧的轨道上的电子(束缚电子(bound electrons)用于结合所邻接的原子,因此在本征半导体内几乎没有自由载子,所以本征半导体具有高电阻比。

●自由电子(free electrons)束缚电子若以热或光加以激发时就成为自由电子,其可在结晶内自由移动。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PPT学习交流

20

電容器

多晶矽2

氧化層

多晶矽1

平行板

介電質層 多晶矽2

介電質層

多晶

矽

矽

多晶矽1

重摻雜 矽

堆疊

深溝槽式PPT学习交流Fra bibliotek21金屬間連線 與 RC時間延遲

介電質, l

金屬, r

I

d w

PPT学习交流

22

二極體

• P-N接面 • 僅准許電流在正向偏壓的時候通過.

PPT学习交流

23

二極體

12

電洞移動的示意說明

導帶, Ec

導帶, Ec

導帶, Ec

電子

Eg = 1.1 eV 電子 Ea ~ 0.05 eV

Eg = 1.1 eV

電洞 價帶, Ev

電洞 價帶, Ev

電子

Eg = 1.1 eV

價帶, Ev

電洞

PPT学习交流

13

摻雜物濃度和電阻係數

電阻係數

N-型, 磷

P-型, 硼

摻雜物濃度

• 矽 V0 ~ 0.7 V

PPT学习交流

26

二極體的 I-V曲線

I

-I0

PPT学习交流

V

27

雙載子電晶體

• PNP 或 NPN接面 • 當作開關使用 • 放大器 • 類比電路 • 快速、高功率元件

PPT学习交流

28

NPN 和 PNP電晶體

E

E

B C

B

N

PN

C

C

E

B C

B

P

NP

E

PPT学习交流

PPT学习交流

8

矽的單晶結構

共享電子

Si

Si

Si

Si

Si

Si

Si

Si

- Si

PPT学习交流

9

為什麼用矽

• 豐度高, 價格不貴 • 容易在熱氧化過程中成長一層二氧化矽. • 熱穩定性 • 二氧化矽具強介電質及相對容易生成二氧化

矽可以做為擴散摻雜的遮蓋

PPT学习交流

10

N-型 (砷) 摻雜矽及施體能階

VD > 0

SiO2

p+

源極

金屬匣極

p+

SiO2

-------

p+ + + + + + + +

p+

n-Si

n-Si

汲極

源極

汲極

沒有電流

正電荷

PPT学习交流

35

金氧半場效電晶體

PPT学习交流

36

MOSFET 和飲水機(Drinking Fountain)

MOSFET

飲水機

• 源極, 汲極, 匣極 • 源極 / 汲極偏壓

Chapter 3 半導體基礎原理、元件 與製程

Hong Xiao, Ph. D.

PPT学习交流

1

目標

• 從元素週期表上至少可以認出兩種半導體材料 • 列出n型和p型的摻雜物 • 描述一個二極體和一個MOS 電晶體列出在半導

體工業所製造的三種晶片 • 列出至少四種在晶片製造上必備的基本製程

PPT学习交流

PPT学习交流

14

摻雜物濃度和電阻係數

• 摻雜物濃度越高, 提供的載體越多(電子或電洞) • 導電性越高,電阻係數越低 • 電子移動速度比電洞快 • 在相同的濃度下,N-型 矽比P-型矽的電阻係數

低

PPT学习交流

15

基本元件

• 電阻器 • 電容器 • 二極體 • 雙載子電晶體 • 金氧半場效電晶體

P型晶片

PPT学习交流

31

金屬氧化半導體電晶體

• 金屬氧化半導體 • 也稱作金氧半場效電晶體 (MOSFET) • 簡單對稱的結構 • 可做為開關, 有助於發展數位邏輯電路 • 在半導體工業中被廣泛的使用

PPT学习交流

32

NMOS 元件

基本結構

VG

VD

氧化層

n+

源極

金屬匣極

p-Si

n+

汲極

接地

VG VD

• 匣極加上偏壓電壓做 為開關(開)

• 電流從源極流到集極

• 源, 汲, 匣 閥 • 受壓力作用的源閥

• 對匣閥加壓 (按鈕)做為 開關(開)

• 電流從源極流到集極

PPT学习交流

37

基本電路

• Bipolar • PMOS • NMOS • CMOS • BiCMOS

PPT学习交流

38

不同基片的元件

2

主題

• 半導體是什麼? • 基本半導體元件 • 基本積體電路製程

PPT学习交流

3

半導體是什麼?

• 介於導體和絕緣體之間 • 藉摻雜物控制導電性 • 矽和鍺 • 半導體化合物

• 碳化矽,鍺化矽 • 砷化鎵, 磷化銦, 等.

PPT学习交流

4

元素週期表

PPT学习交流

5

半導體基片與摻雜物

基片

P-型 摻 雜物

V1

V2

P1

P2

• V1 > V2 , 有電流 • V1 < V2 , 沒有電流

• P1 > P2 , 有氣流 • P1 < P2 , 沒有氣流

PPT学习交流

24

圖3.14

過渡區(空乏區)

-- + +

-- + +

P

-- + +

N

-- + +

-- + +

Vn V0 Vp

PPT学习交流

25

內電壓

V0 kqTlnNnaNi2 d

PPT学习交流

16

電阻器

r

l

h

w

Rr l

wh

r:電阻係數

PPT学习交流

17

電阻器

• 通常以多晶矽來製作IC晶片上的電阻器 • 電阻的高低取決於長度、線寬、接面深度和摻

雜物濃度

PPT学习交流

18

電容器

l

h d

C hl

d

:介電質常數

PPT学习交流

19

電容器

• 電荷儲存元件 • 記憶體元件, 例如. DRAM • 挑戰: 在維持相同的電容量下降低電容的尺寸 • 高- 介電質材料

N-型 摻雜物

PPT学习交流

6

單原子的軌道示意圖與能帶

價殼層

導帶, Ec

原子核

能隙, Eg

價帶, Ev

PPT学习交流

7

能帶、能隙 和電阻係數

Eg = 1.1 eV

Eg = 8 eV

鋁 2.7 mW•cm

導體

鈉 4.7 mW•cm

矽~ 1010 mW•cm

半導體

二氧化矽 > 1020 mW•cm

絕緣體

Si

Si

導帶, Ec Si 額外

的電子

Ed ~ 0.05 eV

Si

As

Si

Eg = 1.1 eV

Si

Si - Si

價帶, Ev

PPT学习交流

11

P-型(硼) 摻雜矽及其受體能階

導帶, Ec

Si

Si

Si

電洞

Si

B

Si

Eg = 1.1 eV

Si

Si - Si

電子

價帶, Ev

Ea ~ 0.05 eV

PPT学习交流

29

NPN雙載子電晶體

射極

基極 集極

Al•Cu•Si

p+

n+ p

SiO2

n+

N型

p+

電子流

磊晶層

n+ 深埋層

P型基片

PPT学习交流

30

側壁基極接觸式NPN雙載子電晶體

CVD氧

化層

基極

射極

金屬

CVD氧 化層

集極

多晶矽 p n+

p

場區氧 化層

n 型磊晶層

場區氧 化層

n+

n+ 深埋層

CVD氧 化層

場區氧 化層

PPT学习交流

33

NMOS元件

VG = 0

正電荷

VD 電子流

VG > VT > 0

VD > 0

“金屬匣極

SiO2

n+

源極

n+

SiO2

+++++++

n+ - - - - - - -

n+

p-Si

p-Si

汲極

源極

汲極

沒有電流

負電荷

PPT学习交流

34

PMOS元件

VG = 0

負電荷 VD 電洞電流 VG < VT < 0