第三章数字逻辑

数字逻辑 第三章 加法器.ppt

四位二进制并行加法器

三、四位二进制并加法器的外部特性和逻辑符号 1.外部特性

图中,A4、A3、A2、A1 ------- 二进制被加数; B4、B3、 B2、B1 ------- 二进制加数; F4、 F3、 F2、 F1 ------相加产生的和数; C0 --------------------来自低位的进位输入; FC4 -------------------向高位的进位输出。

a3b1

+) 乘积 Z5 a3b2 Z4 a2b2 Z3

a2b1

a1b2 Z2

a1b1

Z1

因为: ☆1位二进制数乘法 法则和逻辑“与”运算法 则相同,“积”项aibj(i =1,2,3;j=1,2)可用 两输入与门实现。 ☆对部分积求和可用 并行加法器实现。 所以:该乘法运算电 路可由6个两输入与门和1 b2 个4位二进制并行加法器构 成。逻辑电路图如右图所 示。

四位二进制并行加法器

实现给定功能的逻辑电路图如下图所示。 1) 输入端A4、A3、A2、 A1输入8421码;

2) 而从另一输入端B4、 B3、B2、B1输入二进 制数0011; 3) 进位输入端C0接上“0”;

4) 可从输出端F4、F3、F2、 F1得到与输入8421码对

应的余3码。

四位二进制并行加法器

Z5 Z4 Z3 Z 2 Z1

F4 F3 F2 F 1 FC4 T 693 C0

0

A4 A3 A2 A1

B4 B 3 B2 B1

&

&

&

&

&

&

b1

a3

a2

a1 0 a 3

a2

a1

FA4

F3 C3

FA3

F2

《数字逻辑教案》

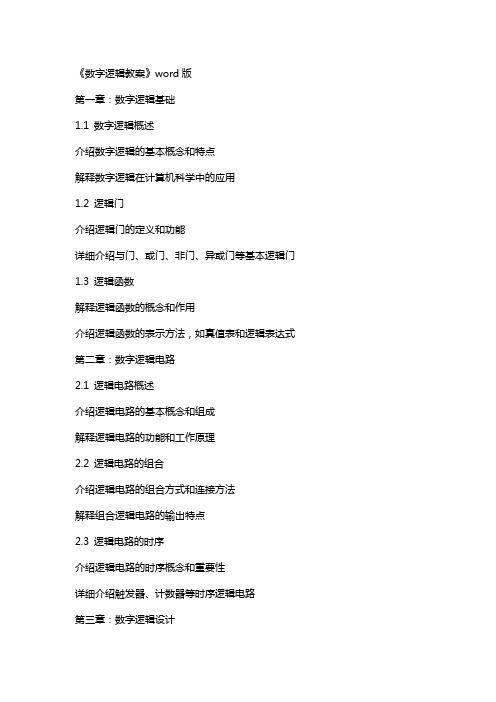

《数字逻辑教案》word版第一章:数字逻辑基础1.1 数字逻辑概述介绍数字逻辑的基本概念和特点解释数字逻辑在计算机科学中的应用1.2 逻辑门介绍逻辑门的定义和功能详细介绍与门、或门、非门、异或门等基本逻辑门1.3 逻辑函数解释逻辑函数的概念和作用介绍逻辑函数的表示方法,如真值表和逻辑表达式第二章:数字逻辑电路2.1 逻辑电路概述介绍逻辑电路的基本概念和组成解释逻辑电路的功能和工作原理2.2 逻辑电路的组合介绍逻辑电路的组合方式和连接方法解释组合逻辑电路的输出特点2.3 逻辑电路的时序介绍逻辑电路的时序概念和重要性详细介绍触发器、计数器等时序逻辑电路第三章:数字逻辑设计3.1 数字逻辑设计概述介绍数字逻辑设计的目标和方法解释数字逻辑设计的重要性和应用3.2 组合逻辑设计介绍组合逻辑设计的基本方法和步骤举例说明组合逻辑电路的设计实例3.3 时序逻辑设计介绍时序逻辑设计的基本方法和步骤举例说明时序逻辑电路的设计实例第四章:数字逻辑仿真4.1 数字逻辑仿真概述介绍数字逻辑仿真的概念和作用解释数字逻辑仿真的方法和工具4.2 组合逻辑仿真介绍组合逻辑仿真的方法和步骤使用仿真工具进行组合逻辑电路的仿真实验4.3 时序逻辑仿真介绍时序逻辑仿真的方法和步骤使用仿真工具进行时序逻辑电路的仿真实验第五章:数字逻辑应用5.1 数字逻辑应用概述介绍数字逻辑应用的领域和实例解释数字逻辑在计算机硬件、通信系统等领域的应用5.2 数字逻辑在计算机硬件中的应用介绍数字逻辑在中央处理器、存储器等计算机硬件部件中的应用解释数字逻辑在计算机指令执行、数据处理等方面的作用5.3 数字逻辑在通信系统中的应用介绍数字逻辑在通信系统中的应用实例,如编码器、解码器、调制器等解释数字逻辑在信号处理、数据传输等方面的作用第六章:数字逻辑与计算机基础6.1 计算机基础概述介绍计算机的基本组成和原理解释计算机硬件和软件的关系6.2 计算机的数字逻辑核心讲解CPU内部的数字逻辑结构详细介绍寄存器、运算器、控制单元等关键部件6.3 计算机的指令系统解释指令系统的作用和组成介绍机器指令和汇编指令的概念第七章:数字逻辑与数字电路设计7.1 数字电路设计基础介绍数字电路设计的基本流程解释数字电路设计中的关键概念,如时钟频率、功耗等7.2 数字电路设计实例分析简单的数字电路设计案例讲解设计过程中的逻辑判断和优化7.3 数字电路设计工具与软件介绍常见的数字电路设计工具和软件解释这些工具和软件在设计过程中的作用第八章:数字逻辑与数字系统测试8.1 数字系统测试概述讲解数字系统测试的目的和方法解释测试在保证数字系统可靠性中的重要性8.2 数字逻辑测试技术介绍逻辑测试的基本方法和策略讲解测试向量和测试结果分析的过程8.3 故障诊断与容错设计解释数字系统中的故障类型和影响介绍故障诊断方法和容错设计策略第九章:数字逻辑在现代技术中的应用9.1 数字逻辑与现代通信技术讲解数字逻辑在现代通信技术中的应用介绍数字调制、信息编码等通信技术9.2 数字逻辑在物联网技术中的应用解释数字逻辑在物联网中的关键作用分析物联网设备中的数字逻辑结构和功能9.3 数字逻辑在领域的应用讲述数字逻辑在领域的应用实例介绍逻辑推理、神经网络等技术中的数字逻辑基础第十章:数字逻辑的未来发展10.1 数字逻辑技术的发展趋势分析数字逻辑技术的未来发展方向讲解新型数字逻辑器件和系统的特点10.2 量子逻辑与量子计算介绍量子逻辑与传统数字逻辑的区别讲解量子计算中的逻辑结构和运算规则10.3 数字逻辑教育的挑战与机遇分析数字逻辑教育面临的挑战讲述数字逻辑教育对培养计算机科学人才的重要性重点和难点解析重点环节一:逻辑门的概念和功能逻辑门是数字逻辑电路的基本构建块,包括与门、或门、非门、异或门等。

《数字逻辑》第3章习题答案

题

【3-1】填空: (1) 逻辑代数中有三种最基本运算: 与 、 或 和 非 ,在此基础上又派生出五种基本运算, 分别为 与非 、 或非 、 异或 、 同或 、和 与或非 。 (2) 与运算的法则可概述为:有 0 出 0 ,全 1 出 1 ;类似地,或运算的法则为 有”1”出”1”, 全”0”出”0” 。 (3) 摩根定理表示为: A B = A B ; A B = A B 。 (4) 函数表达式 Y= AB C D ,则其对偶式为 Y ' = ( A B)C D 。 积的形式结果应为 M ( 0,1,2,4,5,8,9,10)。 (5) 函数式 F=AB+BC+CD 写成最小项之和的形式结果应为 m ((3,6,7,11,12,13,14,15)), 写成最大项之

0 0 1 1 1 1

1 1 0 0 1 1

0 1 0 1 0 1

1 1 0 0 1 0

【3-8】写出下列函数的反函数 F ,并将其化成最简与或式。 (1) F1 ( A D )( B C D)( AB C ) (2) F2 ( A B )( BCD E )( B C E )(C A) (3) F3 A B C A D (4) F4 ( A B)C ( B C ) D 解: (1) F1 AD C (2) F2 AB A C E (3) F3 AB AC A D (4) F4 BC C D ABD A B C 【3-9】用对偶规则,写出下列函数的对偶式 F ,再将 F 化为最简与或式。 (1) F1 AB B C A C (2) F2 A B C D (3) F3 ( A C )( B C D)( A B D) ABC (4) F4 ( A B )( A C )( B C )(C D) (5) F5 AB C CD BD C 解:题中各函数对偶函数的最简与或式如下: (1) F1 A BC AB C (2) F2 A B D A C D (3) F3 AC A BD (4) F4 A BC B C CD (5) F5 ABC D (6) F6 AB C D 【3-10】已知逻辑函数 F A B C , G=A⊙B⊙C,试用代数法证明: F G 。 解:

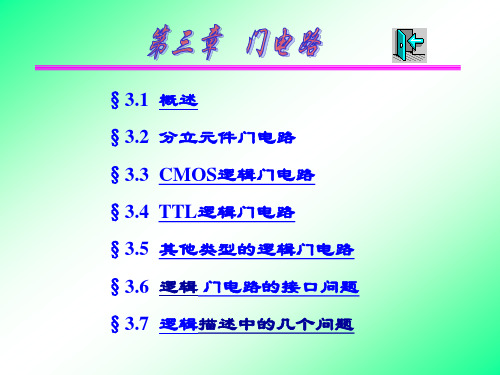

数字逻辑第3章 门电路

逻辑式:Y=A + B

逻辑符号: A 1

B

Y

电压关系表

uA uB uY

0V 0V 0V 0V 3V 2.3V 3V 0V 2.3V 3V 3V 2.3V

真值表

ABY

0

0

0

0

1

1

1

0

1

1

1

1

三、三极管非门

5V

利用二极管的压降为0.7V, 保证输入电压在1V以下时,

电路可靠地截止。

A(V) Y(V) <0.8 5 >2 0.2

II H &

II L &

… …

NOH

I OH (max) I IH

N MIN ( NOH , NOL )

NOL

IOL(max) I IL

六、CMOS漏极开路门(OD)门电路(Open Drain)

1 . 问题的提出

普通门电路

在工程实践中,往往需要将两个门的输出端 能否“线与”?

并联以实现“与”逻辑功能,称为“ 线与 。

输入 0 10% tr tf

tPHL

输出

tPLH

tr:上升时间

tf:下降时间 tw:脉冲宽度 tPHL:导通传输时间

tPLH:截止传输时间

平均传输延迟时间 (Propagation delay)

tpd= tpHL+ tpLH 2

5、功耗: 静态功耗:电路的输出没有状态转换时的功耗。 动态功耗:电路在输出发生状态转换时的功耗。

PMOS

NMOS

3、增强型MOSFET的开关特性

iD管可变子类型恒

VGS1 击开/关的条(件1)N沟道增强开型/M关O的S等FE效T电:路

计算机组成原理3-数字逻辑

04

数字逻辑在计算机中的应 用

计算机中的基本数字逻辑单元

01

逻辑门

逻辑门是构成数字逻辑电路的基本单元,如与门、或门、非门等。它们

按照一定的逻辑关系组合,实现各种复杂的逻辑功能。

02

触发器

触发器是计算机中常用的存储单元,它能够存储一位二进制信息,具有

记忆功能。常见的触发器有RS触发器、D触发器和JK触发器等。

03

编码器与译码器

编码器用于将输入的信号或数据转换为二进制代码,而译码器则将二进

制代码转换为对应的输出信号或数据。编码器和译码器在计算机中用于

数据传输和存储。

计算机中的存储器

寄存器

寄存器是计算机中用于存储数据 的临时存储单元,其特点是存取 速度快,但容量较小。寄存器常 用于CPU内部的数据传输和运算。

THANKS

感谢观看

输出Y仅在所有输入A、B都为高 电平时为高电平。

OR门

输出Y在任一输入A、B为高电平 时为高电平。

NOT门

输出Y与输入A的电平相反。

XOR门

输出Y在输入A、B不同电平时为 高电平,相同时为低电平。

NOR门

输出Y在所有输入A、B都为低电 平时为低电平。

NAND门

输出Y在任一输入A、B为高电平 时为低电平。

05

数字逻辑的发展趋势与展 望

可编程逻辑器件的发展

现场可编程门阵列(FPGA)

FPGA是一种可由用户配置的集成电路,通过编程实现各种数字逻辑功能。随 着技术的进步,FPGA的规模和性能不断提升,应用范围越来越广泛。

专用集成电路(ASIC)

ASIC是一种定制的集成电路,针对特定应用进行优化设计。随着工艺技术的进 步,ASIC的集成度和性能得到大幅提升,同时降低了功耗和成本。

数字逻辑第三章(2014)

.0 1 1 1 1

1 10 01

F

F1=A

F2=BC

以上分析可知: (1) 阻塞圈可大可小,小可以到某个最小项,大可超过 头部因子的合并圈; (2) 为保证尾因子的“非”内不再有非,阻塞圈也应包 含1重心; 大的阻塞圈可以使变量少,但究竟选大还是选小,应考虑此

阻塞圈(尾因子)的公用程度。

用阻塞法设计三级与非电路

• 如三级门设计中,输入全为原变量,就应当围 绕1重心来圈。

• 实际围绕1重心来圈时,有时将0方格也圈入, 所以要设法将圈入的0方格扣除,扣除的方法 是用被扣除的最小项的非之积来扣除,这就是 阻塞逻辑,因为在其相应输入组合下值为0, 禁止了积项输出“1”,使积项受控制。

阻塞的结果由两部分因子构成:一部分因子为原变量 形式,称为头部因子;另一部分因子为带“非”号形 式,称为尾因子。

F A B AB ( A B)( AgB)

AB AB ( A B)( A B)

该函数表达式简单,不用列真 值表,由表达式直接可以知 道电路的逻辑功能。这是一 个异或电路。

逻辑图

逐从

1

级输 写入

出到

输

出

逻辑表 达式

化 简

2

最简与或

表达式

组合逻辑电路的分析

A

& F1

__ __

__

= AD AD BC

3.3 组合逻辑电路的设计方法

• 组合电路的设计就是根据逻辑功能的要求,设计出实 现该功能的最优逻辑电路。

• 从采用的器件来看,

– 小规模集成电路(SSI) – 中规模集成电路(MSI) – 大规模集成电路(LSI)

追求的目标是最少门数 追求集成块数的减少

《数字逻辑》第3章作业与习题_单选题第六小题已更正版本

。

20.如果某 TTL 与非门的输入低电平噪声容限 VNL=0.7V,输入低电平

ViL=0.2V,那么它的关门电平 Voff 为

。

21.对于或非门,只要有一个输入为高电平,则输出就为 电平,所以

对或非门多余输入端的处理不能接 电平。

22.对于 TTL 与非门,只要有一个输入为低电平,则输出就为 电平,

为

,按抗干扰能力强弱的顺序依次为

,按静态功耗低和高的顺序依次为

。

6. 假设 VGS(TH)为开启电压,一般在 1~3V 范围内,则 NMOS 管当

时

截止,当

时导通;PMOS 管当

时截止,当

时

导通。

7. CMOS 反相器是由

作为驱动管,

作为负载管形成了 电

路结构。

2)单选题

1.硅二极管导通和截止的条件是( )。

不形成

;在外电场作用下,

和

均能参与导电。

7. 半导体中载流子的两种运动方式指

运动和

运动。

8. 硅二极管的截止条件是

,导通条件是

。

9. 数字电路中的晶体三极管作为开关元件,主要工作在

和

。

10. 三种基本逻辑门是

、

、

。

11. 与门是可以实现

的电路。

12. 在 TTL 电路中,输入端悬空等效于逻辑 电平,但为了避免引入干

② 输出端能带同类门的输入端个数

③ 输出端能带同类门的个数

④ 输入端数

7.输出端可直接连在一起实现“线与”逻辑功能的门电路是( )。

① 与非门

② 或非门 ③ OC 门

④ 异或门

8.两输入变量 A、B 的逻辑门的输出、输入如图所示,根据输出波形 Y,该

数字逻辑课件-第3章 组合逻辑电路

F

B F tpd tpd

3.3 组合电路中的竞争冒险

二、竞争现象与冒险的产生 A B C

& P2

1

& P1

&

F

A C B

B

H H

F A B BC A B BC

P2 P1 F

当A=C=1时 F B B 1 从理论上看:不论B为什么, 输出都为1

3.3 组合电路中的竞争冒险

制数的数值范围指示器,电路的 输入A、B、C、D是一位十进制数 的NBCD码,即X=8A+4B+2C+D, 要求当X≥5时,输出F=1,否则 F=0,该电路能实现四舍五入。 C

Z A BD BC A BD BC

A 1 d A 1 1 D d d D d 1 d 1 B d B C

Z

1 0 1 0 0 1 1 0 0 0 1 0 1 1 1 1

&

&

&

&

1

a

1

b

1

c

1

d

Z ab cd bc d a b d

ab c d进

制数的数值范围指示器,电路的 输入A、B、C、D是一位十进制数 的NBCD码,即X=8A+4B+2C+D, 要求当X≥5时,输出F=1,否则 F=0,该电路能实现四舍五入。 C

Z= RYG+RG+RY

5、用与非门构成逻辑电路 Z= RYG+ RG+ RY =RYG + RG + RY = RYG • RG

1 1

1

• RY

&

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

and NOR (与非和或非)

3

Digital Logic Design and Application (数字逻辑设计及应用)

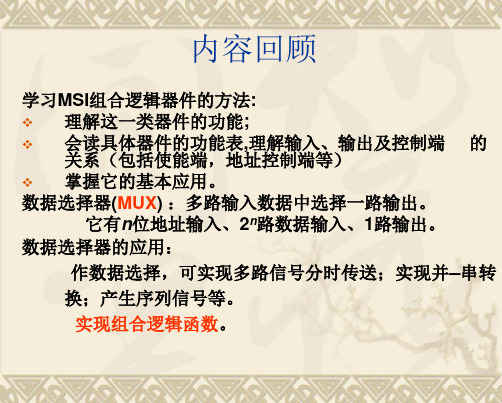

Review of Chapter 3 (第三章内容回顾)

Logic Families: TTL Family and CMOS Family (逻辑系列:TTL系列 和 CMOS系列) CMOS Logic Level (CMOS逻辑电平)

电压传输特性

Digital Logic Design and Application (数字逻辑设计及应用)

3.5 CMOS Steady-State Electrical Behavior (CMOS稳态电气特性)

Logic Levels Specifications (逻辑电平规格) VIHmin VILmax 0.3VCC LOW (低态) VOLmax 地+0.1V HIGH (高态) ABNOMAL (不正常状态) VOHmin VCC-0.1V

N-Channel (N沟道)

Drain (漏极) Gate (栅极 ) +

Vgs

Gate (栅极) +

Source (源极)

Drain (漏极)

Vgs

4

Source (源极)

P-Channel (P沟道)

Digital Logic Design and Application (数字逻辑设计及应用)

3.5 CMOS Steady-State Electrical Behavior (CMOS稳态电气特性)

Logic

Levels and Noise Margins ( 逻辑电平和噪声容限)

VOUT 5.0

Tp VOUT 1.5 3.5 5.0 VIN VIN Tn VDD = +5.0V

12

VDD = +5.0V

CMOS Inverter (CMOS反相器)

VCC

Z

A

Z

B

6

A

Digital Logic Design and Application (数字逻辑设计及应用)

Review of Chapter 3

CMOS NOR Gate (CMOS或非门)

VDD = +5.0V

CMOS Inverter (CMOS反相器)

VCC

A

B Z

Z

A

7

Digital Logic Design and Application (数字逻辑设计及应用)

Review of Chapter 3

Non-inverting Gate (非反相门)

VDD = +5.0V

CMOS Inverter (CMOS反相器)

VCC

Z

A A

Z

8

Digital Logic Design and Application (数字逻辑设计及应用)

0.7VCC

13

Digital Logic Design and Application (数字逻辑设计及应用)

Review of Chapter 3

The Additive “on” Resistance of series transistors limits the Fan – In of CMOS gates. (导通电阻的可加性限制了CMOS门的扇入数) VDD = +5.0V V = +5.0V

Digital Logic Design and Application (数字逻辑设计及应用)

Chapter 3 Digital Circuits (数字电路)

Give a knowledge of the Electrical aspects of Digital Circuits (介绍数字电路中的电气知识)

物理上的

而不是逻辑上的

DC

(直流噪声容限)

Fun-Out

10

(扇出)

Digital Logic Design and Application (数字逻辑设计及应用)

3.4 Electronic Behavior of CMOS Circuits (CMOS电路的电气特性)

Speed, Power Consumption (速度、功耗) Noise, Electrostatic Discharge (噪声、静电放电)

Review of Chapter 3

CMOS Inverter (CMOS反相器)

VDD = +5.0V

VCC

Tp

VOUT VIN Tn A Z

5

Digital Logic Design and Application (数字逻辑设计及应用)

Review of Chapter 3

CMOS NAND Gate (CMOS与非门)

DD

A B Z Z

A

B

9

Digital Logic Design and Application (数字逻辑设计及应用)

3.4 Electronic Behavior of CMOS Circuits (CMOS电路的电气特性)

Logic

Voltage Levels (逻辑电压电平) Noise Margins

Data Sheet (数据表) Specifications (规格说明) (Table 3-3 P99)

11

Open-Drain Outputs, Three State Outputs (漏 极开路输出、三态输出)

Digital Logic Design and Application (数字逻辑设计及应用)

1

Digital Logic Design and Application (数字逻辑设计及应用)

Review of Chapter来自3 PositiveLogic and Negative Logic

Vcc R VOUT VIN

(正逻辑和负逻辑)

Three

basic logic functions: AND, OR, and NOT

2

(三种基本逻辑:与、 或、非)

获得高、低电平的基本原理

Digital Logic Design and Application (数字逻辑设计及应用)

Review of Chapter 3 (第三章内容回顾)

Three

kinds of Description Method

(三种描述方法): Truth Table (真值表) Logic Expression (逻辑表达式) Logic Circuit (逻辑符号)