奇偶校验发生器

什么是奇偶校验,奇偶校验的方法

什么是奇偶校验,奇偶校验的方法

单向奇偶校验(Row Parity)由于一次只采用单个校验位,因此又称为单个位奇偶校验(Single Bit Parity)。

发送器在数据祯每个字符的信号位后添一个奇偶校验位,接收器对该奇偶校验位进行检查。

典型的例子是面向ASCII码的数据信号祯的传输,由于ASCII码是七位码,因此用第八个位码作为奇偶校验位。

单向奇偶校验又分为奇校验(Odd Parity)和偶校验(Even Parity),发送器通过校验位对所传输信号值的校验方法如下:奇校验保证所传输每个字符的8个位中1的总数为奇数;偶校验则保证每个字符的8个位中1的总数为偶数。

显然,如果被传输字符的7个信号位中同时有奇数个(例如1、3、

5、7)位出现错误,均可以被检测出来;但如果同时有偶数个(例如2、4、

6)位出现错误,单向奇偶校验是检查不出来的。

一般在同步传输方式中常采用奇校验,而在异步传输方式中常采用偶校验。

奇校验:就是让原有数据序列中(包括你要加上的一位)1的个数为奇数

1000110(0)你必须添0这样原来有3个1已经是奇数了所以你添上0之后1的个数还是奇数个。

偶校验:就是让原有数据序列中(包括你要加上的一位)1的个数为偶数

1000110(1)你就必须加1了这样原来有3个1要想1的个数为偶数就只能添1了。

02-17.2 奇偶校验器-课件

◆ 当n=9时,实现的即9位奇性奇偶校验电路。

《数字电子技术基础》

第十七讲 若干常用中规模组合逻辑电路-数值比较器和奇偶校验器

图1 9位奇性奇偶检验的数据传送示意图 《数字电子技术基础》

第十七讲 若干常用中规模组合逻辑电路-数值比较器和奇偶校验器

《数字电子技术基础》

第十七讲 若干常用中规模组合逻辑电路-数值比较器和奇偶校验器

※ 奇偶校验器 ※

Lecture

《数字电子技术基础》

第十七讲 若干常用中规模组合逻辑电路-数值比较器和奇偶校验器

█ 奇偶校验器

奇偶校验码是一种最常用的误差检验码。它的 编码方法是在信息码组外增加一位监督码元,增加 监督码元后,使得整个码组中“1”码元的数目为 奇数或为偶数。若为奇数,称为奇校验码(Odd parity);若为偶数,称为偶校验码(Even parity)。 实现奇偶校验的相关电路称为奇偶校验器。

图2 9位奇性奇偶检验异或门设计电路图 (a)串联型 (b)树型 《数字电子技术基础》

第十七讲 若干常用中规模组合逻辑电路-数值比较器和奇偶校验器

█ 奇偶校验 器的级联扩展

常用的9 位奇偶校验 器集成电路 有74LS280和 74180,若输 入多于9位, 可对其进行 级联扩展。 图示如下:

图3 多位奇偶检验器 (a)25位奇性校验 (b)81位奇性校验

实现奇校验的检验电路称为奇性奇偶校验器, 实现偶校验的检验电路称为偶性ห้องสมุดไป่ตู้偶校验器。

《数字电子技术基础》

第十七讲 若干常用中规模组合逻辑电路-数值比较器和奇偶校验器

█ 奇性奇偶校验器的门级电路设计

◆ 利用异或门可进行奇偶校验。 ◆ 因为异或门能实现“模2和”运算,即它能成对

奇偶校验器的原理

奇偶校验器的原理

奇偶校验器是一种错误检测机制,用于确认数据传输的准确性。

其原理是通过在传输数据中添加一个奇偶位,使得数据的总位数为奇数或偶数。

当数据接收端收到数据后,它会重新计算奇偶位,并与接收到的奇偶位进行比较。

如果两者一致,则数据传输正确无误;如果不一致,则说明数据传输过程中发生了错误。

具体原理如下:

1. 奇偶校验器在发送端将要传输的数据进行编码,将每个字符对应的二进制码与一个奇偶位相连。

奇偶位可以是“1”或“0”,使得整个字符的二进制码中的1的个数要么为奇数,要么为偶数。

2. 在接收端,奇偶校验器接收到数据之后,会重新计算接收到的每个字符的奇偶位,并与接收到的奇偶位进行对比。

3. 如果计算得出的奇偶位与接收到的奇偶位一致,说明数据传输正确。

4. 如果计算得出的奇偶位与接收到的奇偶位不一致,说明数据传输过程中发生了错误。

通过奇偶校验器的原理,可以在数据传输过程中检测出单比特错误(即数据中的某一位由于传输错误而发生了变化)。

但是奇偶校验器并不能检测出多比特错误(即数据中的多个位由于传输错误而发生了变化)。

因此,在实际应用中,通常会采用更强大的错误检测机制,如CRC(循环冗余校验)或哈密顿码。

位的奇偶校验器设计

16位的奇偶校验器设计课程设计报告学生姓名学号班级电子信息工程院系信院电子系题目16位的奇偶校验器设计指导教师2012 年 5 月题目一:设计一个16位的奇偶校验器,并仿真验证其功能。

(1班1组)(要求:输入一个16位的矢量数值,统计矢量中“1”的个数;并判断16位数中1的个数的奇偶性)1、设计思路2、VHDL程序(或原理图)3、仿真波形(图片)4、程序分析1,设计思路如下:可以使用FOR_LOOP语句,语法格式如下:[LOOP标号: ] FOR 循环变量,IN 循环次数范围LOOP顺序语句END LOOP [LOOP标号];FOR后的“循环变量”是一个临时变量,属LOOP语句的局部变量,不必事先定义。

“循环次数范围”规定LOOP语句中的顺序语句被执行的次数。

循环变量从循环次数数范围的初值开始,每执行完一次顺序语句后递增1,直至达到循环次数范围指定的最大值。

其中定义输入端口十六位的数据总线为a, 输出端口y将其奇偶校验的结果输出, 输出端c统计1 的个数2,VHDL程序如下:LIBRARY IEEE;USE ENTITY parity_check ISPORT (a:IN STD_LOGIC_VECTOR (15 DOWNTO 0); y:OUT STD_LOGIC;c:out integer range 0 to 16);END parity_check;ARCHITECTURE arch OF parity_check ISBEGINPROCESS(a)V ARIABLE temp:STD_LOGIC;V ARIABLE m: INTEGER RANGE 0 TO 16; BEGINtemp:='0';m:=0; --偶校验初始值设为0,奇校验初始值设为1 FOR i IN 0 TO 15 LOOP temp:=temp XOR a(i);IF (a(i)='1') THEN m:=m+1;END IF;END LOOP;y<=temp;c<=m;END PROCESS;END arch;原理图如下:3,仿真波形如下:程序分析实体:实体名parity_check输入端口十六位的数据总线a:IN STD_LOGIC_VECTOR (15 DOWNTO 0) 输出端口y:OUT STD_LOGIC;将其奇偶校验的结果输出若为奇数个1 输出为高电平;若为偶数个1输出为低电平输出端c:out integer range 0 to 16)统计1 的个数结构体:结构体名arch在进程PROCESS(a)中定义变量V ARIABLE temp:STD_LOGIC;V ARIABLE m: INTEGER RANGE 0 TO 16; 并进行变量的赋值temp:='0';m:=0;loop循环FOR i IN 0 TO 15 LOOPtemp:=temp XOR a(i);IF (a(i)='1') THEN m:=m+1;END IF;END LOOP;Temp与a(i)异或将其结果赋给tempIf语句若a(i)为1 m加1计数将其m的计数结果赋给c c 即为a中1 的个数相关文档:••••••••••更多相关文档请访问:。

实验五 奇偶校验器的设计

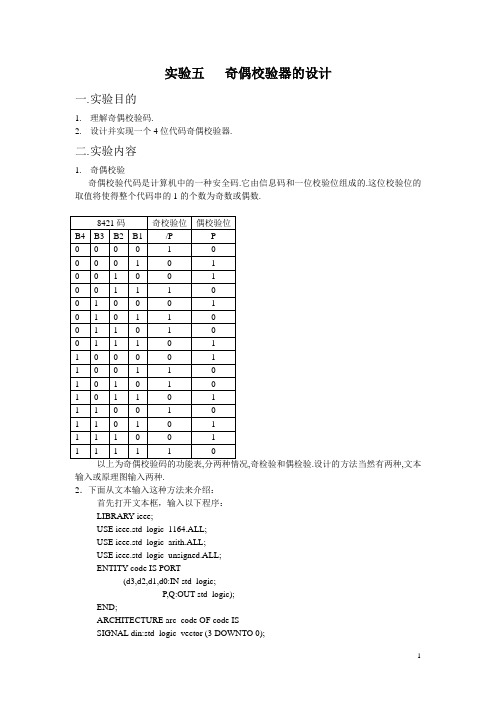

实验五奇偶校验器的设计一.实验目的1.理解奇偶校验码.2.设计并实现一个4位代码奇偶校验器.二.实验内容1.奇偶校验奇偶校验代码是计算机中的一种安全码.它由信息码和一位校验位组成的.这位校验位的取值将使得整个代码串的1的个数为奇数或偶数.以上为奇偶校验码的功能表,分两种情况,奇检验和偶检验.设计的方法当然有两种,文本输入或原理图输入两种.2.下面从文本输入这种方法来介绍:首先打开文本框,输入以下程序:LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_arith.ALL;USE ieee.std_logic_unsigned.ALL;ENTITY code IS PORT(d3,d2,d1,d0:IN std_logic;P,Q:OUT std_logic);END;ARCHITECTURE arc_code OF code ISSIGNAL din:std_logic_vector (3 DOWNTO 0);SIGNAL dout:std_logic_vector (1 DOWNTO 0);BEGINdin<=d3&d2&d1&d0;PROCESS (din)BEGINCASE din ISWHEN"0000"=>dout<="10";WHEN"0001"=>dout<="01";WHEN"0010"=>dout<="01";WHEN"0011"=>dout<="10";WHEN"0100"=>dout<="01";WHEN"0101"=>dout<="10";WHEN"0110"=>dout<="10";WHEN"0111"=>dout<="01";WHEN"1000"=>dout<="01";WHEN"1001"=>dout<="10";WHEN"1010"=>dout<="10";WHEN"1011"=>dout<="01";WHEN"1100"=>dout<="10";WHEN"1101"=>dout<="01";WHEN"1110"=>dout<="01";WHEN others=>dout<="10";END CASE;END PROCESS;P<=dout(1);Q<=dout(0);END arc_code;3.打开波形图输入,并导入图形三、心得体会:经过此次实验,体会到文本输入方式在某种程序上比原理输入方法会简单易操作,进一步熟悉MAXPLUS的操作。

用VHDL设计奇偶校验器

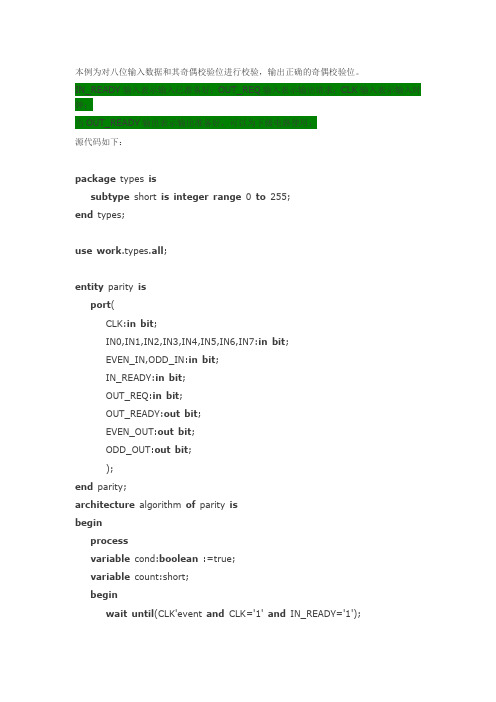

本例为对八位输入数据和其奇偶校验位进行校验,输出正确的奇偶校验位。

IN_READY输入表示输入已准备好;OUT_REQ输入表示输出请求;CLK输入表示输入时钟;当OUT_READY输出表示输出准备好,可以为下级电路使用;源代码如下:package types issubtype short is integer range0 to255;end types;use work.types.all;entity parity isport(CLK:in bit;IN0,IN1,IN2,IN3,IN4,IN5,IN6,IN7:in bit;EVEN_IN,ODD_IN:in bit;IN_READY:in bit;OUT_REQ:in bit;OUT_READY:out bit;EVEN_OUT:out bit;ODD_OUT:out bit;);end parity;architecture algorithm of parity isbeginprocessvariable cond:boolean:=true;variable count:short;beginwait until(CLK'event and CLK='1' and IN_READY='1');if(EVEN_IN=ODD_IN) then --奇偶校验预判断cond:=false;end if;count:=0;if IN0='1' thencount:=count+1;end if;if IN1='1' thencount:=count+1;end if;if IN2='1' thencount:=count+1;end if;if IN3='1' thencount:=count+1;end if;if IN4='1' thencount:=count+1;end if;if IN5='1' thencount:=count+1;end if;if IN6='1' thencount:=count+1;end if;if IN7='1' thencount:=count+1;end if;--判断输入数据中1的个数的奇偶while count>1 loopcount:=count-2;end loop;--判断奇偶校验位的正确性if count=1 and ODD_IN='0' thencond:=false;end if;if count=0 and EVEN_IN='0' thencond:=false;end if;--输出奇偶校验位if count=1 thenEVEN_OUT<='0';ODD_OUT<='1';elseEVEN_OUT<='1';ODD_OUT<='0';end if;--同步控制,设置输出控制信息wait until CLK'event and CLK='1' and OUT_REQ='1'; OUT_READY<='1';wait until CLK'event and CLK='1' and OUT_REQ='0'; OUT_READY<='0';--提示出错信息assert condreport"EVEN_IN ODD_IN error"severity warning;end process;end algorithm;。

74ls138设计奇偶校验器实验报告

74ls138设计奇偶校验器实验报告实验项目:数据的校验一、实验目的:1.了解数据的校验机制。

2.掌握海明码校验实施过程。

3.掌握循环冗余码校验实施过程。

二、实验要求:1.设计一个程序模拟奇偶校验实施过程(提示:主函数、发送函数、传输函数、校验函数)。

首先奇偶校验过程的基本过程:奇偶校验位有两种类型:偶校验位与奇校验位。

如果一组给定数据位中1的个数是奇数,那么偶校验位就置为1,从而使得总的1的个数是偶数。

如果给定一组数据位中1的个数是偶数,那么奇校验位就置为1,使得总的1的个数是奇数。

偶校验实际上是循环冗余校验的一个特例,通过多项式x+1得到1位cRc。

2.设计一个程序模拟海明码校验实施过程(提示:主函数、发送函数、传输函数、校验函数、纠错函数)。

3.设计一个程序模拟循环冗余码校验实施过程(提示主函数、发送函数、传输函数、校验函数、纠错函数)。

三、实验报告:1.给出源程序和执行结果。

#include#include#includeVoidproduct ();voidtrans();voidpop();intpl,p2;inta[8]={0};intmain()product()//产生一个随机的八位二进制的数trans()://设置传输出错一位或者没有出错的情况pop()//判断有无出错的情况return0;voidproduct();{inti,dataintcount1=0;srand((unsigned)time(0));data=0+rand()%128; //产生0-127的随机数printf("随机的产生一个128以内的十进制数为%d\n",data);for(i=0;i if(count1%2==0)//奇校验奇数个1校验位为0,偶数个1为la[7]=1;}for(i=0;i elsea[7]=0;pl=a[7];printf("初始二进制校验位放在最高位它printf("产生随机二进制数为");/*while(i>=0)printf("%d",a[--i]);*/for(i=7;i>=0;--i){printf("%d",a[i]);}printf("\n");}Voidtrans(){inti;srand((unsigned)time(0));i=0+rand()%9;//产生0-8的随机数if(i==0)printf("机器内部设置传输过程中没有出错\n");Else{a[i-1]=(a[i-1]==0)?1:0printf("传输过程将机器内部的数据进行了一位改动,改动位voidpop()printf("接收数据计算出的校验位为:%d\n",p2)if(p2!=a[7])printf("通过校验位p1与p2 的比较得出传输过程中数据出错了。

奇偶校验电路(Parity

n 位二进制代码

1位代码

奇偶校验位的取值原则: 采用奇校验时,使整个代码组中“1”的个数为奇数。 采用偶校验时,使整个代码组中“1”的个数为偶数。

四位二进制信息码 B3 B2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 B0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

agtb_out aeqb_out altb_out

比 较 结 果 输 出

A[3..0]

B[3..0]

A[7..4]

B[7..4]

也可通过修改Verilog HDL描述模型,完成设计。 当迭代级数增加时,引发电路响应速度问题。

四. 超前电路设计模型

在串行迭代比较电路中,从高到低逐位比较,其速度随位数增加而 降低。为了提高速度,减少级联信号通过的门的数量,可采用超前电 路,即每个模块不产生级联信号,只产生超前电路需要的中间信号,超 前电路对这些中间信号同时处理,产生输出结果。

4.5.6 比较器(Comparators) 比较器是对两个位数相同的二进制整数进行数值比 较,并判断其大小关系的逻辑电路。 ● 大小关系分为:大于(>) 等于(=) 小于(<) ●从高位开始比较,只有在高位相等情况下,才进 行低位比较。 ●通常采用便于级连扩展的迭代设计方法(模块设 计、重复电路)。

若约定为奇校验,一般采用偶校验电路产生发送 端的校验位,而用奇校验电路在接收端检验数据的正 确性; 若约定为偶校验,一般采用奇校验电路产生发送 端的校验位,而用偶校验电路在接收端检验数据的正 确性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

奇偶校验发生器/检测器

奇偶校验发生器/检测器是用来检查数据传输和存取过程中是否产生

错误的组合逻辑电路。

奇偶校验发生器/检测器是同一个逻辑器件:当作为奇偶校验发生器使用时,它可产生奇偶校验位,与数据一起传输或保存;

当作为奇偶校验检测器使用时,它可以检验所接受数据的正确性。

⑴奇偶校验发生器

①工作原理

被校验的数据和1位校验位组成校验码。

以 8421 码为例, 当采用奇校验时,被校验的数据和校验位满足奇数个 1 ,组成 5 位奇校验码

奇校验位逻辑值的表达式

当采用偶校验时,被校验的数据和校验位满足偶数个 1,组成 5 位偶校验码

偶校验位逻辑值的表达式

②电路实现

由以上两个表达式看出:

电路采用异或门实现,非常简单;

奇校验位逻辑值电路是在偶校验位逻辑值电路输出端加非门实现。

⑵奇偶校验检测器

①工作原理

校验码被送到检测电路,该电路能够检测奇偶错。

工作原理是校验码送到检测电路,发生一位错或奇数位错时,输出为 1,否则为 0.

②电路实现

和发生器电路相同,只不过增加了 1 个输入端。

实际应用中,发生器电路和检测器电路是同一电路,作在一个 IC 片上。

逻辑表达式

Jqi 是奇检测输出当 Jqi = 0 时,校验码无错,允许输出;

当Jqi=1时,校验码有错,禁止输出。

逻辑表达式

Jou 是偶检测输出当Jou = 0 时,校验码无错,允许输出;

当Jou = 1 时,校验码有错,禁止输出。

⑶奇偶校验实际应用意义

①能够检测一位错或奇数位错,但不能确定错误位置,因此,不能纠错;

②由逻辑表达式看出,电路不能检测偶数位错,当发生偶数位错时,电路显示正确;

③数据在存储或传送过程中,发生一位错误的可能性占96%以上;

④电路简单,容易实现,且有实际应用意义。