用于高速总线的信号完整性测试

信号完整性常用的三种测试方法

信号完整性常用的三种测试方法信号完整性是指在传输过程中信号能够保持原始形态和准确性的程度。

在现代高速通信和数字系统中,信号完整性测试是非常重要的工作,它能够帮助工程师评估信号的稳定性、确定系统的极限速率并发现信号失真的原因。

下面将介绍三种常用的信号完整性测试方法。

一、时域方法时域方法是信号完整性测试中最常见和最直观的方法之一、它通过观察信号在时间轴上的波形变化来评估信号的完整性。

时域方法可以检测和分析许多类型的信号失真,如峰值抖动、时钟漂移、时钟分布、幅度失真等。

时域方法的测试设备通常包括示波器和时域反射仪。

示波器可以显示信号的波形和振幅,通过观察波形的形状和幅度变化来判断信号完整性。

时域反射仪可以测量信号在传输线上的反射程度,从而评估传输线的特性阻抗和匹配度。

二、频域方法频域方法是另一种常用的信号完整性测试方法。

它通过将信号转换为频域表示,分析信号的频谱分布和频率响应来评估信号完整性。

频域方法可以检测和分析信号的频谱泄漏、频谱扩展、频率失真等。

频域方法的测试设备通常包括频谱分析仪和网络分析仪。

频谱分析仪可以显示信号的频谱图和功率谱密度,通过观察频谱的形状和峰值来评估信号完整性。

网络分析仪可以测量信号在不同频率下的响应和传输损耗,从而评估传输线的频率响应和衰减特性。

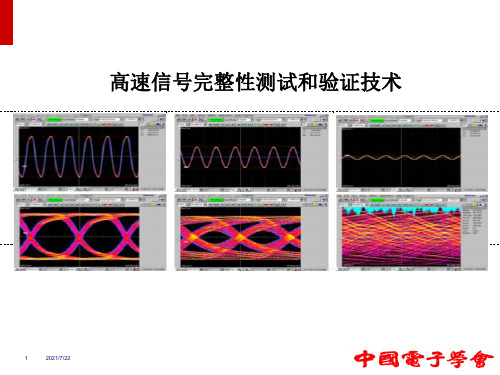

三、眼图方法眼图方法是一种特殊的信号完整性测试方法,它通过综合时域和频域信息来评估信号的完整性。

眼图是一种二维显示,用于观察信号在传输过程中的失真情况。

眼图可以提供信号的时钟抖动、峰值抖动、眼宽、眼深、眼高等指标。

眼图方法的测试设备通常包括高速数字示波器和信号发生器。

高速数字示波器可以捕捉信号的多个周期,并将其叠加在一起形成眼图。

通过观察眼图的形状和特征,工程师可以评估信号的稳定性和传输质量。

总结起来,时域方法、频域方法和眼图方法是常用的信号完整性测试方法。

它们各自具有独特的优势和适用范围,可以互相协作来全面评估信号的完整性。

在实际应用中,根据具体需求和测试对象的特点,选择合适的测试方法是非常重要的。

SPI总线信号品质与完整性检测技术与标准

SPI总线信号品质与完整性检测技术与标准1. 简介SPI(Serial Peripheral Interface)总线是一种同步串行通信接口,常用于连接微控制器和外设设备。

为确保SPI总线的正常工作,需要对信号品质和完整性进行检测。

本文档将介绍SPI总线信号品质与完整性检测技术与标准。

2. SPI总线信号品质检测技术2.1 基本参数检测在进行SPI总线信号品质检测时,需要关注以下几个基本参数:- 时钟频率:检测SPI总线的时钟频率是否符合规范要求。

- 数据传输速率:检测SPI总线的数据传输速率是否达到设定目标。

- 噪声干扰:检测SPI总线信号是否受到外部噪声和干扰的影响。

- 电压波动:检测SPI总线信号的电压波动情况,确保在合理范围内。

2.2 眼图分析眼图分析是一种常用的SPI总线信号品质检测方法。

通过使用示波器捕获SPI总线信号,并在屏幕上显示眼图,可以直观地评估信号的质量。

眼图分析可以检测以下问题:- 时钟抖动:检测时钟信号的抖动情况。

- 眼图闭合度:评估数据信号的稳定性和抗干扰能力。

- 眼图畸变:检测信号波形的畸变情况。

2.3 串扰分析串扰是指在SPI总线中,信号线之间相互干扰所引起的问题。

对于高速SPI总线,串扰问题尤为重要。

进行串扰分析时,需要考虑以下几个方面:- 电磁干扰:检测信号线之间的电磁干扰情况。

- 电源干扰:检测信号线受到电源干扰的影响程度。

- 地线干扰:评估信号线之间的地线干扰情况。

3. SPI总线信号完整性检测技术3.1 时序分析时序分析是一种常用的SPI总线信号完整性检测方法。

通过对SPI总线信号进行时序分析,可以评估信号传输的准确性和稳定性。

时序分析可以检测以下问题:- 时钟偏移:检测时钟信号的偏移情况。

- 数据丢失:检测数据传输过程中是否有数据丢失的情况。

- 时序违规:评估信号传输是否符合时序规范要求。

3.2 噪声分析噪声分析是一种用于检测SPI总线信号完整性的重要方法。

高速数字电路设计中的信号完整性分析

高速数字电路设计中的信号完整性分析在高速数字电路设计中,信号完整性分析是非常重要的一环。

信号完整性分析旨在确保信号在电路中能够准确、稳定地传输,从而避免信号失真或干扰,保证电路的性能和可靠性。

首先,我们需要了解信号完整性分析的基本概念。

信号完整性是指在一个电路中,信号从发送端到接收端能够保持原有的形态和正确的数值。

在高速数字电路设计中,信号往往受到许多因素的影响,如传输线特性、阻抗、反射、串扰等,这些因素都有可能导致信号失真。

因此,对信号完整性的分析和优化至关重要。

在进行信号完整性分析时,我们需要首先考虑传输线的特性。

传输线的特性包括传输速度、阻抗匹配、传输延迟等,这些特性直接影响信号传输的稳定性和速度。

通过对传输线的建模和仿真分析,可以帮助我们了解传输线对信号的影响,从而优化电路设计。

另外,阻抗匹配也是信号完整性分析中的重要内容。

当信号源和负载的阻抗不匹配时,会导致信号的反射和衰减,从而降低信号的质量和稳定性。

因此,在设计电路时,需要确保信号源和负载的阻抗能够有效匹配,以减少信号的失真和干扰。

此外,信号完整性分析还需要考虑信号的传输延迟和时序关系。

在高速数字电路中,信号传输的延迟会对数据的同步和稳定性产生影响。

通过时序分析和延迟优化,可以更好地控制信号的传输速度和有效减少时序误差。

最后,在进行信号完整性分析时,还需要考虑信号的功耗和信噪比。

功耗会影响电路的工作效率和稳定性,信噪比则会影响信号和噪声的比值,从而影响信号的准确性和清晰度。

因此,在设计电路时,需要综合考虑功耗和信噪比等因素,以实现信号的高质量传输。

总的来说,信号完整性分析是保证高速数字电路性能和可靠性的重要步骤。

通过对传输线特性、阻抗匹配、传输延迟、功耗和信噪比等方面的分析和优化,可以更好地保证信号在电路中的准确传输,避免信号失真和干扰,从而提高电路的性能和可靠性。

希望以上内容对您有所帮助。

集成电路测试中的高速串行接口测试方法

集成电路测试中的高速串行接口测试方法高速串行接口测试方法在集成电路测试中起到非常重要的作用。

高速串行接口是现代集成电路中广泛使用的一种通信方式,其在数据传输速率和通信距离方面具有明显优势,适用于高速数据传输和远距离通信。

为确保高速串行接口的稳定性和可靠性,需要对其进行全面的测试。

以下将介绍几种常用的高速串行接口测试方法。

一、物理层测试方法物理层测试主要是对高速串行接口的物理连接进行测试。

该测试方法主要包括以下几个方面的内容:1. 信号完整性测试:通过检测信号的波形和电平,确保信号在传输过程中没有发生失真和干扰。

常用的测试手段包括时钟和数据眼图测试、时钟抖动和噪声测试等。

2. 差分信号测试:对差分信号的幅度、延迟和相位进行测试,以保证差分信号的正常传输。

常用的测试方法包括查找表测试、时序测量和匹配测试等。

3. 传输线测试:通过对传输线的阻抗匹配、衰减和时延进行测试,确保传输线的质量和传输速率。

常用的测试手段包括衰减测试、传输线模型测试和传输线延时测试等。

二、协议层测试方法协议层测试主要是对高速串行接口的通信协议进行测试。

该测试方法主要包括以下几个方面的内容:1. 通信协议测试:对通信协议的正确性和稳定性进行测试,以保证数据能够正确地传输和解析。

常用的测试手段包括数据包验证、错误恢复和流控制测试等。

2. 时序调整测试:对时钟的校准和时序的调整进行测试,以确保时序的准确性和稳定性。

常用的测试方法包括时钟同步测试、时序校准和时序复位测试等。

3. 错误检测与纠正测试:对错误检测和纠正机制进行测试,以保证数据的可靠性和完整性。

常用的测试手段包括CRC校验测试、差错码测试和纠错算法测试等。

三、性能测试方法性能测试主要是对高速串行接口的数据传输性能进行测试。

该测试方法主要包括以下几个方面的内容:1. 传输速率测试:对传输速率进行测试,以确保高速串行接口能够达到设计要求的数据传输速率。

常用的测试手段包括比特错误率测试、吞吐量测试和带宽测试等。

信号完整性测试

5

2021/7/22

测试能帮我们做些什么?

▪ 验证

–验证我们的硬件设计是否符合设计要求 –验证我们的信号质量是否达到设计要求:波形,时序,电源 –验证仿真结果和实测结果的一致性:波形,时序,电源 –验证模型的准确性

▪ 调试

–调试的目的:发现问题,解决问题 –问题是否是硬件设计的问题? –问题是否是器件的原因:驱动能力?模型? –问题是否是布局布线的问题:拓扑?端接?阻抗?走线长度?串扰?

▪ 高速电路常见测试问题和调试技巧

▪ 衡量高速信号质量的重要手段和方法:眼图和抖动测试与分析

▪ 高速互连的阻抗测试与分析

3

2021/7/22

客户调查:您需要哪一项测试?

System test

(functional check; debug)

2

1

Test points

Tx output

Tx + -

Tx + Interconnect

▪ 测试仪器的关键指标

–探头影响 –带宽和上升时间 –采样模式 –时钟恢复 –时间精度

38

2021/7/22

探头如何影响测量测量系统

VCC

CC VIN

RC 探头及仪表

RP

CP

RE

DUT

NOTE: VCC 为交流对地

没有探头及仪表

有探头及仪表

Gain = - RC RE

f0 = 1 2 RCCC

Gain = - (RC||RP) RE 1

9

2021/7/22

波形测试——模板测试

10

2021/7/22

时序测试

▪ 时序测试的内容:

RapidIO高速串行总线的信号完整性测试

Ke r s h hsedsr l u ;i a i eryt tjt et m;y a em; I ywod :i pe e a b ss n ln gi s;t rs c u eept r I g i g t t e ie p r t S

pt r , t —smblnefr c (S) er nrle .T et t euts ie o bn t nwt a a e i e y o itr e e II ,r r o t ,t h s rsli g ni cm ia o i R ・ t n nr en oc o c e v n i h

p l i edsr l u yt p l ai ,n erlt p cf a o saea a sdb s gjt i O hg s e e a b sss m api t n a dt e e seic t n r n l e yu i t r d hp i e c o h ad i i y n ie

采 用 R pdO 串行 总 线 协议 的芯 片 、 板 和系 ail 背 统设 备 间传送 速 率高 达 3 15~6G i s信 号上 升 .2 bt , / 时 间低 于 0 1n , 号 完整 性 测 试 在 整个 系统 性 能 . s信

1 R pd0 高 速 串行 总 线 信 号完 整 性 测试 a il 的几个概念

A s a tT ekycne t fh h sed sr l u i a it ryt t sit d cdicu igjt ,y bt c :h e o cp i p e e a b ss n l ne i s i nr ue ldn ie ee r o g i g gt e o n tr

《高速串行总线信号完整性分析》范文

《高速串行总线信号完整性分析》篇一摘要:本文主要探讨高速串行总线中信号完整性的重要性、影响信号完整性的主要因素及其对系统性能的影响。

通过对信号完整性的深入分析,我们提出了有效的设计策略和改进措施,以提高信号完整性和系统的整体性能。

一、引言随着现代电子技术的发展,高速串行总线已成为数据传输的主要手段。

然而,在高速传输过程中,信号完整性成为一个关键问题。

信号完整性的好坏直接影响到系统的性能和可靠性。

因此,对高速串行总线信号完整性的分析具有重要的实际意义。

二、信号完整性的定义及重要性信号完整性是指信号在传输过程中保持其形状、幅度、时间和相位关系的能力。

在高速串行总线中,由于传输线效应、反射、电磁干扰等的影响,信号完整性可能受到损害,导致系统性能下降,甚至出现错误。

因此,保证信号完整性是提高系统性能和可靠性的关键。

三、影响信号完整性的主要因素1. 传输线效应:传输线效应是高速串行总线中影响信号完整性的主要因素之一。

由于传输线的特性阻抗与驱动器和接收器的阻抗不匹配,会导致反射、振荡等现象,从而影响信号的完整性。

2. 电磁干扰:电磁干扰是另一个影响信号完整性的重要因素。

外部电磁场和电流可能会对传输的信号产生干扰,导致信号失真或衰减。

3. 串扰:串扰是指不同传输线之间的耦合效应,它会导致信号的误读或畸变,从而影响信号的完整性。

四、信号完整性对系统性能的影响信号完整性的好坏直接影响到系统的性能和可靠性。

信号失真或衰减可能导致数据的误读或丢失,从而影响系统的正常工作。

此外,由于反射和振荡等现象,可能会增加系统的噪声和功耗,降低系统的稳定性和可靠性。

五、提高信号完整性的设计策略和改进措施1. 优化传输线设计:通过合理设计传输线的长度、阻抗等参数,以减小传输线效应对信号完整性的影响。

2. 电磁屏蔽:通过合理的电磁屏蔽设计,减小外部电磁场对传输的信号的干扰。

3. 串扰控制:通过优化布线、增加地线层等方式,减小不同传输线之间的耦合效应,从而控制串扰对信号完整性的影响。

高速并行总线信号完整性测试技术

射电磁能, 并随之产生串扰 。

6定时抖 动 : ) 当数字信 号在周期 间包含有微小

2 .高速数字系统 的信号完整性 问题

在高速数字系统中 ,典型的信号完整性问题包

的边沿位置变动时 , 就会产生抖动 。 这种抖动将影响

整个数位系统的定时准确性和同步 。

3 .定时 问题 引起信 号完整性故 障

维普资讯

数字信号畸变产生于许多根本性原 因,与定时 特别是对那些拥有大量总线 、输入和输 出装置的高

有关的问题是非常普遍 的现象。

速数字系统, 它具有高通道数 、 深存储器和先进的触

发功能 , 可从许多测试点捕获数字信息。 作为数据域 仪器 , 逻辑分析仪产生的定时图形清晰 、 易懂 , 并易 于与预期的数据进行 比较,从数据层上验证结果是

维普资讯

高逮并行息线位号竞奠性潮试技术

泰克科技 ( 中国) 有限公 司 张楷

摘要 : 随着信号速度的显著提 高, 信号完整性 问题 已经成为高速数字设计 中的关键 。本文介绍 了一种

新的信 号完整性分析技 术, 通过集成逻辑分析仪和数字存储示波器, 将物理层模拟信 号, 数据层数 字 信号时间相关的联合观测 , 自动测试多迭 48 0 个并行总线眼图, 效定位和分析 高速 总线 中出现的故 有 障问题 , 排除由于信号完整性 问题导致 的数字系统错误。最后结合处理器和 高速总线 , 出了高速信 给

3 1总线竞争 .

当两个驱动器设备试图同时使用同一总线时 ,

就产生了总线竞争现象 , 它会导致信号畸变。正常 否正确 。现代逻辑分析仪都包括能够帮助检测某些 例如毛刺触发 、 建 情况下 , 当一个驱动器传送数据时 , 另一个驱动器应 对信号完整性有影响的触发功能 , 这些触发条件, 以及许 进入高阻抗状态并保持 “ 让路” 态。但如果高阻 立和保持时间违规触发等等 , 状 抗 的设备不能及时切换 , 就会出现两个驱动器争用 多其他逻辑组合触发条件可同时应用于数百个通道

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

- >133 MHz clock,

Fr. Side Bus

- <250 ps rise time,

800

MB/s

-

Spread spectrum clocking, Logic levels: 3.3V, 1.0V

1.ห้องสมุดไป่ตู้ GB/s Hi-speed

AGP

Bus

Controller

RamBus

System Memory

用于高速总线的信号完整性测试

目录

• 市场的紧迫性 • 技术趋势 • 工业挑战 • 测试方面的挑战机解决方案

• 总结

市场的驱动力

技术趋势

– Digital Data Bandwidth: Pentium P4 - >1GHz, 400MHz bus, 3.2GB/s bus transfer rate (IDF August 2000)

Chip Set

- 800 MHz self-timed

driver IC,

data,

Legacy Buses

- Source-sync bus

- 800 mV pp RSL logic,

- up to 266 MHz data rate

Peripherals

- 200 ps setup/hold, - 200 ps rise times

Inter-chip bus

1.6 GB/s

AGP:

Rambus:

- 66 MHz Clock,

I/O Bus

- Differential 400 MHz

- Dynamic series Peripherals PCI Bus Controller USB Peripherals clock,

termination in the

多快才是足够快?

示波器上升时间

等于信号的上升时间 2 倍于信号的上升时间 3 倍于信号的上升时间 5 倍于信号的上升时间

上升时间慢/异常幅度衰 减

41% 12% 5% 2%

What you don’t know...

...can hurt you!

关于示波器边沿速度的建议

建议示波器的上升时间至少为被测信号上升时间 的3-5倍

示波器带宽指标

0.1

0.2

0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

100

97.5

95

92.5

90

BW

=

0.35* trise

87.5 85 82.5

80

77.5

75

72.5

70.7 (- 3 dB)

在 3dB 带宽频率,信号的垂直幅度误差大约为30%

关于示波器带宽的建议

建议示波器的带宽至少为被测信号频率的3-5倍

用具有 100ps 上升时间的示波器测试一个 300ps 上升时 间的信号会使失真降到最小限度

你曾经遇到过这样的测试挑战吗?

– 更快的时钟和数据速率 – 更快的上升/下降时间 – 更短的建立/保持时间 – 更加轻微的抖动指标 – 更小的逻辑摆动 – 阻抗及终端问题 – 同步总线结构 – 需要观察更多的信号 – 难于探测 – 难于连接

教科书上的数字化信号

逻辑信号 +5 V电源

地信号

1

1

1

0

FALL TIME

RISE TIME

CLOCK A

B

C

DATA

上升/下降时间 vs. 示波器带宽

上升时间(示波器) ~= 0.35/带宽(示波器)

2 GHz BW Oscilloscope has ~200ps Risetime 4 GHz BW Oscilloscope has ~100ps Risetime

– “The 21264 ...channels up to 5.3 Gbytes/s of cache data ...into the processor, feeding its demanding CPU core.”

(Digital/Compaq web site on Alpha 21264 RISC processor)

– “Peak Memory BW (2.13 GB/sec)” (IBM web site regarding

RS-6000 RISC processor)

– “The PCI (Peripheral Component Interconnect) bus provides data rates of one GByte per second and up”

用 2GHz 带宽示波器测试 100ps 上升时间

RT(measured) = SQRT[RT(oscilloscope)2 + RT(Signal)2] RT(measured) = SQRT[200ps2 + 100ps2] = 224ps!

用 4GHz带宽示波器测试 100ps 上升时间

RT(measured) = SQRT[RT(oscilloscope)2 + RT(Signal)2] RT(measured) = SQRT[100ps2 + 100ps2] = 140ps!

(Intel web site )

工业挑战: 更快的计算机结构

PCI: - >66 MHz

clock, - >66 MHz data - >266 MB/s

Secondary Cache

Graphics Accelerator

Back Side Bus

CPU

FSB (Front Side Bus):

0

0

真实的数字信号

?

逻辑信号 +5 V电源

地

更高的时钟和数据速率的挑战

– P4 >400MHz data bus – Rambus 800MHz – DDR 266MHz clock – Firewire 1394b 1.6Gb/s transfer rate – USB2 480 Mb/s data rate – Infiniband 2.5Gb/s – DVI 1 Gb/s data BW – Serial ATA 1.5Gb/s transfer rate

使用 2.4 GHz 的示波器测试一个800 MHz 正弦波信号使信 号的幅度失真降到最小限度

举例: Tektronix 4 GHz TDS7404, 3 GHz TDS694C

更快的边沿速度的挑战

– Rambus 200ps 上升/下降时间 – DDR <250ps – Firewire 1394b 80-300ps – USB2 <500ps