cadence upf 低功耗流程的仿真验证

Cadence综合技术提供新的方法来实现低功耗

Cadence综合技术提供新的方法来实现低功耗Cadence 设计系统公司今天发布了专为Cadence Encounter RTL Compiler 综合技术实现新的低功耗能力,可提升芯片质量(QoS)。

Encounter RTL Compiler 现在通过将多目标全局优化扩展到动态及泄漏功耗优化,以一种全新的方式实现了低功耗。

该单一过程解决方案改进了电源、时序和面积以求获得更高质量的芯片。

Encounter RTL Compiler 的整个低功耗综合解决方案在所有目标的同步优化上是独一无二的,带来了最快的芯片实现途径。

从事纳米规模设计的工程师们对功耗最为关注,并且功耗业已成为众多项目中最主要的优化对象。

在数字化实现流程中,大多数泄漏功耗优化是在RTL 到门级综合过程中实现的。

Encounter RTL Compiler 独一无二的、针对功耗、速度以及面积的单通路方法意味着更高的QoS 以及简化的设计流。

QoS 通过布线衡量一个设计的物理特性,主要包括改进的面积利用率、更高的性能以及更低的功耗。

不再需要在多次运行及多种工具中进行试验和错误纠正折衷。

“我们将在接下来的设计中使用Encounter RTL Compiler 的电源优化工具。

我们已经通过SoC Encounter 研究出一套基于Encounter RTL Compiler 的泄漏缩减方法,该方法能够帮我们实现高达600MHz 的目标速度,同时还能极大程度地减少泄漏功耗。

这绝对可以称得上是一举两得。

”SandbridgeTechnoloies公司的物理设计师Jeff Turlip 如是说。

Cadence 公司副总裁Chi-Ping Hsu 指出:“借助新低功耗方法,Encounter RTL Compiler 将继续改进其能力生产出质量最好的芯片,实现最快的运行时间和最高的容量。

我们很高兴能够提供全局综合技术以便在整个设计链中帮助我们的客户实现低功耗设计。

Cadence混合信号低功耗设计流程助力Silicon Labs降低MCU功耗

Cadence混合信号低功耗设计流程助力Silicon Labs降低

MCU功耗

佚名

【期刊名称】《单片机与嵌入式系统应用》

【年(卷),期】2013(13)11

【摘要】Cadence设计系统公司宣布,SiliconLabs采用完整的Cadence混合信号低功耗设计流程,使其最新款节能型基于ARM微控制器(MCU)的功耗大幅降低。

搭载了ARMCortex—M4核心的新款EFM32WonderGecko,功耗显著降低,即使运行在更高的温度,也能延长电池使用时间。

这款微控制器瞄准对功耗敏感的应用场合,例如智能能源和自动化领域,无论在活动还是在睡眠模式下均可实现低功耗运行。

【总页数】1页(P87-87)

【关键词】Cadence设计系统公司;低功耗运行;设计流程;混合信号;ARM微控制器;MCU;电池使用时间;睡眠模式

【正文语种】中文

【中图分类】TP368.1

【相关文献】

1.SMIC推出基于CPF的CADENCE低功耗数字参考流程SMIC加盟PFI;向在SMIC投产90纳米低功耗芯片的客户,提供新设计解决方案 [J],

2.Power Architecture助力IC设计突破障碍/MIPS授权国家IC设计深圳产业化

基地低功耗内核/凌讯科技90nm芯片采用Cadence低功耗解决方案 [J],

3.Silicon Labs低功耗无线MCU进军智能家居/智能仪表市场 [J], 韩霜

4.Silicon Labs针对物联网推出最低功耗和最小尺寸的无线MCU [J],

5.Cadence混合信号低功耗设计流程 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

一种低功耗系统芯片的实现流程

一种低功耗系统芯片的实现流程摘要:随着半导体工艺技术的进步,系统芯片的集成度越来越高,功耗成为重点考虑的因素之一,尤其用于便携式设备中。

本文描述了一种多电源、多电压低功耗系统芯片的实现流程。

该流程基于IEEE1801(UPF)标准,采用Synopsys和MentorGraphics公司的EDA 工具,方便地实现了RTL-GDSII的整个过程。

关键词:低功耗;可测性设计;多电源多电压;电源关断0 引言随着CMOS半导体工艺的进步,集成电路进入系统芯片(System on Chip,SoC)设计时代,极大地提高了集成度和时钟频率,导致芯片的功耗急剧增加。

功耗成为集成电路设计中除面积和时序之外的又一个重要因素,因此低功耗设计成为学术界和产业界关注的焦点。

低功耗技术的引入,给芯片的设计和实现提出了新的挑战。

这些挑战包括电压域的划分、EDA工具之间数据的交换和管理等。

本文基于IEEEl801标准Uni-fied Power Format(UPF),采用Synopsys和Mentor Graphics的EDA工具实现了包括可测性设计在内的“从RTL到GDSII”的完整低功耗流程设计。

本论文第1部分描述了低功耗技术和术语。

第2部分描述了本文设计的系统芯片的情况。

第3部分描述了整个设计的流程和采用的EDA工具。

第4部分为总结。

1 低功耗技术数字CMOS电路的功耗主要有三个来源,分别是开关功耗Pswitching、短路功耗Pshort-circuit和泄漏功耗Pleakage,分为动态功耗(Psw itching+Pshort-circuit)和静态功耗(Pleakage)两大类,如式(1)所示。

其中,α是开关活动因子,CL是有效电容,VDD是工作电压,fclk是时钟频率,ISC是平均短路电流,Ileak是平均漏电流。

目前提出了各种降低功耗的方法,主流的技术有门控时钟(Clock-Gating)、多阈值电压(Multi-threshold),先进的技术包括多电压(Mulit-Voltage,MV)电源关断(MTCMOS Pwr Gating)、多电压和带状态保持功能的电源关断(MV&Pwr Gating with State Retention)、低电压待机(Low-VDD Stan-dby)、动态或自适应电压和频率调整(Dynamic or Adaptive Voltage&Frequency Scaling,DVS、DVFS、AVS、AVFS)、阱偏置(Well Biasing,VTCMOS)等。

Cadence Incisive Enterprise Simulator将低功耗验证效率提升30%

Cadence Incisive Enterprise Simulator 将低功耗验证

效率提升30%

中国,2013 年5 月14 日,全球电子设计创新领先企业Cadence 设计系统公司(NASDAQ:CDNS),近日推出新版本Incisive Enterprise Simulator,该版本将复杂SoC 的低功耗验证效率提高了30%。

13.1 版的Cadence® Incisive® Enterprise Simulator 致力于解决低功耗验证的问题,包括高级建模、调试、功率格式支持,并且为当今最复杂的SoC 提供了

更快的验证方式。

Incisive SimVision Debugger 的最新调试功能对复杂的文本式功率意图标准提供了简单明了的交互式调试方式。

其他仿真器的改进包括额外的SystemVerilog 支持,更快的编译连接,使得仿真工作更快完成。

对CPF 的改良支持以及新增的IEEE 1801 支持将会让所有低功耗工程师都能享受到这些

改良成果。

我们成功地运行了Unified Power Format(IEEE 1801/UPF)仿真,用Incisive Enterprise Simulator 识别功耗域,确认隔离以及更多。

ST Microelectronics 研发设计经理David Vincenzoni 说。

该工具性能非常出色,我们对Cadence 表示喝彩,他们增加了全新的高级验证能力,以及IEEE

1801 支持,这将有助于加快低功耗SoC 的完成。

Cadence InciSive Enterprise SimuIator将低功耗验证效率提升30%

N a n o Y i e l d 高 良率解 决方 案

概伦 电子 科技 有限 公 司宣布 中芯 国际集 成 电路

视 频编码器 l P已可支持 V P 8技术

I m a g i n a t i o n T e c h n o l o g i e s日 前宣布 , 已在其领先

L I M b u s  ̄和 I 2 S 接 口,用 以为智能手 机和 更快完成。对 C P F的改良支持 以及新增的 I E E E 的同步 S

h t t p: / / www. c i c ma g . c o m

l 圆 圈

! 璺 箜 ! 垒 ! 塑 3

证的问题 , 包括高级建模 、 调试 、 功率格式支持 , 并且

为 当今最 复 杂的 S o C提供 了更快 的验 证 方式 。

全新高性价 比 H D音频 中枢

欧胜微电子有限公司 日 前宣布 :推 出产品代码

为 WM8 9 9 7的一 款 高度 灵 活 的 高 清 晰 度 音 频 中枢

I n c i s i v e S i m V i s i o n D e b u g g e r 的最新调试功能对

电子 )

应用提供高性能 、高品质的视频编码 / 解码解决方

案。 它 的出货 量 已超 过 5亿 , 遥 遥领 先于 业界 其他 方 案。P o w e r V R E 4 5 0 0 MP 视 频 编 码 器 是 I m a g i n —

进工艺制程开发中的 S R A M进行优化。 ( 来 自概伦 a t i o n V X E S e r i e s 4系列 产 品 的成 员 , 可 处 理所 有 主 要

功耗 验证 效率提 高 了 3 0 %。 1 3 . 1 版的 C a d e n c e  ̄

低功耗验证方法学

低功耗验证方法学

低功耗验证方法学是一个非常重要的领域,它涉及到在集成电路设计中如何有效地验证低功耗电路的正确性和可靠性。

在当今的电子产品中,低功耗设计已经成为一种趋势,因为它可以显著地降低能耗和延长电池寿命。

因此,低功耗验证方法学变得尤为重要。

在低功耗验证中,有几种常见的方法,包括仿真、形式化验证和硬件验证。

这些方法都有其优点和缺点,并且需要根据具体的需求进行选择。

仿真是一种通过模拟电路行为来验证其功能的方法。

在低功耗验证中,仿真可以帮助验证电路中低功耗模式的正确性,但是仿真速度较慢,需要大量的计算资源,而且在某些情况下可能无法覆盖所有可能的状态。

形式化验证是一种基于逻辑推理的方法,它可以通过数学方法来证明电路的正确性。

形式化验证可以帮助验证电路中低功耗模式的正确性,而且可以避免仿真中可能存在的遗漏问题,但是它需要对电路进行严格的建模和证明,因此可能需要大量的时间和资源。

硬件验证是一种基于实际物理硬件的验证方法,它可以直接验证电路的正确性。

在低功耗验证中,硬件验证可以帮助验证电路中低功耗模

式的正确性,并且可以提供更高的可靠性和准确性,但是需要更高的成本和时间。

总的来说,低功耗验证方法学是一个充满挑战和机遇的领域,需要持续地发展和创新,以满足不断变化的市场需求和技术要求。

CADENCE仿真步骤

CADENCE仿真步骤

Cadence是一款电路仿真软件,它可以帮助设计师创建、分析和仿真

电子电路。

本文将介绍Cadence仿真的步骤。

1.准备仿真结构:第一步是准备仿真结构。

我们需要编写表示电路的Verilog或VHDL代码,然后将它们编译到Cadence Integrated Circuit (IC) Design软件中。

这会生成许多文件,包括netlist和verilog等文件,这些文件将用于仿真。

2.定义仿真输入输出信号:接下来,我们需要定义仿真的输入信号和

输出信号。

输入信号可以是电压、电流、时间和其他可测量的变量。

我们

需要定义输入信号的模拟和数字值,以及输出信号的模拟和数字值。

3.定义参数:参数是仿真中用于定义仿真设计的变量,这些变量可以

是仿真中电路的物理参数,如电阻、电容、时延、输入电压等,也可以是

算法参数,如积分步长等。

4.运行仿真:在所有参数和信号都设置完成后,我们可以运行仿真。

在运行仿真之前,可以使用自动参数检查来检查参数是否正确。

然后,使

用“开始仿真”命令即可启动仿真进程。

5.结果分析:在仿真结束后,我们可以使用结果分析器来查看输出信

号的模拟和数字值,以及仿真中电路的其他特性,如暂态分析、稳态分析、功率分析等。

以上就是Cadence仿真步骤。

Cadence仿真流程

Cadence仿真流程Cadence 仿真流程第⼀章在Allegro 中准备好进⾏SI 仿真的PCB 板图1)在Cadence 中进⾏SI 分析可以通过⼏种⽅式得到结果:Allegro 的PCB 画板界⾯,通过处理可以直接得到结果,或者直接以*.brd 存盘。

使⽤SpecctreQuest 打开*.brd,进⾏必要设置,通过处理直接得到结果。

这实际与上述⽅式类似,只不过是两个独⽴的模块,真正的仿真软件是下⾯的SigXplore 程序。

直接打开SigXplore 建⽴拓扑进⾏仿真。

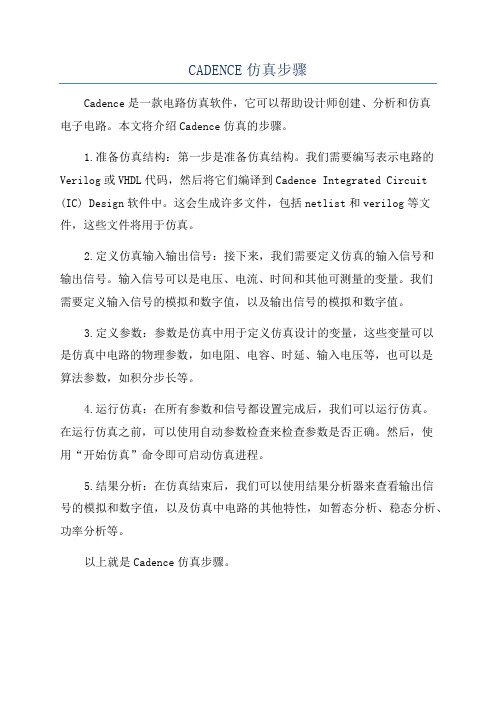

2)从PowerPCB 转换到Allegro 格式在PowerPCb 中对已经完成的PCB 板,作如下操作:在⽂件菜单,选择Export 操作,出现File Export 窗⼝,选择ASCII 格式*.asc ⽂件格式,并指定⽂件名称和路径(图1.1)。

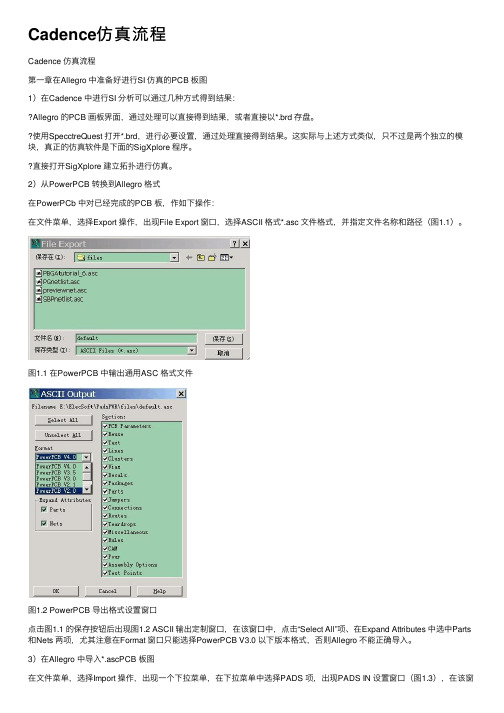

图1.1 在PowerPCB 中输出通⽤ASC 格式⽂件图1.2 PowerPCB 导出格式设置窗⼝点击图1.1 的保存按钮后出现图1.2 ASCII 输出定制窗⼝,在该窗⼝中,点击“Select All”项、在Expand Attributes 中选中Parts 和Nets 两项,尤其注意在Format 窗⼝只能选择PowerPCB V3.0 以下版本格式,否则Allegro 不能正确导⼊。

3)在Allegro 中导⼊*.ascPCB 板图在⽂件菜单,选择Import 操作,出现⼀个下拉菜单,在下拉菜单中选择PADS 项,出现PADS IN 设置窗⼝(图1.3),在该窗⼝中需要设置3 个必要参数:图1.3 转换阿三次⽂件参数设置窗⼝i. 在的⼀栏那填⼊源asc ⽂件的⽬录ii. 在第⼆栏指定转换必须的pads_in.ini ⽂件所在⽬录(也可将此⽂件拷⼊⼯作⽬录中,此例)iii. 指定转换后的⽂件存放⽬录然后运⾏“Run”,将在指定的⽬录中⽣成转换成功的.brd ⽂件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

cadenceupf低功耗流程的仿真验证

本文是记录项目过程中遇到的奇巧淫技,如有遗漏或者不足,请大家改正和补充,谢谢。

随着深亚微米技术的普及与发展,leakage功耗在整个功耗中的比重越来越大,比如45nm下,已

经占到了60%以上,所以低功耗解决方案应运而生。

目前已经有一套标准的低功耗设计流程,流

程有CPF(cadence主导)和UPF(synopsys主导)两种,但技术趋势是UPF会大一统,所以本篇

将为那些仍旧使用ncverilog而不是vcs仿真工具的苦逼们提供一些参考。

目前常用的降低低功耗的方法有四种:多电压域、时钟门控、电源关断和动态电压频率调整。

其

中的时钟门控对验证影响较小,大家应该都接触过,而剩下的三个对验证工作影响较大,需要用

到各个EDA厂商的低功耗解决方案。

闲话就说这么多,那么cadence如何使用upf来实现低功耗流程的仿真验证呢?

第一步,先得有UPF文件,根据设计需求,使用TCL建立脚本,建立和管理独立电压源、确定隔离、建立电平漂移等,一般是设计或者后端人员书写,验证工程师当然也可以写,具体内容参考IEEE 1801。

第二步,仿真case中添加电源上电过程,使用$supply_on函数给相应VDD上电。

第三步,将UPF嵌入到仿真命令中,即:

irun -lps_1801 sim.upf -lps_assign_ft_buf -lps_iso_verbose ...

或者

1 ncvlog ...

2 ncelab -lps_1801 sim.upf -lps_assign_ft_buf -lps_iso_verbose ...

3 ncsim ...

相关options解释如下:

①-lps_1801 filename: 指定符合IEEE 1801标准的UPF文件;

②-lps_assign_ft_buf: 指定assign赋值被当做buffer对待,而非默认的wire,好处是从always-on domain进入和穿过power-down domain的信号被force成x,便于debug;

③-lps_const_aon: 对处在power-down domain并且直接和always-on domain相连接的tie-high或

者tie-low constant,不使能corruption功能;默认不使用该功能;

④-lps_enum_rand_corrupt:对于用户定义的enum类型数据,在电源关断后,随机从枚举列表中

选择一个值作为变量值;和该命令相类似的还有-lps_enum_right, -lps_implicit_pso等,因为不常用,就不一一介绍了;

⑤-lps_iso_verbose: 使能isolation的log功能,这个一般需要加上;

⑥...

其它的options请参考cadence的low-power simulation guide。

最后,运行仿真即可。

最后说一下low power流程验证正确性和完备性的确认方法。

①增加的low power流程不能影响芯片本身功能的正确性,比如通过电源关断来降低芯片功耗,

则关断再打开后,芯片还可以正常work。

这部分可以利用原有的self-check验证环境来确认。

②利用log文件分析,上述仿真命令-lps_verbose和UPF文件会为仿真输出与low power相关的

warning, error以及assertion信息,通过log文件可以check流程的正确性;

③自动的assertion checker分析,使用-lps_verify选项可以自动检查电源关断顺序(隔离->复位->断电)和电源打开过程(上电->解复位->解隔离),如不满足该时序要求,会自动报错;

④利用覆盖率保证验证完备性,使用-lps_vplan选项依据UPF文件生成low power验证计划,通过simvision提供的coverage接口,得到low power相关的功能覆盖率;。