数字移相01

数字移相

一.两个同频信号之间的移相与实现方式所谓移相是指两路同频的信号,以其中的一路为参考,另一路相对于该参考作超前或滞后的移动,即称为是相位的移动。

两路信号的相位不同,便存在相位差,简称相差。

若我们将一个信号周期看作是3600,则相差的范围就在00∽3600之间。

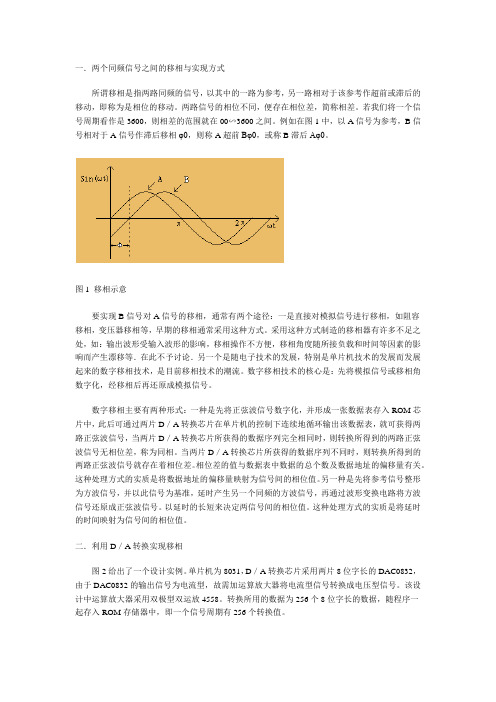

例如在图1中,以A信号为参考,B信号相对于A信号作滞后移相φ0,则称A超前Bφ0,或称B滞后Aφ0。

图1 移相示意要实现B信号对A信号的移相,通常有两个途径:一是直接对模拟信号进行移相,如阻容移相,变压器移相等,早期的移相通常采用这种方式。

采用这种方式制造的移相器有许多不足之处,如:输出波形受输入波形的影响,移相操作不方便,移相角度随所接负载和时间等因素的影响而产生漂移等.在此不予讨论.另一个是随电子技术的发展,特别是单片机技术的发展而发展起来的数字移相技术,是目前移相技术的潮流。

数字移相技术的核心是:先将模拟信号或移相角数字化,经移相后再还原成模拟信号。

数字移相主要有两种形式:一种是先将正弦波信号数字化,并形成一张数据表存入ROM芯片中,此后可通过两片D/A转换芯片在单片机的控制下连续地循环输出该数据表,就可获得两路正弦波信号,当两片D/A转换芯片所获得的数据序列完全相同时,则转换所得到的两路正弦波信号无相位差,称为同相。

当两片D/A转换芯片所获得的数据序列不同时,则转换所得到的两路正弦波信号就存在着相位差。

相位差的值与数据表中数据的总个数及数据地址的偏移量有关。

这种处理方式的实质是将数据地址的偏移量映射为信号间的相位值。

另一种是先将参考信号整形为方波信号,并以此信号为基准,延时产生另一个同频的方波信号,再通过波形变换电路将方波信号还原成正弦波信号。

以延时的长短来决定两信号间的相位值。

这种处理方式的实质是将延时的时间映射为信号间的相位值。

二.利用D/A转换实现移相图2给出了一个设计实例。

单片机为8031,D/A转换芯片采用两片8位字长的DAC0832,由于DAC0832的输出信号为电流型,故需加运算放大器将电流型信号转换成电压型信号。

二相PSK调制实验

二相PSK(DPSK)调制实验一、实验目的1.掌握二相PSK(DPSK)调制的工作原理及电路组成。

2.了解载频信号的产生方法。

3.掌握二相绝对码与相对码的码变换方法。

二、预习要求认真预习《通信原理》中关于PSK调制有关章节的内容。

三、实验仪器仪表(一)实验仪器仪表1.+5V、+12V、-12V三路稳压电源;一台2.二踪示波器;一台3.三用表;一台4.电子与通信原理实验系统实验箱一台(二)集成电路芯片介绍1.4066四双向模拟开关①典型参数:a、导通电阻Ron≤500Ωb、截止电阻Roff≥50MΩc、每路间偏差小于50Ω②外引线排列图③逻辑排列图2、LM318运算放大器外引线排列图3、LM311单比较器外引线排列图四、实验电路工作原理在本实验中,绝对移相键控(PSK)是采用直接调相法来实现,也就是用输入的基带信号直接控制已输入载波相位的变化来实现相位键控。

(一)电路组成图8-1是本实验系统二相PSK(DPSK)调制器电路框图。

图8-2是本实验系统二相PSK(DPSK)调制器电原理图。

(二)电路基本工作原理众所周知,数字相位调制又称为移相键控。

它是利用载波相位的变化来传递数字信息的。

通常又可把它分成绝对移相与相对移相两种方式。

本实验是采用绝对移相方式,所谓绝对移相就是利用载波不同相位的绝对值来传递信息。

那么,怎样才能让载波不同相位的绝对值来传递数字信息呢?如果让所需传输的数字基带信号控制载波相位改变,而载波的振幅和频率都不变,那么就得到载波的相位发生变化的已调信号,我们把这种调制方式称为数字相位调制。

即移相键控PSK调制。

PSK调制在数字通信系统中是一种极重要的调制方式,它的抗干扰噪声性能及通频带的利用率均优先于ASK移幅键控和FSK移频键控。

因此,PSK技术在中、高速数据传输中得到了十分广泛的应用。

本实验采用的是二相PSK调制,其它还有四相移键控(QPSK)、八相移相键控(8PSK)、正交部分响应(QPRS)、十六进制正交调幅(16QAM)等。

ASK&FSK&PSK

10

双比特码元与载波相位的关系

双比特码

00 10 11 01

π/2相移系统

0 π/2 π -π/2

π/4相移系统

-3π/4 - π/4 π/4 3π/4

多进制相对移相(MDPSK) 多进制相对移相和二进制相对移相原理相同,也 是利用码元之间的相对相位变化来表示数字信息。

n n

A cos[ 0t t ]

n

n

s (t ) cos ( 1t n ) s (t ) cos ( 2 t n )

= ) [ 0 ) 1t n ) s (tA cos(2 t nt ] 0 t t ]

1, 概率为P an 0, 概率为(1-P)

e2 PSK (t ) s(t ) cos ct

s 这里, (t ) 与2ASK及2FSK时不同,为双极性数字 基带信号,即 1, 概率为P an s(t ) an g (t nTS ) 1, 概率为(1-P) n

因此,在某一个码元持续时间 TS 内观察时,有

e2 PSK (t ) cos ct cos(ct i ) (i 0或 )

2PSK信号的典型波形

2PSK信号的产生框图

s(t) 双极性不归 零 e2PSK (t) 开关电路 cos ct 0° 180°移相 (b) s(t) e2PSK (t)

码型变换

乘法器

cos ct (a)

2DPSK方式是利用前后相邻码元的相对载波相位值 去表示数字信息的一种方式。CCITT国际标准中对 2DPSK有如下规定:

发“1”时 发“0”时

二进制相移键控(2PSK)

二进制数字信号基带码对载波进行调相分为绝对 移相(2PSK)和相对移相(2DPSK)两种形式。 绝对相移是利用载波的相位(指初相)直接表示 数字信号的相移方式。在绝对移相(PSK)中, 载波起始相位与基带码的关系是:载波0相位对 应基带信号的“1”码;载波 相位对应基带信号 的“0”码。上ห้องสมุดไป่ตู้的对应关系也可以反过来。只要 是载波信号的起始相位与基带信号的“1”码和 “0”码对应关系保持不变的调制方式通称为绝对 移相。

锅炉温度串级控制系统

过程控制仪表课程设计题目:锅炉温度串级控制系统学生姓名:安春雨薛龙朝常玉龙班级:生产过程0901指导老师:张娓娓2011年06月08日•电阻炉是现代工业生产的主要装备,在国民经济建设中具有举足轻重的作用。

本次设计是根据电阻炉温度控制技术的发展要求而设计的一种温度实时串级控制系统。

其控制原理、思想非常适用于自动化程度比较高的企业以及现场环境比较复杂的控制场所。

本系统利用温度传感器、变送器、PLC及其配套的A/D转换器件MAD02、上位计算机等,完成了电阻炉温度可编程控制器串级控制系统的设计,以CX-Programmer、Windows为平台,通过上位机和下位机软件的设计,实现电阻炉温度的实时串级控制。

变送器选择的几个基本原则如下①尽可能选择测量误差小的测量元件。

②尽可能选择快速响应的测量元件与变送设备。

③正确采用微分超前补偿。

④合理选择测量点位置并正确安装。

⑤对测量信号作必要的处理。

锅炉温度串级控制系统框图锅炉温度串级控制系统工作原理•选取炉出口温度为主被控参数(简称主参数),选取炉膛温度为副被控参数(简称副参数),把炉出口温度调节器的输出作为炉膛温度调节器的给定值。

这样,扰动对出口温度的影响主要由炉膛温度调节器(称为副调节器)构成的控制回路(称副回路)来克服,扰动对炉出口温度的影响则由出口温度调节器(称为主调节器)构成的控制回路(称为主回路)来消除。

•用高精度的铂电阻传感器对电热锅炉的水温进行实时精确测量,用JCJ100G温度变送器把传感器的输出信号转换成0~5V标准电压信号,再送入8位的MAD02进行A/D转换,从而实现自动检测。

控制部分采用PID算法,经过PID运算产生的控制信号u(k)是数字信号,将其送入012通道实现D/A 转换,此时在MAD02的输出端就形成了模拟信号,将此模拟信号送入执行机构(温度控制器)。

实时更新PWM控制输出参数,控制可控硅,最终实现对炉温的高精度控制。

热电阻的温度特性系统检测部分采用铂电阻传感器测量输入信号,铂是目前最好的热电阻材料,它在国际使用温标中13.81K~630.74℃范围内作为基准器的复现温标。

通原实验4-数字调制PSK实验

常认为增加一倍;所以DPSK解调大多采用差厚分德相博干学接收追。求卓越

1.8 2DPSK信号解调

B.相干解调-码变换法电路工作原理

以数字序列 =[101001]为例

发送数据 0 1 0 1 0 0 1

2DPSK

0

载波

这就避免了2PSK中的倒π现象发生,为此得到了广泛的工程应用。 相乘输出

低通输出 由以上分析可知,2DPSK与2PSK的波形不同,他们的同一相位

厚德博学 追求卓越

三、实验应知知识

1.数字移相键控PSK调制的基本原理

数字相位调制又称移相键控,简记PSK,二 进制移相键控记作2PSK。它是利用载波相位 的变化来传送数字信息的。

通常有两种类型:

(1)绝对相移(2PSK或BPSK)

(2)相对相移(差分相移/2DPSK 或DBPSK)

厚德博学 追求卓越

1、2DPSK与2PSK信号有相同的功率谱

2、2DPSK与2PSK信号带宽相同,是基带信号带宽Bs的两倍, 即

3、2DPSK与2PSK信号频带利用率也相同,为

B 2DP SB K 2PS K 厚2德fs博学 追求卓越

1.8 2DPSK信号解调

差分相干解调和相干解调-码变换法,后者又称为极性比较-码 变换法。

Ø切忌无目的地拨弄仪器面板上的开关和按钮。

Ø仪器设备出现问题,请向老师寻求帮助,请勿随便调换配件。 Ø注意仪表允许安全电压(或电流),切勿超过!

当被测量的大小无法估计时,应从仪表的最大量程开始测试,然后逐 渐减小量程。

厚德博学 追求卓越

四、实验内容与步骤

实验用数字调制与解调电路模块的基本组成:

PSK调制解调单元模块电路

通信原理实验

第17讲 频带传输:2PSK、QPSK

参考信号

表示前后码 元相位相同

载波同步

载波同步:

在相干解调时,一般需要对接收到的频带信号乘以一个 同频同相的本地载波,那么这个载波: 1)虽然由本地振荡器产生,但必须与频带信号同频同 相

2)频率和相位变换信息从频带信号中提取 这种技术称为载波提取技术,也称载波同步

参考信号 1 (1 1 (1 t 2 cos2 ct cos 2(ccos )) ct ) 2 2 VCO输出

移相器

使用匹配滤波器接收2BPSK信号时,可以将信号表示为:

"1" A cos ct , "1" A cos ct , e2BPSK (t ) "0" A cos(ct ), "0" A cos ct , 此时,在 t =Ts时,对匹配滤波器的输出y(t)进行抽样: Ts y(Ts ) r (t ) h(t ) s( ) n( ) h( t )d

DPSK的相干解调

ˆ an cn cn1

1 cos(c t )cos 1cos(2 11 t t cos(2 c t t ) ) DPSK的差分相干解调 cos c t cos c c 2 c 2

也称相位比较法

表示前后码 元相位不同

LPF输出

1 sin 2 4

锁相环

qpsk调制解调

qpsk调制解调

QPSK调制解调是指在无线通信中应用的一种调技术,也叫作四相

移相 keying(QPSK)。

QPSK是具有相同带宽的其他数字调制技术的改

进版本之一。

它的特点是使用双极平衡阶段调制,同时发出四个相位

状态:00,01,11和10。

QPSK的优势在于能够提高信号性能,同时减

少射频功率的消耗。

在QPSK调制中,每个符号代表2bits,比如发送码 0110,则表示

两个符号,分别对应00和11,即:00 11,此时输出调制信号将位于

45度和135度位置上。

比特流中每个符号都会被调制,用sin和cos

波形表示原始信号。

QPSK调制解调的过程包括调制和解调两个步骤。

调制步骤是将每

个符号(00或11)映射到特定的位置上,通常是45度和135度;接着,将原始信号映射到新的位置上以产生调制信号。

解调步骤是反过来,将接收到的调制信号映射回原始位置,解调后可得到原始比特流。

QPSK调制解调的另一个优势是它在信号传输和处理方面占用较少

的带宽资源。

它通过4倍时间复用将比特流进行压缩,使得比特流可

以更容易地被传输和处理。

另外,QPSK还具有灵活的抗干扰特性,可

以有效抵抗传输噪声,大大提高了信号质量。

总之,QPSK调制解调是一种应用于无线通信的高效率数字调制技术。

它以双极平衡阶段引入四个相位状态进行调制,每个状态分别表

示00,01,11和10。

QPSK能够提高信号性能,有效抵御干扰,同时

节省带宽资源,是一种非常具有经济效益的数字调制技术。

基于FPGA数字移相信号发生器设计

基于FPGA 数字移相信号发生器设计付莉,潘明(桂林电子科技大学 计算机与控制学院 广西 桂林 541004)摘 要:根据直接数字合成器的基本原理,给出了基于FPGA 的直接数字合成器的设计与实现,利用FPGA 有效地扩展了输出波形的频率范围,实现了数字移相信号发生器。

该信号发生器主要采用了直接数字合成器、直接存储器存取、数字移相和数字调幅等技术,对传统的模拟移相不能实现任意波形的移相的缺点方便进行了改进和优化。

关键词:直接数字合成器;FPGA;频率范围;移相信号发生器中图分类号:TP332.3 文献标识码:BDesign of Digital Phase Shift Signal Generator Based on FPGAFu Li ,Pan Ming(School of Computer Science and Control, Guilin University of Electronic Technology, Guilin 541004 , China )Abstract: According to the basic principles of Direct Digital Synthesizer, this article put forward Design and Implementation of the Direct Digital Synthesizer based on FPGA, and extend the output waveform of the frequency range with FPGA effectively. The signal generator used mainly technologies of direct digital synthesizer, a direct memory access, digital phase-shifting and digital AM. It improve and optimise the traditional analog phase-shifting arbitrary waveforms which can not be realized the shortcomings of the phase-shifting facilitate.Key word :Direct Digital Synthesizer; Frequency range; Digital Phase Shift Signal Generator0 引言DDS 即Direct Digital Synthesizer ,中文名称是直接数字合成器,是一种新型的频率合成技术,具有较高的频率分辨率,可以实现快速的频率切换,并且在改变时能够保持相位连续,很容易实现频率、相位和幅度的数控调制。

三相晶闸管移相触发器IP核的开发

V2/-1/5P;#)=54>#)=9 8%29’(4*:.O74IM.54/I-./00/1.2306456/4.7154/;15K60/T645G43KK3S0/05GI1N/RI1/(8,*’)

!#

的脉动波形。三相全控桥式整流电路在任何时刻必 须保证有两个不同组别的晶闸管同时导通才能构成 回路。换流 只 在 本 组 内 进 行,每 隔 ":#<换 流 一 次。 由于共阴 极 组 与 共 阳 极 组 的 换 流 点 相 隔 >#<,所 以 每隔>#<有一个元件换流。同组内各晶闸管的触发 脉冲相位 差 为 ":#<。 接 在 同 一 相 的 两 个 元 件 的 触 发脉冲 相 位 差 为 "%#<,而 相 邻 两 脉 冲 的 相 位 差 是 >#<。各元件触发脉冲顺序见图"S。

-$%时,计 数 器 重 新 开 始 计 数,并 输 出 第 二 次 脉 冲。 当脉冲选择计数器为-时,脉冲计数器被停止。

! 设计的验证及结论

9:核设计采用 ;<=> 语言实现,在多种 ?=’ 软件中进行过仿真验证。图,为 @’A:>BC99仿真 软件[)]中分别对应 !D$ 和 !D"#$%时 的 输 出 脉 冲 时序仿真图,程序最终下载到 E:>=中得以验证。

该模块的数据输入(./0/)来自移位寄存器模块 的锁存输出端口。在同步信号上升沿到来之前,./0/ 被置入计数器。当方波同步信号(123)的上升沿到 来时,移相计数器开始减法计数,移相计数器的启动

智能电表检定装置发展现状

工业技术科技创新导报 Science and Technology Innovation Herald85DOI:10.16660/ki.1674-098X.2020.14.085智能电表检定装置发展现状吕付刚 陈媛媛(烟台东方威思顿电气有限公司 山东烟台 264003)摘 要:智能电表是电力系统运营的关键计量环节,在我国被划归为强检计量器具。

智能电表在使用前必须通过相关检验流程,并在日常使用中开展周期性检验。

在电能表检定装置中,最重要的组成部分是标准表,其准确度决定检定装置的好坏。

中国标准智能电表在初期运用模拟乘法器技术,现阶段正在向采样计算技术变革。

目前中国智能电表数量可观,同时高性能的智能电表逐步上市,智能电表检定装置相关技术研究十分必要。

关键词:智能电表 智能电表检定装置 发展现状中图分类号:TM73 文献标识码:A 文章编号:1674-098X(2020)05(b)-0085-02中国电力系统正在逐步成熟,智能电表作为电力系统重要环节,关键指标准确度受到工程师的关注,对应的智能电表检定装置成为研究热点。

其中城网、农网电力系统,正在进行更新升级,新并网设备在功能、结构上与初期一代电能表区别较大。

针对当时情况,国家在2002年颁布GB/T11150-2001《智能电表检验装置》,后期为适应新型电能表的更新,2006年颁布JJG597-2005《交流智能电表检定装置检定规程》,在标准制定中,抓住最新版国标《1级和2级静止式交流有功智能电表》与《0.2s和0.5s级静止式交流有功智能电表》中有关电磁兼容与谐波影响问题,更新了现有标准中的漏洞,是现行被行业认可的标准。

1 装置用标准表现具备采样计算技术的电能表受到行业认可已经占据大部分市场。

但模拟乘法器技术因成本低、运行稳定,在部分低端产品中仍继续使用。

1.1 模拟式标准表时分割乘法器在80年代中期被提出,迅速在全国范围行业内被认可,功率电能测量技术进入崭新的时代。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一.两个同频信号之间的移相与实现方式 所谓移相是指两路同频的信号,以其中的一路为参考,另一路相对于该参考作超前或滞后的移动,即称为是相位的移动。

两路信号的相位不同,便存在相位差,简称相差。

若我们将一个信号周期看作是3600,则相差的范围就在00∽3600之间。

例如在图1中,以A信号为参考,B信号相对于A信号作滞后移相φ0,则称A超前Bφ0,或称B滞后Aφ0。

图1 移相示意 要实现B信号对A信号的移相,通常有两个途径:一是直接对模拟信号进行移相,如阻容移相,变压器移相等,早期的移相通常采用这种方式。

采用这种方式制造的移相器有许多不足之处,如:输出波形受输入波形的影响,移相操作不方便,移相角度随所接负载和时间等因素的影响而产生漂移等.在此不予讨论.另一个是随电子技术的发展,特别是单片机技术的发展而发展起来的数字移相技术,是目前移相技术的潮流。

数字移相技术的核心是:先将模拟信号或移相角数字化,经移相后再还原成模拟信号。

数字移相主要有两种形式:一种是先将正弦波信号数字化,并形成一张数据表存入ROM芯片中,此后可通过两片D/A转换芯片在单片机的控制下连续地循环输出该数据表,就可获得两路正弦波信号,当两片D/A转换芯片所获得的数据序列完全相同时,则转换所得到的两路正弦波信号无相位差,称为同相。

当两片D/A转换芯片所获得的数据序列不同时,则转换所得到的两路正弦波信号就存在着相位差。

相位差的值与数据表中数据的总个数及数据地址的偏移量有关。

这种处理方式的实质是将数据地址的偏移量映射为信号间的相位值。

另一种是先将参考信号整形为方波信号,并以此信号为基准,延时产生另一个同频的方波信号,再通过波形变换电路将方波信号还原成正弦波信号。

以延时的长短来决定两信号间的相位值。

这种处理方式的实质是将延时的时间映射为信号间的相位值。

二.利用D/A转换实现移相 图2给出了一个设计实例。

单片机为8031,D/A转换芯片采用两片8位字长的DAC0832,由于DAC0832的输出信号为电流型,故需加运算放大器将电流型信号转换成电压型信号。

该设计中运算放大器采用双极型双运放4558。

转换所用的数据为256个8位字长的数据,随程序一起存入ROM存储器中,即一个信号周期有256个转换值。

图2 D/A转换移相框图 进行D/A转换的程序段及正弦波的数值表如下:程序清单:MOV R5,#00H;第一路正弦波起点地址的偏移量送R5MOV R1,#08H;第二路正弦波起点地址的偏移量送R1LOOP:MOV A, R5MOV DPTR,#TAB;取数据表首地址MOVC A,@DPTR;取第一路数据MOV DPTR,#0DFFFH;选通第一路DAC0832MOVX @DPTR,A;数据送第一路DAC0832INC R5;修改第一路地址的偏移量MOV A,R1;MOV DPTR,#TAB:MOVC A,@DPTR;取第二路数据MOV DPTR,#0BFFFH:选通第二路DAC0832MOVX @DPTR,A;数据送第二路DAc0832INC R1:修改第二路地址的偏移量MOV DPTR,#7FFFH;选通两片DAC0832的转换端MOVX @DPIR,A;同时转换两路数据AJMP LOOPTAB:DB 80,83,86,89,90,93,96DB 99,9C,9F,A2,A5,A8,AB,AEDB B1,B4,B7,BA,BC,BF,C2,C5DB C7,CA,CC,CP,D1,D4,D6,D8DB DA,DD,DF,E1,E3,E5,E7,E9DB EA,EC,EE,EF,F1,F2,F4,F5DB F6,F7,F8,F9,FA,FB,FC,FDDB FD,FE,FF,FF,FF,FF,FF,FFDB FF,FF,FF,FF,FF,FF,FE,FDDB FD,FC,FB,FA,F9,F8,F7,F6DB F5,F4,F2,F1,EF,EE,EC,EADB E9,E7,E5,E3,E1,DF,DD,DADB D8,D6f D4,D1,CF,CC,CA,C7DB C5,C2,BF,BC,BA,B7,B4,B1DB AE,AB,A8,A5,A2,9F,9C,99DB 96,93,90,8D,89,86,83,8ODB 80,7C,79,76,72,6F,6C,69DB 66,63,60,5D,5A,57,55,51DB 4E,4C,48,45,43,40,3D,3ADB 38,35,33,30,2E,2B,29,27DB 25,22,20,1E,1C,1A,18,16DB 15,13,11,10,0E,0D,0B,0ADB 09,08,07,06,05,04,03,02DB 02,01,00,00,00,00,00,00DB 00,00,00,00,00,00,01,02DB 02,03,04,05,06,07,08,09DB 0A,0B,0D,0E,10,11,13,15DB 16,18,1A,1C,1E,20,22,25DB 27,29,2B,2E,30,33,35,38DB 3A,3D,40,43,45,48,4C,4EDB 51,55,57,5A,5D,60,63,66DB 69,6C,6F,72,76,79,7C,80 此例中,数据表中数据共有256个,每两个相邻数据之间的相位差为3600÷256=1.40。

我们只需改变R1中的值就可改变两路正弦波的相位差。

程序中R1=8,故第一路正弦波滞后第二路正弦波1.40×8=11.20。

现将以这种方式实现移相的几个技术指标作如下分析: 1.波形失真度;正弦波的转换精度若不加其它的处理,则取决于D/A转换芯片的位数和数据表中数据的准确度。

8位的D/A转换芯片其输入数据的范围是0-255,也就是说最多可将模拟量分为256级。

在双级型的转换中,正、负半波被分为128级。

2.正弦波的周期;正弦波的周期由对数据表作一遍完整的转换所需要的时间决定。

显然,单片机的速度、数据表中数据的个数以及程序的算法等因素都将影响正弦波的周期。

上例中设8031的晶振频率为6MHz,则程序完成一个数据的转换所需要的时间是52us,故正弦波的周期为K×52 us×256=K×13312 us。

K为转换下一个数据前等待的时间系数,当K=l时,为连续转换,此时正弦波的周期最短。

3.移相细度;移相细度(最小移动步长)取决于数据表中数据的个数,数据越多则移相细度越细。

上例中数据表中数据的个数为256个,所以移相细度为3600÷256=1.40。

若数据表中数据的个数为360个,则移相细度为3600÷360=10。

表面上看,只要增加数据的个数,就可提高移相细度,但在不增加D/A芯片的位数的情况,单纯增加数据的个数,会使正弦波波形的失真度增加,并使正弦波的周期变长。

在正弦波周期一定的情况下,数据表中数据的个数是有限制的。

三.利用单片机进行方波信号的移相 利用单片机进行方波信号的移相则是数字移相的另一个途经,已有多种成功之作,有些偏重硬件,有些偏重软件,总体说来,偏重硬件的精度较高,但制造及调试较复杂。

偏重软件的结构简单,成本较低,但往往精度受影响。

本文介绍一种己获得较为理想效果的设计。

设计的原理框图如图3所示。

upload/article/2005122581313.gif[/IMG]图3 方波移相框图 工作原理:作为参考信号的A,经整形后得到方波信号a,再利用锁相技术对a作3600倍频,并将此倍频信号作为单片机中CTC的计数脉冲,以此来产生相移和测量移相的实际值。

由于计数脉冲是通过锁相环产生的,在锁相环允许的频率范围内,计数脉冲始终是a信号的3600倍,因此,可以看成是将a信号的一个信号周期分为了3600份,且允许a 的频率可在一个小的范围内波动。

若一个信号周期为3600,那么在一个信号周期内每个计数脉冲即代表0.10。

我们只需以a信号为参考,延时若干个计数脉冲的时间来产生c信号即可做到移相,改变延时计数脉冲的个数即可改变移相值,亦可记录两个信号的上沿(或下沿)间的脉冲个数来获得两信号的相位差。

正是由于锁相环的存在,才使得移相信号B与参考信号A的频率完全相同。

比起由软件测得A信号的周期后再来产生B 信号的方式来,其精度要高得多。

锁相环倍频的频率愈高则移相的最小单位愈小,若作7200倍频,那么在一个信号周期内每个计数脉冲即代表0.050。

图4 移相时序 图4是以上述方式进行移相的时序图,设计数脉冲的频率是a信号的3600倍,那么从a信号的上沿开始经N个计数脉冲后产生c信号的上沿,则有a信号超前c信号 N×0.10。

但我们需要的是A信号与B信号之间的移相。

A信号与a信号的相位是相同的,但c信号与B信号的相位,由于波形转换电路的存在而不相同,其相位差视波形转换电路的参数而定。

故A信号与B信号之间的实际移相值无法由N×0.10来计算。

要获得A信号与B信号之间的实际移相值,可将B信号整形成b信号(两信号相位相同)后反馈给单片机,由单片机测量出a信号与b信号之间的计数脉冲个数n即可,实际移相值为n×0.10。

改变N的值即可改变移相值。

要实现上述设计,除需要用锁相环产生计数脉冲外,还需要三个16位的计数器,分别用来计N,n及1800的值。

笔者将8032中的计数器作如下分配:T0计N的值、T1计n的值、T2计1800的值。

T0、T1及T2的启停全部由中断服务程序控制。

接线如图3所示。

具体是: ① a信号的上沿产生INT0中断,其中断服务程序分别将-N及0赋给TH0TL0和TH1TL1;然后使T0、T1开始计数。

② T0归零,其中断服务程序关闭T0;置P3.0;-1800赋TH2TL2;使T2开始计数。

③ T2归零,其中断服务程序清P3.0;关闭T2。

④ b信号的上沿产生INT0中断,其中断服务程序关闭T1;读取TH1TL1的计数值n.。

四.两种移相方式的性能比较 通过以上介绍,我们可以看到:以D/A转换方式实现的移相,虽然所用元件少,但输出信号的频率难以细调,特别是移相的最小单位太大 (1.40/步)。

在50Hz频率下,要达到0.10/步移相细度难以办到。

因此,该方式只适合于对频率要求不高,且移相角度固定的场合。

以延时输出方波的方式实现的移相,其硬件电路比较复杂(锁相及波形变换电路)。

输出信号的频率以参考信号的频率为准,而参考信号的频率则可以精确给定。

移相的最小单位可小于0.10/步,这就为无级移相提供了基础。

因此,该方式可用于对频率要求高,且需3600无级移相的场合。

参考资料1.王秉时,移相技术的发展与移相器产品的进步,《电测与仪表》1998。