74LS373应用介绍

74LS373中文资料_数据手册_参数

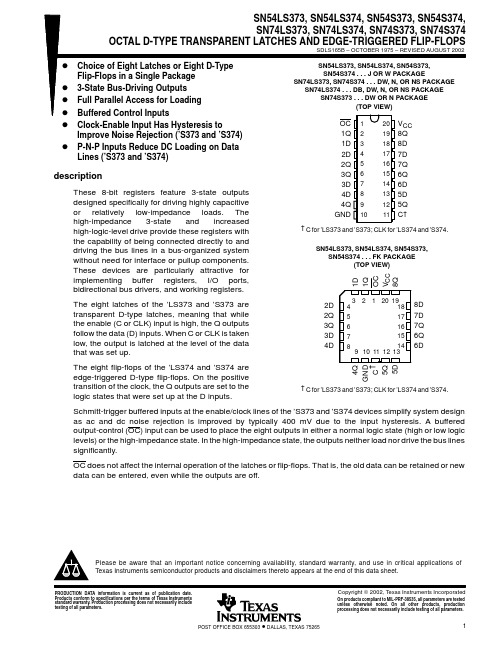

4Q

GND

C†

† C for ’LS373 and ’S373; CLK for ’LS374 and ’S374.

5Q

5D

Schmitt-trigger buffered inputs at the enable/clock lines of the ’S373 and ’S374 devices simplify system design as ac and dc noise rejection is improved by typically 400 mV due to the input hysteresis. A buffered output-control (OC) input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or the high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly.

DM74LS373中文资料

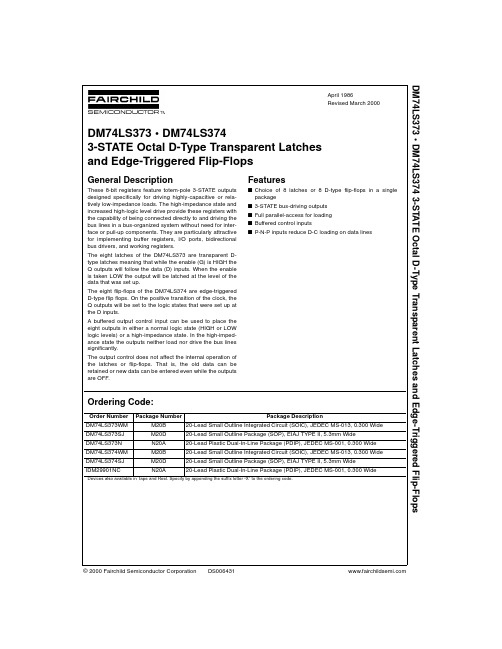

© 2000 Fairchild Semiconductor Corporation DS006431April 1986Revised March 2000DM74LS373 • DM74LS374 3-STATE Octal D-Type Transparent Latches and Edge-Triggered Flip-FlopsDM74LS373 • DM74LS3743-STATE Octal D-Type Transparent Latches and Edge-Triggered Flip-FlopsGeneral DescriptionThese 8-bit registers feature totem-pole 3-STATE outputs designed specifically for driving highly-capacitive or rela-tively low-impedance loads. The high-impedance state and increased high-logic level drive provide these registers with the capability of being connected directly to and driving the bus lines in a bus-organized system without need for inter-face or pull-up components. They are particularly attractive for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.The eight latches of the DM74LS373 are transparent D-type latches meaning that while the enable (G) is HIGH the Q outputs will follow the data (D) inputs. When the enable is taken LOW the output will be latched at the level of the data that was set up.The eight flip-flops of the DM74LS374 are edge-triggered D-type flip flops. On the positive transition of the clock, the Q outputs will be set to the logic states that were set up at the D inputs.A buffered output control input can be used to place the eight outputs in either a normal logic state (HIGH or LOW logic levels) or a high-impedance state. In the high-imped-ance state the outputs neither load nor drive the bus lines significantly.The output control does not affect the internal operation of the latches or flip-flops. That is, the old data can be retained or new data can be entered even while the outputs are OFF.Featuress Choice of 8 latches or 8 D-type flip-flops in a single package s 3-STATE bus-driving outputs s Full parallel-access for loading s Buffered control inputss P-N-P inputs reduce D-C loading on data linesOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Order Number Package NumberPackage DescriptionDM74LS373WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide DM74LS373SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide DM74LS373N N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide DM74LS374WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide DM74LS374SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide IDM29901NCN20A20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide 2D M 74L S 373 • D M 74L S 374Connection DiagramsDM74LS373DM74LS374Function TablesDM74LS373DM74LS374H = HIGH Level (Steady State)L = LOW Level (Steady State)X = Don’t CareZ = High Impedance State↑ = Transition from LOW-to-HIGH levelQ 0 = The level of the output before steady-state input conditions were established.Logic DiagramsDM74LS373Transparent LatchesDM74LS374Positive-Edge-Triggered Flip-FlopsOutput Enable D Output ControlG L H H H L H L L L L X Q 0HXXZOutput Clock D Output ControlL ↑H H L ↑L L L L X Q 0HXXZDM74LS373 • DM74LS374Absolute Maximum Ratings (Note 1)Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings.The “Recommended Operating Conditions” table will define the conditions for actual device operation.DM74LS373 Recommended Operating ConditionsNote 2: The symbol (↓) indicates the falling edge of the clock pulse is used for reference.Note 3: T A = 25°C and V CC = 5V.DM74LS373 Electrical Characteristicsover recommended operating free air temperature range (unless otherwise noted)Note 4: All typicals are at V CC = 5V, T A = 25°C.Note 5: Not more than one output should be shorted at a time, and the duration should not exceed one second.Supply Voltage 7V Input Voltage7VStorage Temperature Range−65°C to +150°COperating Free Air Temperature Range0°C to +70°CSymbol ParameterMin Nom Max Units V CC Supply Voltage4.7555.25V V IH HIGH Level Input Voltage 2V V IL LOW Level Input Voltage 0.8V I OH HIGH Level Output Current −2.6mA I OL LOW Level Output Current 24mA t W Pulse Width Enable HIGH 15ns (Note 3)Enable LOW15t SU Data Setup Time (Note 2) (Note 3)5↓ns t H Data Hold Time (Note 2) (Note 3)20↓ns T AFree Air Operating Temperature70°CSymbol ParameterConditionsMinTyp Max Units (Note 4)V I Input Clamp Voltage V CC = Min, I I = −18 mA −1.5V V OH HIGH Level V CC = Min, I OH = Max 2.4 3.1VOutput Voltage V IL = Max, V IH = Min V OLLOW Level V CC = Min, I OL = MaxOutput VoltageV IL = Max, V IH = Min 0.350.5VI OL = 12 mA, V CC = Min 0.4I I Input Current @ Max Input Voltage V CC = Max, V I = 7V 0.1mA I IH HIGH Level Input Current V CC = Max, V I = 2.7V 20µA I IL LOW Level Input Current V CC = Max, V I = 0.4V −0.4mA I OZH Off-State Output Current with V CC = Max, V O = 2.7V 20µA HIGH Level Output Voltage Applied V IH = Min, V IL = Max I OZL Off-State Output Current with V CC = Max, V O = 0.4V −20µA LOW Level Output Voltage Applied V IH = Min, V IL = Max I OS Short Circuit Output Current V CC = Max (Note 5)−50−225mA I CCSupply CurrentV CC = Max, OC = 4.5V,2440mA D n , Enable = GND 4D M 74L S 373 • D M 74L S 374DM74LS373 Switching Characteristicsat V CC = 5V and T A = 25°CNote 6: C L = 5 pF.DM74LS374 Recommended Operating ConditionsNote 7: The symbol (↑) indicates the rising edge of the clock pulse is used for reference.Note 8: T A = 25°C and V CC = 5V.R L = 667ΩSymbol ParameterFrom (Input)C L = 45 pF C L = 150 pF UnitsTo (Output)MinMax MinMax t PLH Propagation Delay Time Data to Q 1826ns LOW-to-HIGH Level Output t PHL Propagation Delay Time Data to Q 1827ns HIGH-to-LOW Level Output t PLH Propagation Delay Time Enable to Q 3038ns LOW-to-HIGH Level Output t PHL Propagation Delay Time Enable to Q 3036ns HIGH-to-LOW Level Output t PZH Output Enable Time Output Control to Any Q 2836ns to HIGH Level Output t PZL Output Enable Time Output Control to Any Q 3650ns to LOW Level Output t PHZ Output Disable TimeOutput Control to Any Q 20ns from HIGH Level Output (Note 6)t PLZOutput Disable TimeOutput Control to Any Q25nsfrom LOW Level Output (Note 6)Symbol ParameterMin Nom Max Units V CC Supply Voltage4.7555.25V V IH HIGH Level Input Voltage 2V V IL LOW Level Input Voltage 0.8V I OH HIGH Level Output Current −2.6mA I OL LOW Level Output Current 24mA t W Pulse Width Clock HIGH 15ns (Note 8)Clock LOW15t SU Data Setup Time (Note 7) (Note 8)20↑ns t H Data Hold Time (Note 7) (Note 8)1↑ns T AFree Air Operating Temperature70°CDM74LS373 • DM74LS374DM74LS374 Electrical Characteristicsover recommended operating free air temperature range (unless otherwise noted)Note 9: All typicals are at V CC = 5V, T A = 25°C.Note 10: Not more than one output should be shorted at a time, and the duration should not exceed one second.DM74LS374 Switching Characteristicsat V CC = 5V and T A = 25°CNote 11: C L = 5 pF.Symbol ParameterConditionsMinTyp Max Units (Note 9)V I Input Clamp Voltage V CC = Min, I I = −18 mA −1.5V V OH HIGH Level V CC = Min, I OH = Max 2.43.1VOutput Voltage V IL = Max, V IH = Min V OLLOW Level V CC = Min, I OL = Max0.350.5VOutput VoltageV IL = Max, V IH = Min I OL = 12 mA, V CC = Min 0.250.4I I Input Current @ Max Input Voltage V CC = Max, V I = 7V 0.1mA I IH HIGH Level Input Current V CC = Max, V I = 2.7V 20µA I IL LOW Level Input Current V CC = Max, V I = 0.4V −0.4mA I OZH Off-State Output Current with V CC = Max, V O = 2.7V 20µA HIGH Level Output Voltage Applied V IH = Min, V IL = Max I OZL Off-State Output Current with V CC = Max, V O = 0.4V −20µA LOW Level Output Voltage Applied V IH = Min, V IL = Max I OS Short Circuit Output Current V CC = Max (Note 10)−50−225mA I CCSupply CurrentV CC = Max, D n = GND, OC = 4.5V2745mAR L = 667ΩSymbol Parameter C L = 45 pF C L = 150 pF Units Min MaxMin Maxf MAX Maximum Clock Frequency 3520MHz t PLH Propagation Delay Time 2832ns LOW-to-HIGH Level Output t PHL Propagation Delay Time 2838ns HIGH-to-LOW Level Output t PZH Output Enable Time 2844ns to HIGH Level Output t PZL Output Enable Time 2844ns to LOW Level Output t PHZ Output Disable Time20ns from HIGH Level Output (Note 11)t PLZOutput Disable Time25nsfrom LOW Level Output (Note 11) 6D M 74L S 373 • D M 74L S 374Physical Dimensionsinches (millimeters) unless otherwise noted20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 WidePackage Number M20B DM74LS373 • DM74LS374Physical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M20D8D M 74L S 373 • D M 74L S 374 3-S T A TE O c t a l D -T y p e T r a n s p a r e n t L a t c h e s a n d E d g e -T r i g g e r e dF l i p -F l o p sPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N20AFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

74AC573介绍

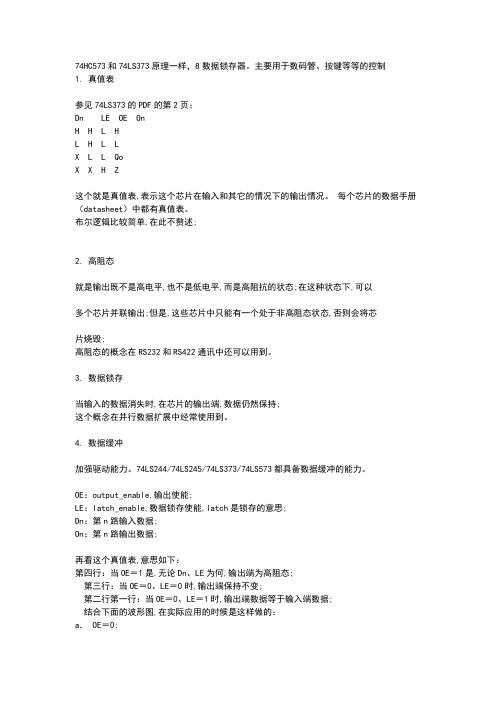

74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制1. 真值表参见74LS373的PDF的第2页:Dn LE OE OnH H L HL H L LX L L QoX X H Z这个就是真值表,表示这个芯片在输入和其它的情况下的输出情况。

每个芯片的数据手册(datasheet)中都有真值表。

布尔逻辑比较简单,在此不赘述;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁;高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力。

74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

OE:output_enable,输出使能;LE:latch_enable,数据锁存使能,latch是锁存的意思;Dn:第n路输入数据;On:第n路输出数据;再看这个真值表,意思如下:第四行:当OE=1是,无论Dn、LE为何,输出端为高阻态;第三行:当OE=0、LE=0时,输出端保持不变;第二行第一行:当OE=0、LE=1时,输出端数据等于输入端数据;结合下面的波形图,在实际应用的时候是这样做的:a. OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:mov P0,A ;将数据输出到并行数据端口clr LEsetb LEclr LE ;上面三条指令完成LE的波形从0->1->0的变化74ls573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端。

EDA74LS3738位三态锁存器设计

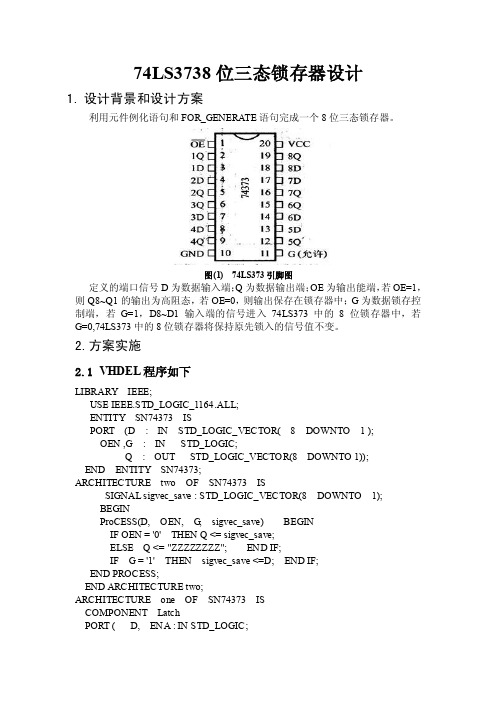

74LS3738位三态锁存器设计1.设计背景和设计方案利用元件例化语句和FOR_GENERATE语句完成一个8位三态锁存器。

图(1) 74LS373引脚图定义的端口信号D为数据输入端;Q为数据输出端;OE为输出能端,若OE=1,则Q8~Q1的输出为高阻态,若OE=0,则输出保存在锁存器中;G为数据锁存控制端,若G=1,D8~D1输入端的信号进入74LS373中的8位锁存器中,若G=0,74LS373中的8位锁存器将保持原先锁入的信号值不变。

2.方案实施2.1 VHDEL程序如下LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SN74373 ISPORT (D : IN STD_LOGIC_VECTOR( 8 DOWNTO 1 );OEN ,G : IN STD_LOGIC;Q : OUT STD_LOGIC_VECTOR(8 DOWNTO 1));END ENTITY SN74373;ARCHITECTURE two OF SN74373 ISSIGNAL sigvec_save : STD_LOGIC_VECTOR(8 DOWNTO 1);BEGINProCESS(D, OEN, G, sigvec_save) BEGINIF OEN = '0' THEN Q <= sigvec_save;ELSE Q <= "ZZZZZZZZ"; END IF;IF G = '1' THEN sigvec_save <=D; END IF;END PROCESS;END ARCHITECTURE two;ARCHITECTURE one OF SN74373 ISCOMPONENT LatchPORT ( D, ENA : IN STD_LOGIC;Q : OUT STD_LOGIC );END COMPONENT;SIGNAL sig_mid : STD_LOGIC_VECTOR( 8 DOWNTO 1);BEGINGeLatch : FOR iNum IN 1 TO 8 GENERATELatchx : Latch PORT MAP(D(iNum), G , sig_mid(iNum) );END GENERATE;Q <= sig_mid WHEN OEN = '0' ELSE"ZZZZZZZZ";END ARCHITECTURE one ;2.2程序分析(1)程序中有两个结构体,以不同的电路来实现相同的逻辑,即一个实体可以对应多个结构体,每个结构体对应一种实现方案。

74HC373中文资料

74HC373和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制1. 真值表Dn LE OE OnH H L HL H L LX L L QoX X H Z这个就是真值表,表示这个芯片在输入和其它的情况下的输出情况。

每个芯片的数据手册(datasheet)中都有真值表。

布尔逻辑比较简单,在此不赘述;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁; 高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力。

74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

OE:output_enable,输出使能;LE:latch_enable,数据锁存使能,latch是锁存的意思;Dn:第n路输入数据;On:第n路输出数据;再看这个真值表,意思如下:第四行:当OE=1是,无论Dn、LE为何,输出端为高阻态;第三行:当OE=0、LE=0时,输出端保持不变;第二行第一行:当OE=0、LE=1时,输出端数据等于输入端数据;结合下面的波形图,在实际应用的时候是这样做的:a.OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:mov P0,A ;将数据输出到并行数据端口clr LEsetb LEclr LE ;上面三条指令完成LE的波形从0->1->0的变化74ls573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端。

74hc373锁存器作用

74HC373锁存器作用什么是74HC373锁存器?74HC373是一种集成电路芯片,属于高速CMOS逻辑系列,由意法半导体公司生产。

它是一种8位锁存器,可用于在数字电路中存储8位数据。

锁存器是数电中常见的一个功能模块,用于存储和保持信号。

74HC373锁存器的作用74HC373锁存器在数字电路中起到重要的作用,以下是几个典型的应用场景:1. 数据缓存在某些情况下,需要将某个电平的信号保持一段时间,并在需要时输出。

74HC373锁存器可以用作数据缓存,将输入信号锁存,并在需要时输出。

这在通信系统、计算机存储和控制电路中经常使用。

通过将数据输入到锁存器中,可以防止数据丢失,确保在更合适的时机进行处理。

2. 数据传输74HC373锁存器通常被用作数据传输的工具。

当需要将数据从一个电路传输到另一个电路时,可以使用锁存器来暂存待传输的数据。

通过将数据输入到锁存器中,并在需要传输时将数据输出,可以确保数据传输的可靠性和稳定性。

3. 地址寄存器在微处理器系统中,锁存器经常被用作地址寄存器。

地址寄存器用于存储指令的地址,以便微处理器能够从存储器中读取指令。

通过使用74HC373锁存器作为地址寄存器,可以实现高效的地址存储和解码。

4. 控制信号在数字电路中,锁存器也可以用于存储和控制信号的生成。

通过将控制信号输入到锁存器中,并根据需要输出,可以实现复杂的控制逻辑。

锁存器可以存储不同的控制状态,并在需要时将相应的控制信号输出到其他电路中,从而实现对数字系统的控制。

5. 边沿检测锁存器还可以用于边沿检测。

在数字信号处理中,有时需要检测信号的上升沿或下降沿。

通过将信号输入到锁存器中,并与之前的状态进行比较,可以检测到信号的边沿。

这对于时序控制和触发器电路非常有用。

总结74HC373锁存器是一种常见的集成电路芯片,用于存储和保持信号。

它的作用多种多样,可以用于数据缓存、数据传输、地址寄存器、控制信号和边沿检测等场景。

锁存器在数字电路中起到重要的作用,对于数字系统的设计和控制至关重要。

74LS373在单片机接口中的应用

!

般用 与

的

万 弃 的 端不再

了

” 泛 二二二 甲 一 公、

二二

月

飞

八

以〕

从

相连 而 由

,

和

决定

。

在

里

图

了

一

厂

!

在 作为扩 展

!

,

时 的地 址 锁 存器 都利 用 其锁存 功

,

使 用 时和 作 为扩展

以 实现

口

,

口 使 用时

,

能 但工 作方式完全 不同 前者 用于锁存低剐立地址

。

月

口

的 分 时复 用 后 者 用 于 作 为输入 输 出

,

、

撰然翼群 蒸

,

,

。

资格 考 试 是 针 对那些 具 备 了晋升 职 称条件

不 受 资历 限 制

。

为那些 有志 青年提供 了一

,

、

的 原 因 是 多方 面 的 最 主要 的是 一

,

。

各级 领

、

二

、

计算 机 软 件人 员数量 增 加 素质 普遍 提 高

, ,

,

三

考前

,

培 训 工 作抓得好 省考 办 及 各市 地 考 试 办 积极 举 办 各个 级 别 的考前辅 导 班 提 高 了 考 试 的 合格率 四 各个 大 学 大 中专院 校学 生 走 出了 象 牙 塔 为培养 自己 的 实践 能力 赶 上 社 会 的最 新发 展 积 极 报名 参加考 试 为将 来走 向社会奠 定 了 良好 的基础 供万年报 名工 作即 将 开 始 相 应的考 前培 训工 作 已 在全 省名 市 地 全面展 开 张玲

74ls373中文资料

LS373 最小 最大

单位

VIK输入嵌位电压

Vcc=最小,Iik=-18mA

-1.5

-1.5 V

VOH输出高电平电压

Vcc=最小,VIL=最大, VIH=2V,IOH=最大

2.4

2.4

V

VOL输出低电平电压

Vcc=最小,VIL=最大, VIH=2V,IOL=最大

54 74

0.5 0.5

0.4 0.5

OE 到 O0~O7

(LS373 为 667 Ω)

45pF)

15

28

ns

18

36

tPHZ

OE 到

tPLZ

O0~O7

9

20

CL=5pF

12

ns 25

[2] tPLH输出由低到高传输延迟时间 tPHL输出由高到低传输延迟时间

17ic电子渠道网可为您提供免费的中文资料、电路图 等资料并可提供在线采购电子元器件等

本站最新动态

·3.1号起本站将实行新的会员收费标准 ·会员管理中心推出重复库存清除功能 ·教您如何选择一个好的IC交易平台! ·你的论坛你做主,赶快来体验吧 ·好消息:本站所有广告按点击次数…

MCP1316中文资料MCP1317应用MCP1318 MCP1319封装 图MCP1320管脚

·MCP111 中文资料 MCP112 应用 pdf … ·MCP102中文资料MCP103应用MCP1… ·MCP41010 中文资料 MCP41050 应用… ·MCP40D17中文资料 MCP40D18应用… ·DS12R885 中文资料 DS12CR887 应… ·MAX6972ATJ 中文资料 MAX6973AT… ·MCP14E3中文资料MCP14E4 应用 pd… ·MCP6V06中文资料 MCP6V07应用 p… ·MCP6V01中文资料MCP6V02应用 pd… ·MCP6S91中文资料 MCP6S92应用 pd…

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片.本文将介绍74ls373的工作原理,引脚图(管脚图),内结构图、主要参数及在单片机系统中的典型应用电路.

74ls373工作原理简述:

(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);

(2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.

锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。

当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

74ls373内部逻辑结构图

74LS373的真值表(功能表),表中:

L——低电平;

H——高电平;

X——不定态;

Q0——建立稳态前Q的电平;

G——输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。

图中OE——使能端,接地。

当G=“1”时,74LS373输出端1Q—8Q与输入端1D—8D相同;

当G为下降沿时,将输入数据锁存。

74ls373引脚(管脚)排列图:

74ls373电气特性

74ls373推荐工作条件

74ls373在单片机系统中的应用电路图:

当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。

51单片机的ALE信号可以直接与74LS373的C连接。

在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。

其中输入端

1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。

输出允许端OE接地,表示输出三态门一直打开。

1D~8D为8个输入端。

1Q~8Q为8个输出端。

G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。

OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。

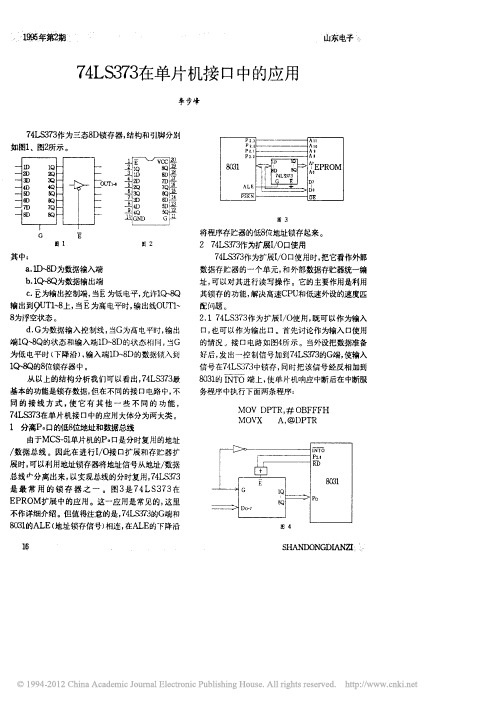

74LS373在单片机接口中的应用李步峰74LS373作为三态8D锁存器,结构和引脚分别如图1、图2

所示。

其中:a.1D~8D为数据输入端b.1Q~8Q为数据输出端c.E为输出控制端,当E为低电平,允许1Q~8Q输出到OUT1~8上,当E为高电平时,输出线OUT1~8为浮空状态。

d.G为数据输入控制线,当G为高电平时,输出端1Q~8Q的状态和输入端1D~8D的状态相同,当G为低电平时(下降沿),输入端1D~8D的数据锁入到1Q~8Q的8位锁存器中。

从以上的结构分析我们可以看出,74LS373最基本的功能是锁存数据,但在不同的接口电路中,不同的接线方式,使它有其他一些不同的功能,74LS373在单片机接口中的应用大体分为两大类。

1分离P_o口的低8位地址和数据总线由于MCS-51单片机的P_o口是分时复用的地址/数据总线。

因此在进行I/O接口扩展和存贮器扩展时,可以利用地址锁存器将地址信号从地址/数据总线中分离出来,以实现总线的分时复用,74LS373是最常用的锁存器之一。