74LS373详细资料精心整理

74LS373中文资料_数据手册_参数

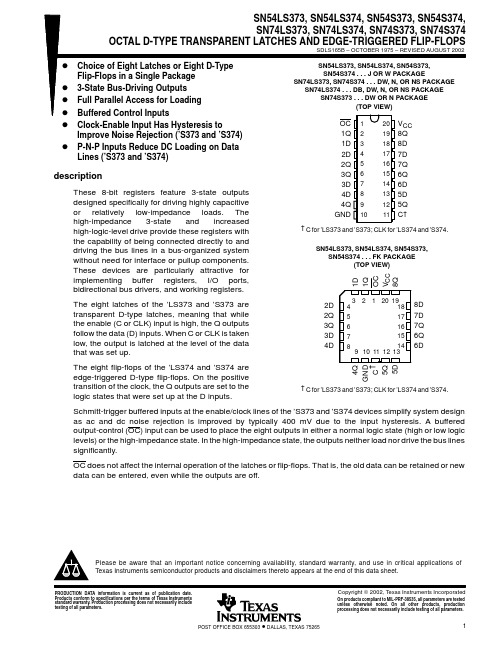

4Q

GND

C†

† C for ’LS373 and ’S373; CLK for ’LS374 and ’S374.

5Q

5D

Schmitt-trigger buffered inputs at the enable/clock lines of the ’S373 and ’S374 devices simplify system design as ac and dc noise rejection is improved by typically 400 mV due to the input hysteresis. A buffered output-control (OC) input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or the high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly.

74ls373引脚图管脚功用表阐明

74ls373引脚图管脚功用表阐明74ls373是常用的地址锁存器芯片,它本质是一个是带三态缓冲输出的8D触发器,在单片机体系中为了拓展外部存储器,一般需求一块74ls373芯片,74ls373内部构造图与74ls373引脚图(1).1脚是输出使能(OE),是低电平有用,当1脚是高电往常,不论输入3、4、7、8、13、14、17、18怎么,也不论11脚(锁存操控端,G)怎么,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)悉数呈现高阻状况(或许叫浮空状况);(2).当1脚是低电往常,只需11脚(锁存操控端,G)上呈现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)当即呈现输入脚3、4、7、8、13、14、17、18的状况.锁存端LE由高变低时,输出端8位信息被锁存,直到LE端再次有用。

当三态门使能信号OE为低电往常,三态门导通,容许Q0~Q7输出,OE为高电往常,输出悬空。

当74LS373用作地址锁存器时,应使OE为低电平,此刻锁存使能端C为高电往常,输出Q0~Q7状况与输入端D1~D7状况一样;当C发作负的跳变时,输入端D0~D7数据锁入Q0~Q7。

51单片机的ALE信号能够直接与74LS373的C联接。

1D~8D为8个输入端。

1Q~8Q为8个输出端。

G是数据锁存操控端;当G=1时,锁存器输出端同输入端;当G由1变为0时,数据输入锁存器中。

OE为输出容许端;当OE=0时,三态门翻开;当OE=1时,三态门封闭,输出呈高阻状况。

在MCS-51单片机体系中,常选用74LS373作为地址锁存器运用,其联接办法如上图所示。

其间输入端1D~8D接至单片机的P0口,输出端供给的是低8位地址,G端接至单片机的地址锁存容许信号ALE。

输出容许端OE接地,标明输出三态门一向翻开。

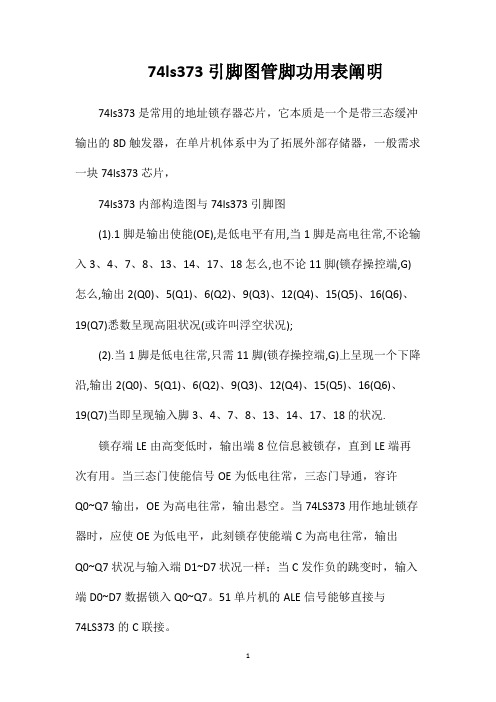

74ls373引脚图管脚功能表

74ls373引脚图管脚功能表74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片,(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);(2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。

当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。

51单片机的ALE信号可以直接与74LS373的C连接。

74ls373与单片机接口:1D~8D为8个输入端。

1Q~8Q为8个输出端。

G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。

OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。

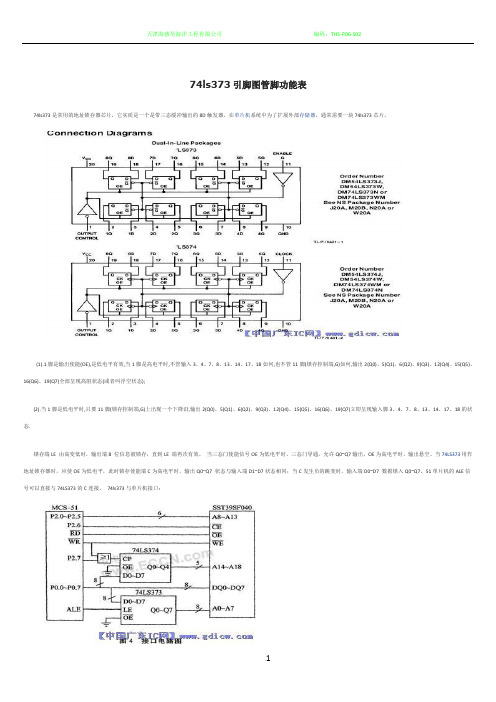

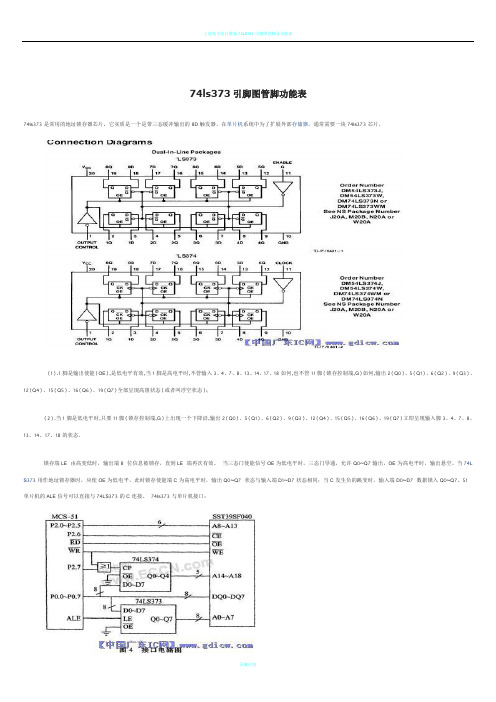

在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。

其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。

输出允许端OE接地,表示输出三态门一直打开。

74ls373引脚图管脚功能表

74ls373引脚图管脚功能表之马矢奏春创作74ls373是经常使用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片,(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);(2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q 0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。

当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7数据锁入Q0~Q7。

51单片机的ALE信号可以直接与74LS373的C连接。

74ls373与单片机接口:1D~8D为8个输入端。

1Q~8Q为8个输出端。

G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变成“0”时,数据输入锁存器中。

OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。

在MCS-51单片机系统中,常采取74LS373作为地址锁存器使用,其连接方法如上图所示。

其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G 端接至单片机的地址锁存允许信号ALE。

输出允许端OE接地,暗示输出三态门一直打开。

74ls373引脚图管脚功能表

74ls373引脚图管脚功效表74ls373是经常应用的地址锁存器芯片,它本质是一个是带三态缓冲输出的8D触发器,在单片机体系中为了扩大外部存储器,平日须要一块74ls373芯片,(1).1脚是输出使能(OE),是低电平有用,当1脚是高电日常平凡,不管输入3.4. 7.8.13.14.17.18若何,也不管11脚(锁存掌握端,G)若何,输出2(Q0).5(Q1).6(Q2).9 (Q3).12(Q4).15(Q5).16(Q6).19(Q7)全体呈现高阻状况(或者叫浮空状况);(2).当1脚是低电日常平凡,只要11脚(锁存掌握端,G)上消失一个降低沿,输出2 (Q0).5(Q1).6(Q2).9(Q3).12(Q4).15(Q5).16(Q6).19(Q7)立刻呈现输入脚3.4.7.8.1 3.14.17.18的状况.锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有用. 当三态门使能旌旗灯号OE为低电日常平凡,三态门导通,许可Q0~Q7输出,OE为高电日常平凡,输出悬空.当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电日常平凡,输出Q0~Q7 状况与输入端D1~D7状况雷同;当C产生负的跳变时,输入端D0 ~D7 数据锁入Q0~Q7.51单片机的ALE旌旗灯号可以直接与74LS373的C衔接. 74ls3 73与单片机接口:1D~8D为8个输入端.1Q~8Q为8个输出端.G是数据锁存掌握端;当G=1时,锁存器输出端同输入端;当G由“1”变成“0”时,数据输入锁存器中.OE为输出许可端;当OE=“0”时,三态门打开;当OE=“1”时,三态门封闭,输出呈高阻状况.在MCS-51单片机体系中,常采取74LS373作为地址锁存器应用,其衔接办法如上图所示.个中输入端1D~8D接至单片机的P0口,输出端供给的是低8位地址,G端接至单片机的地址锁存许可旌旗灯号ALE.输出许可端OE接地,暗示输出三态门一向打开。

74ls373中文资料

PD

m

54S373/74S373

7ns

54LS373/74LS373

17ns

525mW 120mW

r

a 373 的输出端 O0~O7 可直接与总线相连。

当三态允许控制端 OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总

- 线。当 OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但

单位

VIK输入嵌位电压

VOH输出高电平电压

VOL输出低电平电压 II最大输入电压时输入

电流 IIL输入低电平电流 IIH输入高电平电流

Vcc=最小,Iik=-18mA

Vcc=最小,VIL=最大, VIH=2V,IOH=最大

Vcc=最小,VIL=最大, 54

VIH=2V,IOL=最大

74

Vcc=最大

VI=5.5V VI=7V

54LS373/74LS373 最小 额定 最大

单位

电源电压 Vcc

54 4.5

5

74 4.75

5

输入高电平电压ViH

2

输入低电平电压ViL

54 74

5.5

4.5

5

5.5

5.25 4.75

5

5.25

V

2

V

0.8 0.8

0.7 0.8

V

输出高电平电流IOH

54 74

-2

-1

mA

-6.5

-2.6

输出低电平电流IOL

. 输出高阻态时高电平电压 ………………………….

工作环境温度

w 54XXX

………………………………….

74XXX

………………………………….

74573资料

74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制1. 真值表参见74LS373的PDF的第2页:Dn LE OE OnH H L HL H L LX L L QoX X H Z这个就是真值表,表示这个芯片在输入和其它的情况下的输出情况。

每个芯片的数据手册(datasheet)中都有真值表。

布尔逻辑比较简单,在此不赘述;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁;高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力。

74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

OE:output_enable,输出使能;LE:latch_enable,数据锁存使能,latch是锁存的意思;Dn:第n路输入数据;On:第n路输出数据;再看这个真值表,意思如下:第四行:当OE=1是,无论Dn、LE为何,输出端为高阻态;第三行:当OE=0、LE=0时,输出端保持不变;第二行第一行:当OE=0、LE=1时,输出端数据等于输入端数据;结合下面的波形图,在实际应用的时候是这样做的:a.OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:mov P0,A ;将数据输出到并行数据端口clr LEsetb LEclr LE ;上面三条指令完成LE的波形从0->1->0的变化74ls573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端182回答者:a33090997a - 一级。

74ls373引脚图管脚功能表

74ls373引脚图管脚功能表74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片,(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);(2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。

当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

当74L S373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。

51单片机的ALE信号可以直接与74LS373的C连接。

74ls373与单片机接口:1D~8D为8个输入端。

1Q~8Q为8个输出端。

G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。

OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。

在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。

其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。

输出允许端OE接地,表示输出三态门一直打开。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74LS373 引脚图、内部结构、参数、典型应用电路

【功能简介】

74LS373是一款常用的地址锁存器芯片,由八个并行的、带三态缓冲输出的D触发器构成。

在单片机系统中为了扩展外部存储器,通常需要一块74LS373芯片。

本文将介绍74LS373的工作原理,内容涵盖引脚图、内部结构、主要参数以及在单片机扩展系统中的典型应用电路。

【内部逻辑结构图】

74LS373地址锁存器的内部逻辑结构如图一所示。

图1

【74LS373的真值表(功能表)】

G—与8031/8051的ALE相连,控制八个D型锁存器的导通与截止:高电平时,八个D型锁存器正常运行(导通),即锁存器的输出端

与输入端D的反相信号始终同步;低电平时锁存器截止,D锁存器输出

端的状态保持不变。

OE(Output Enable = Output Control)—使能端,接地时锁存

【74LS373引脚排列图】

【74LS373电气参数】

拖动图片放大!

74ls373推荐工作条件

【74LS373在单片机扩展系统中的典型应用电路】

当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端G为高电平时,输出Q0-Q7的状态与输入端D1-D7状态相同;当G发生负的跳变时,输入端D0-D7 数据锁入Q0-Q7。

51单片机的ALE信号可以直接与74LS373的G 连接。

在MCS-51单片机系统中,其连接方法如下图所示。

其中输入端1D-8D接

至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允

许信号ALE。

输出允许端OE接地,表示三态输出门一直导通,可以送出地址信

号。

1D-8D为8个输入端。

1Q-8Q为8个输出端。

【说明】基础比较好的同学请直接忽略。

G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。

OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。

(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);

(2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.

锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。

当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。