DMA模块详解

stm32_DMA知识总结

stm32_DMA知识总结DMA实验现象:通过DMA通道将一个1万个数据数组内容向USART1传送.按下UP键触发传送.一.概述DMA直接存储存取.数据传送时无须CPU干扰.二.STM32 DMA特性1.有两个DMA模块 DMA1,DMA2.2.共有12个通道.DMA1 7个. DMA2 5个.3.传输双方可以是: SRAM ,闪存,外设之间.4.传输宽度可变:字节,半字(2B),全字(4B). 最大数目是65535.5.有三个传输事件:半传输,传输完成,传输出错.三.DMA通道分布148页 DMA1149页 DMA2四.相关寄存器(149页)1.中断状态寄存器 DMA_ISR,只读1个通道占4bit.以通道1为例:[0]通道1全局中断标志,以下三种事件的相或.[1]通道1传输完成标志[2]通道1半传输标志[3]通道1传输错误标志[4,5,6,7]通道2相关2.中断标志清除 DMA_IFCR(150页)写1清除上面状态寄存器对应标志位.3.通道配置寄存器1 DMA_CCR1...通道配置寄存器7 DMA_CCR74.传输数量寄存器1 DMA_CNDTR1 ...传输数量寄存器7 DMA_CNDTR75.外设地址寄存器1 DMA_CPAR1...外设地址寄存器7 DMA_CPAR76.存储器地址寄存器1 DMA_CMAR1 ...存储器地址寄存器7 DMA_CMAR7五.示例代码分析将内存中1万个数据发送到USART1->DR.传输进行,统计进度,闪灯.表明CPU没有独占.补充1)源寄存器,目标寄存器 ()2)传输方向 CCR3)传输协议 CCR4)启动DMA CCRCNDTR寄存器必须写入数据,总共搬运多少个字节。

写入值为0的话,即使启动DMA,DMA也不工作CPAR: 串口数据地址,&UASRT->DR,地址加偏移量DMA是一个不需要CPU干预的独立硬件模块,可以进行。

DMA

1. DMA(Direct Memory Access)的概念 Access)的概念 • DMA方式不用处理器干预完成M与I/O间数据传 DMA方式不用处理器干预完成M I/O间数据传 方式不用处理器干预完成 送。 • DMA期间系统总线由其它主模块控制(驱动) DMA期间系统总线由其它主模块控制 驱动) 期间系统总线由其它主模块控制( • 控制总线的主模块要提供系统的地址及控制 信号。 信号。 • DMA控制器与处理器配合可实现系统的DMA功 DMA控制器与处理器配合可实现系统的DMA功 控制器与处理器配合可实现系统的DMA 能。

CPU响应 响应DMA放弃总线 响应 放弃总线

DMAC 控制传一个字节 Y

DMA请求? 请求? 请求 N 放总线

块结束否? 块结束否? Y 放总线中断请求

随机请求 DEMAND REQUEST

HOLD HLDA CLOCK 关闭CPU地址锁存器

HRQ

控制 REG. 8 Addr.Temp.16 Count Temp. 16 暂存器 8

DMAC发出 DMAC发出 控制信号

․DMA传送方式 DMA 请求?

Y

DMAC发BUS请求 发 请求 CPU响应 响应DMA 响应 放弃BUS 放弃 DMAC控制 控制 传一个字节 块结束否? 块结束否?

Y N

DMA 放 总 线

放弃总线中断请求 字节传送

․DMA传送方式 DMA传送方式

DMA与DMA控制器(续)

3.Intel 8237A可编程DMA控制器框图(续) 8237A可编程DMA控制器框图( 可编程DMA控制器框图 • 8237A引线说明: 8237A引线说明 引线说明: DB7-DB0:双向数据总线。 DB7-DB0:双向数据总线。 8237A为从模块时被处理器编程或读状态 为从模块时被处理器编程或读状态, 8237A为从模块时被处理器编程或读状态, DB7-DB0作为数据线 传输数据或命令字。 作为数据线, DB7-DB0作为数据线,传输数据或命令字。 8237A为主模块时DB7-DB0输出地址A15-A8, 为主模块时DB7 输出地址A15 8237A为主模块时DB7-DB0输出地址A15-A8,在 M传送操作时经DB7-DB0, 传送操作时经DB7 M M传送操作时经DB7-DB0,将M数据送 8237A暂存器 暂存器。 8237A暂存器。 A3-A4:地址线,从模块时为输入, A3-A4:地址线,从模块时为输入,处理器寻 8237A;主模块时输出低压位地址。 址8237A;主模块时输出低压位地址。

gd32f4的dma的fifo用法

GD32F4是一款性能强大的微控制器,其DMA(直接内存存取)模块具有FIFO(先进先出)功能,可以很好地优化数据传输。

本文将深入介绍GD32F4的DMA的FIFO用法,帮助读者更好地了解和使用这一功能。

一、GD32F4的DMA概述GD32F4是一款由国内厂商研发的微控制器,采用Cortex-M4内核,具有丰富的外设和强大的性能。

其中的DMA模块可以实现在外设和内存之间的数据传输,提高系统的效率和性能。

GD32F4的DMA模块还支持FIFO功能,能够进一步优化数据传输的效率。

二、DMA的FIFO原理DMA的FIFO是一种数据缓冲机制,用于临时存储数据,从而实现数据的流水线传输。

在GD32F4中,DMA的FIFO可以有效减少CPU 的负担,提高系统整体的并行处理能力。

具体原理如下:1. 数据输入:当外设向DMA模块发送数据时,数据首先被存储在FIFO中,等待DMA的处理。

2. 数据传输:DMA按照一定的规则从FIFO中取出数据,并将其传输到内存或其他外设中。

3. 数据输出:传输完成后,数据可以从FIFO中输出,供其他模块或外设使用。

三、DMA的FIFO用法为了更好地使用GD32F4的DMA的FIFO功能,我们需要了解其具体的用法和配置方法:1. FIFO的配置:在使用DMA功能之前,需要对DMA的FIFO进行合适的配置,包括FIFO的大小、读写指针的设置等。

2. 数据传输:通过配置DMA的传输模式、外设位置区域、内存位置区域等参数,可以实现不同类型的数据传输,如单次传输、循环传输等。

3. 中断处理:DMA在数据传输完成或发生错误时会产生中断,可以通过中断处理函数来处理这些事件,保证数据的完整性和正确性。

四、实例分析为了更好地理解GD32F4的DMA的FIFO用法,我们以SPI(串行外设接口)的数据传输为例进行分析:1. 配置SPI和DMA:首先需要配置SPI接口和DMA模块,包括时钟使能、引脚配置、传输模式设置等。

直接存储器存取(DirectMemoryAccess,DMA)详细讲解

直接存储器存取(DirectMemoryAccess,DMA)详细讲解⼀、理论理解部分。

1、直接存储器存取(DMA)⽤来提供在外设和存储器之间或者存储器和存储器之间的⾼速数据传输。

2、⽆须CPU⼲预,数据可以通过DMA快速移动,这就节省了CPU的资源来做其他操作。

3、两个DMA控制器有12个通道(DMA1有7个通道,DMA2有5个通道),每个通道专门⽤来管理来⾃⼀个或者多个外设对存储器访问的请求。

4、还有⼀个冲裁器协调各个DMA请求的优先权。

在同⼀个DMA模块上,多个请求间的优先权可以通过软件编程设置(共有四级:很⾼、⾼、中和低),优先权设置相等时由硬件决定(请求0优先请求1,)5、每个通道都有三个事件标志(DMA半传输、DMA传输完成和DMA传输出错),这三个事件标志逻辑或成为⼀个单独的中断请求。

6、闪存、SRAM、外设的SRAM、APB1、APB2和AHB外设均可作为访问的源和⽬标。

7、可编程的数据传输数⽬:最⼤为655358、如果外设要想通过DMA 来传输数据,必须先给DMA 控制器发送DMA 请求,DMA 收到请求信号之后,控制器会给外设⼀个应答信号,当外设应答后且DMA 控制器收到应答信号之后,就会启动DMA 的传输,直到传输完毕。

DMA 有DMA1 和DMA2 两个控制器,DMA1 有7个通道,DMA2有5 个通道,不同的DMA 控制器的通道对应着不同的外设请求,这决定了我们在软件编程上该怎么设置,具体见DMA 请求映像表。

9、仲裁器当发⽣多个DMA 通道请求时,就意味着有先后响应处理的顺序问题,这个就由仲裁器也管理。

仲裁器管理DMA 通道请求分为两个阶段。

第⼀阶段属于软件阶段,可以在DMA_CCRx 寄存器中设置,有4 个等级:⾮常⾼、⾼、中和低四个优先级。

第⼆阶段属于硬件阶段,如果两个或以上的DMA通道请求设置的优先级⼀样,则他们优先级取决于通道编号,编号越低优先权越⾼,⽐如通道0 ⾼于通道1。

全志A20_DMA开发说明文档_V1.0_20130315

C on f i d e n t i al A20DMA 开发说明V1.02013-03-15C on f i d e n t ia l Revision HistoryVersionDate Changes compared to previous issue v1.02013-03-15初建版本C o n f i d e n t i al 目录1.概述-------------------------------------------------------------------------------------------------------51.1.编写目的----------------------------------------------------------------------------------------51.2.适用范围----------------------------------------------------------------------------------------51.3.相关人员----------------------------------------------------------------------------------------52.模块介绍-------------------------------------------------------------------------------------------------62.1.模块功能介绍----------------------------------------------------------------------------------62.2.相关术语介绍----------------------------------------------------------------------------------62.2.1.DMA--------------------------------------------------------------------------------------62.2.2.描述符(des)-----------------------------------------------------------------------------62.2.3.散列传输--------------------------------------------------------------------------------62.3.模块配置介绍----------------------------------------------------------------------------------62.4.源码结构介绍----------------------------------------------------------------------------------63.模块体系结构描述------------------------------------------------------------------------------------73.1.DMA 驱动架构图------------------------------------------------------------------------------73.2.DMA 软件状态---------------------------------------------------------------------------------74.模块数据结构描述------------------------------------------------------------------------------------94.1.dma_channel_t-----------------------------------------------------------------------------------94.2.cofig_des_t---------------------------------------------------------------------------------------94.3.des_item-----------------------------------------------------------------------------------------104.4.chan_state_e------------------------------------------------------------------------------------104.5.dma_cb_t----------------------------------------------------------------------------------------104.6.dma_op_type_e--------------------------------------------------------------------------------105.模块接口描述-----------------------------------------------------------------------------------------125.1.sw_dma_request-------------------------------------------------------------------------------125.2.sw_dma_release--------------------------------------------------------------------------------125.3.sw_dma_ctl-------------------------------------------------------------------------------------125.4.sw_dma_config--------------------------------------------------------------------------------135.5.sw_dma_enqueue------------------------------------------------------------------------------135.6.sw_dma_getposition---------------------------------------------------------------------------145.7.sw_dma_dump_chan--------------------------------------------------------------------------146.模块开发DEMO-------------------------------------------------------------------------------------156.1.DMA 使用流程图-----------------------------------------------------------------------------156.2.demo 程序--------------------------------------------------------------------------------------156.2.1.test_case_normal.c--------------------------------------------------------------------156.2.2.test_case_normal.h--------------------------------------------------------------------236.2.3.sun7i_dma_test.h----------------------------------------------------------------------246.2.4.sun7i_dma_test.c----------------------------------------------------------------------257.Android 系统支持-------------------------------------------------------------------------------------318.模块调试-----------------------------------------------------------------------------------------------328.1.menuconfig 的配置---------------------------------------------------------------------------32C on f i d e n t i al 8.2.测试用例选择---------------------------------------------------------------------------------328.3.测试操作步骤---------------------------------------------------------------------------------339.总结-----------------------------------------------------------------------------------------------------3410.Declaration--------------------------------------------------------------------------------------------35C on f i d e n t i al 1.概述1.1.编写目的介绍DMA 模块使用方法。

adc dma 回调函数

adc dma 回调函数ADC和DMA是嵌入式系统中常用的两个模块,它们在数据采集和传输过程中起着重要的作用。

而回调函数是用来处理异步事件的一种机制。

本文将围绕着ADC、DMA和回调函数展开,详细介绍它们的原理和应用。

我们来了解一下ADC(Analog-to-Digital Converter)模块。

ADC 是一种将模拟信号转换为数字信号的电路,常用于嵌入式系统中对模拟量的采集。

在嵌入式系统中,ADC通常连接着各种传感器,用于采集温度、光照、压力等模拟量信号。

ADC的工作原理是将模拟信号通过采样和量化的方式转换为数字信号,然后再经过处理和分析得到需要的信息。

接下来,我们来介绍DMA(Direct Memory Access)模块。

DMA是一种无需CPU干预就能进行数据传输的技术。

在传统的数据传输方式中,数据需要经过CPU的中转,才能从外设传输到内存或者从内存传输到外设。

而DMA的出现,使得数据传输可以直接在外设和内存之间进行,大大提高了数据传输的效率和速度。

DMA模块中有多个通道,可以同时处理多个数据传输请求,从而实现并行传输。

ADC和DMA常常结合使用,以实现高效的数据采集和传输。

ADC采集的数据可以直接通过DMA传输到内存,而不需要CPU的干预。

这样可以减少CPU的负担,提高系统的响应速度。

在这个过程中,回调函数起到了关键的作用。

回调函数是一种异步事件处理的机制。

在ADC和DMA的数据传输过程中,当数据传输完成或者出现错误时,会触发相应的中断事件。

此时,系统会调用预先注册的回调函数来处理这些事件。

回调函数可以根据具体的需求,进行数据处理、错误处理或者其他操作。

通过回调函数的灵活应用,可以实现更加复杂和高效的系统功能。

在使用ADC和DMA的过程中,编写回调函数需要注意一些细节。

首先,回调函数应该尽量简洁和高效,避免耗费过多的系统资源。

其次,回调函数应该及时处理事件,以免影响系统的实时性。

此外,回调函数还需要考虑异常情况的处理,例如数据溢出、传输错误等。

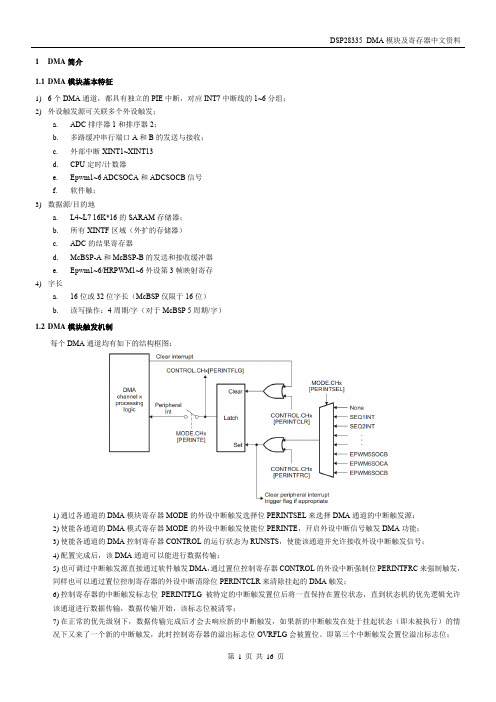

DSP28335 DMA模块及寄存器中文资料

1DMA简介1.1DMA模块基本特征1)6个DMA通道,都具有独立的PIE中断,对应INT7中断线的1~6分组;2)外设触发源可关联多个外设触发;a.ADC排序器1和排序器2;b.多路缓冲串行端口A和B的发送与接收;c.外部中断XINT1~XINT13d.CPU定时/计数器e.Epwm1~6 ADCSOCA和ADCSOCB信号f.软件触;3)数据源/目的地a.L4~L7 16K*16的SARAM存储器;b.所有XINTF区域(外扩的存储器)c.ADC的结果寄存器d.McBSP-A和McBSP-B的发送和接收缓冲器e.Epwm1~6/HRPWM1~6外设第3帧映射寄存4)字长a.16位或32位字长(McBSP仅限于16位)b.读写操作:4周期/字(对于McBSP 5周期/字)1.2DMA模块触发机制每个DMA通道均有如下的结构框图:1)通过各通道的DMA模块寄存器MODE的外设中断触发选择位PERINTSEL来选择DMA通道的中断触发源;2)使能各通道的DMA模式寄存器MODE的外设中断触发使能位PERINTE,开启外设中断信号触发DMA功能;3)使能各通道的DMA控制寄存器CONTROL的运行状态为RUNSTS,使能该通道并允许接收外设中断触发信号;4)配置完成后,该DMA通道可以能进行数据传输;5)也可调过中断触发源直接通过软件触发DMA,通过置位控制寄存器CONTROL的外设中断强制位PERINTFRC来强制触发,同样也可以通过置位控制寄存器的外设中断清除位PERINTCLR来清除挂起的DMA触发;6)控制寄存器的中断触发标志位PERINTFLG被特定的中断触发置位后将一直保持在置位状态,直到状态机的优先逻辑允许该通道进行数据传输,数据传输开始,该标志位被清零;7)在正常的优先级别下,数据传输完成后才会去响应新的中断触发,如果新的中断触发在处于挂起状态(即未被执行)的情况下又来了一个新的中断触发,此时控制寄存器的溢出标志位OVRFLG会被置位。

DMA14-4850Ⅱ整流模块

DMA14-48/50Ⅱ整流模块简介 DMA14-48/50Ⅱ整流模块简介

可构成的电源系统容量从50A到 到 可构成的电源系统容量从 600A,目前所构成的典型系统为 , DUM23Ⅵ型的组合电源系统 Ⅵ DMA14-48/50Ⅱ型整流模块可与监 Ⅱ 控单元进行数据通信,也可根据需要, 控单元进行数据通信,也可根据需要, 通过调制解调器( 通过调制解调器(MODEM)来实现 ) 对整流模块的远端监控 安装条件也十分灵活,只由一个维 安装条件也十分灵活,只由一个维 一个 护人员进行操作即可实现整流模块的 更换

噪音 :<55dB(A)

DMA14-48/50Ⅱ整流模块的组成 DMA14-48/50Ⅱ整流模块的组成

DMA14整流模块由四块印制板组成 DMA14整流模块由四块印制板组成 : 功率主板(PMB25) 功率主板(PMB25) 控制回路板(CLC) 控制回路板(CLC) 数字次级控制板(DSCC) 数字次级控制板(DSCC) 前面板(FP25A) 前面板(FP25A)

光耦隔离 数字次级控制板 在模块与监控之间有二个光耦: DMA14整流模块中又三个光耦 整流模块中又三个光耦: 在模块与监控之间有二个光耦 : 在DMA14数字次级控制板离 : 因为电压和限流回路的反馈信号是从输出电路 整流模块中又三个光耦 光耦 前面显示板隔 并通过数字 有次级电压和电流反馈回路, 监控整流模块的多项功能, 有次级电压和电流反馈回路,用于设置 监控整流模块的多项功能关控制信号光耦 上获得,这样在输出级(次级) 1.数字通信 DSCC板 ,为正激变换器提供电 3.从CLC板到 控制回路板 2.数字化的整流模块开 1.功率控制为线形光耦/ , 数字化的整流模块开/ 板到DSCC 上获得,这样在输出级(次级)电路与初级控制 1.数字通信 DSCC板,用于表明初级电路有没 3.功率控制为线形光耦, 2.功率控制为线形光耦 从CLC板到 数字化的整流模块开 通常输出的正端或负端应与系 它装在整流模块塑料罩板内, 、电压控制 它包括微处理器及存储器电路、 它装在整流模块塑料罩板内,由三个状态显示 它包括微处理器及存储器电路

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

//北京联合大学实训基地潘峰//qq:66797490//微博:潘峰_buu//博客:/panpan_0315/blog/DMA模块DMA模块简介所谓DMA就是直接内存存取(Direct Memory Access),是计算机科学中的一种内存访问技术。

以前我们向内存传送数据,都是通过CPU来进行。

比如AD完成后,我们要把结果寄存器中的值传送到内存的一个变量中,一种方法就是查询COCO标志位(详见ADC模块一节),一旦置1,就读取结果寄存器并传送。

这种方法CPU需要不断查询标志位,耽误时间,降低效率。

我们也可以使用中断的方式,CPU并不需要轮询标志位,而是AD转换完成后触发中断,CPU中断当前的程序,转向执行中断服务程序,在中断服务程序中读取结果寄存器,然后传送到内存中。

这种方式虽然省去了轮询的时间消耗,但传送数据仍然是由CPU完成的,如果是大批量数据高速传输的话,频繁的中断也将造成很重的CPU负担,于是就有了DMA。

和轮询方式、中断方式不同的是,DMA是通过DMA控制器接管数据和地址总线,根据事先设定好的源地址和目的地址,以及传送的字节数,将数据自动传送到指定的位置,而不需要CPU的介入,从而CPU的负担大大减轻。

如果CPU正在执行指令,DMA控制利用空闲的地址和数据总线完成数据传送,某种程度上说,CPU运算和数据传送是在并行进行的。

在制作智能车的应用中,摄像头组的同学,需要将摄像头采集的数据用最快的速度传送到内存变量中,以采集更多的点。

Kinetis芯片的DMA功能这个时候就能发挥重要的作用了。

首先我们需要了解一下和Kinetis芯片的DMA功能有关的一些概念。

1.DMA源和DMA通道在Kinetis芯片中,很多模块都可以请求DMA模块进行数据传送。

所谓DMA源,也就是DMA传送请求是谁发出的。

以K60DN512Z为例,共有63个DMA源。

而DMA源发出的DMA请求并不是直接提交到DMA控制器,而是通过DMA多路复用器的16个DMA通道提交的。

需要设置相关的寄存器建立DMA源和DMA通道之间的映射关系。

如图错误!文档中没有指定样式的文字。

-1所示。

图错误!文档中没有指定样式的文字。

-1 DMA多路复用器2.DMA模块框图DMA控制模块分为两部分,一个是DMA引擎(eDMA Engine)。

一个是DMA传输控制描述符(TCD),如图错误!文档中没有指定样式的文字。

-2所示。

图错误!文档中没有指定样式的文字。

-2 DMA控制框图3.DMA描述符每个通道需要一个32个字节的传输控制描述符用于定义我们想要的数据传送操作。

描述符按通道0~通道15的顺序依次存放在DMA模块的内存中。

描述符中包含了对应的数据传送的所有信息,主要有源地址,目的地址,传送次数,每次传送的字节数,传送完毕后源地址和目的地址如何调整等等,当一个通道的DMA传送结束后,源地址和目的地址需要加上各自的调整量回写到TCD中,传送计数也需要重新初始化并回写到TCD中。

如表错误!4.主循环和副循环数据的传送分为主循环(major loop)和副循环(minor loop)。

如何理解这两个概念呢。

我们不妨假设用软件来实现有规律的顺序数据传送,使用C语言来实现的话,可以用for循环。

好比用两层嵌套的for循环来实现。

如使用DMA做同样的工作,过程是相同的,外层的循环又称主循环,即major loop。

内层循环称为副循环,即minor loop。

major loop 循环一次,可能需要minor loop循环多次。

每个minor loop循环都需要DMA源发来请求或者通过软件请求。

每个minor loop传送完毕,对应的DMA通道就进入空闲模式,等待下一次DMA 请求。

当所有DMA传送完毕,即置DONE标志,并且可以通过设置选择传送完毕是否触发中断。

5.主/副循环链接功能Kinetis的DMA模块有个功能叫主/副循环链接,就是当一个通道的主循环(Major loop)或副循环(minor loop)结束后,自动链接到另一个通道进行传输。

比如你可以用通道0传送AD数据到内存,完毕后,立刻链接到通道1将内存中的数再传送到DAC。

如果要使用这个功能,需要设置DMA_TCDn_CSR寄存器或DMA_TCD_CITER寄存器。

6.散/聚模式Kinetis的DMA模块还有个特殊的功能叫散/聚模式(Scatter/Gather)。

在这个模式下,当一个通道的主循环(major loop)传输结束后,由一个指针指向一个内存中的新的传输控制描述符(TCD)的起始地址,DMA控制器将从内存中载入该描述符。

这种应用可用在分散存储的内存应用中。

多个需要传送的数据块没有按地址连续存放,而是分散存储在内存的不同位置时,可采用这种方式。

如果要使用这个功能,需要设置DMA_TCDn_CSR寄存器。

7.副循环映射前面提到,数据的传送分为主循环(major loop)和副循环(minor loop)。

一般情况下,每传送一次指定宽度的数据,源地址和目的地址都会加上一个设定好的偏移量,直到这次副循环传送的字节数全部完成,等待下一次DMA请求。

当下一次请求到来时,下一次副循环开始传送,访问的源地址或目的地址和上一次都是连续的,如果不希望连续,而是跳过若干字节,可启用副循环映射,并设定好源地址或目的地址的偏移量。

相关寄存器1.DMA控制寄存器(DMA_CR)●CX:取消传输。

向该位写1将取消当前的传送。

CX=0:普通操作模式;CX=1:取消剩下的传送,该位在取消操作完成后自动清0。

●ECX:错误取消传送。

ECX=0:普通操作模式;ECX=1:和CX作用相同,但是ECX置位会被视为DMA错误,相关的错误寄存器会置位且可能引发错误中断。

●EMLM:使能副循环映射。

在传输控制描述符中有一个字段NBYTE,当EMLM=0和EMLM=1时,该字段的内容有不同的含义,详细参见DMA_TCD_NBYTES寄存器介绍。

EMLM=0:禁止副循环映射;EMLM=1:使能副循环映射。

●CLM:连续链接模式。

CLM=0:当一个副循环(minor loop)结束后,在再次被激活之前,还必须通过通道裁决;CLM=1:当一个副循环(minor loop)结束后,在再次被激活之前,不需要通过通道裁决。

●HALT:停止DMA操作。

HALT=0:普通操作模式;HALT=1:停止任何新通道的启动,正在执行的通道可继续执行到结束。

直到该位清0,各通道方可恢复正常。

●HOE:错误停止,该位置位时,一旦发生DMA传送错误则会将HALT置位。

HOE=0:正常模式;HOE=1:任何错误都会造成HALT位置位,所有服务请求被忽略直到HALT被清除。

●ECRE:使能循环通道裁决。

所谓裁决就是当多个通道优先级判断,通过设置ECRE可选择不同的判断方法。

ECRE=0:固定优先级的通道裁决方法;ECRE=1:使用循环通道裁决方法,即从最高的通道号到最低的通道号依次响应DMA 请求而不考虑其优先级。

●EDBG:使能调试。

EDBG=0:在调试模式下,DMA继续运行;EDBG=1:调试模式下,新通道的启动被停止。

正在运行的通道可继续执行到结束。

各通道直到系统退出调试状态或EDBG位被清0时恢复。

2.错误状态寄存器(DMA_ES)该寄存器用于报告通道错误,该寄存器反映的错误是来自上一次DMA请求并记录的DMA传送造成的。

通道错误由以下因素造成:●设置错误,传输控制描述符TCD的非法设置或在固定优先级裁决中设置了非法的优先级;●在总线控制器读写周期中出现了非法终止。

●VLD:所有错误状态位的逻辑或。

该寄存器中其它任何一个错误位置1,该位都会置1。

VLD=0:没有任何错误发生;VLD=1:至少一个错误位被置位。

●ECX:传输取消。

ECX=0:没有被取消的传输;ECX=1:上一个登记的入口是一个被错误传输输入取消的传输。

●CPE:通道优先级错误。

CPE=0:没有通道优先级错误;CPE=1:上一个登记的错误是优先级配置错误,优先级的设置不唯一。

●ERRCHN:错误的通道号或被取消的通道号。

●SAE:源地址错误。

SAE=0:无源地址错误;SAE=1:源地址错误。

TCDn_SADDR域和TCDn_ATTR[SSIZE]不一致。

●SOE:源偏移量错误。

SOE:=0:无源偏移量错误;SOE=1:源偏移量错误,TCDn_SOFF域和TCDn_ATTR[SSIZE]不一致。

●DAE:目的地址错误。

DAE=0:无目的地址错误;DAE=1:最后登记的错误是目的地址错误。

即TCDn_DADDR域和TCDn_ATTR[SSIZE]不一致。

●DOE:目的地址偏移量错误。

DOE=0:无目的地址偏移量错误;DOE=1:目的地址偏移量错误,TCDn_DOFF域和TCDn_ATTR[SSIZE]不一致。

●NCE:NBYTES/CITER 设置错误。

NCE=0:没有NBYTES/CITER 设置错误;NCE=1:NBYTES/CITER错误。

TCDn_NBYTES不是TCDn_ATTR[SSIZE] 和TCDn_ATTR[DSIZE]的倍数;TCDn_CITER[CITER]设为0;TCDn_CITER[ELINK]和TCDn_BITER[ELINK]不相等。

●SGE:散/聚模式(Scatter/Gather)错误。

SGE=0:无散/聚模式设置错误;SGE=1:散/聚模式设置错误。

●SBE:源总线错误。

SBE=0:无源总线错误;SBE=1:最后一个被记录的错误是读取源地址时发生的总线错误。

●DBE:目的总线错误。

3.DMA请求使能寄存器(DMA_ERQ)●ERQn:使能通道n的DMA请求。

ERQn=0:通道n的DMA请求信号被禁止;ERQn=1:通道n的DMA请求信号被使能。

注意:在硬件DMA请求到达之前,对应位必须置1,但软件DMA请求和链接通道的DMA请求不受该位影响。

4.DMA错误中断使能寄存器(DMA_EEI)●EEIn:通道n的错误中断使能。

EEIn=0:通道n的错误中断被禁止;EEIn=1:通道n的错误中断被使能。

5.中断请求寄存器(DMA_INT)●INTn:中断请求n。

INTn=0:对应通道无中断请求;INTn=1:对应通道发出中断请求。

6.错误寄存器(DMA_ERR)●ERRn:通道n错误。

ERRn=0:对应通道没有出现错误;ERRn=1:对应通道出现错误。

7.硬件请求状态寄存器(DMA_HRS)●HRSn:通道n硬件请求。

HRSn=0:对应通道未出现硬件服务请求;HRSn=1:对应通道出现硬件服务请求。

8.通道n优先级寄存器(DMA_DCHPRIn)所谓优先级裁决,即当有多个DMA通道发出DMA请求时,如何决定响应的先后顺序?或有新的DMA请求到达,而当前的DAM传送还未完成,如何处理?这跟中断优先级的判断是一个道理。