一款发烧DAC音频解码器的设计与制作

用PCM1738制作小巧的音频解码器.doc

用PCM1738制作小巧的音频解码器玩音响的发烧友们估计都深有体会,一款优秀的解码器,可以很大程度地提高音响系统的还原水平。

笔者也喜欢音频解码器的制作,并经常和网络论坛里的发烧友交流心得。

部分动手派的发烧友希望能拥有一款线路简单、易做,成本不高,又特别适合手工焊接的解码器。

因此,萌发了设计一款小巧简单的高素质解码器的念头。

结合音响艺苑周年系列解码器的设计理念和制作经验,决定采用BB 公司出品的高性能数字接收芯片—DIR9001,以及同样是BB公司的解码芯片—PCM1738,作为该音频解码器的主要芯片。

PCB 经过反复的排版优化,最终尺寸只有10cm×7cm大小。

除了主要的3个IC芯片是贴片元件,其他均采用直插元件,特别适合手工焊接。

别看PCB尺寸小,却包含了100多个元件,并且拥有了SPDIF同轴和光纤输入,适合驳接CD,DVD,电脑声卡等。

由于尺寸小巧,可以将解码板整合到CD机内,更加节省空间,也可以另外购买市面上常见的铝型材外壳,装成一台解码器整机。

下面我们先来看看主要芯片的基本资料吧。

DIR9001是28针TSSOP封装的,可接收24bit(28 ~108kHz)采样率的数字接收芯片。

它有极低的抖动(jitter),支持标准的SPDIF、AES等多种信号输入方式。

可选择的多种系统时钟::128f s,256f s,384f s以及512f s (f s为输入数字信号采样率),并支持多种输出方式,比如24bit I²S、24bit Left-Justified、16~24bit Right-Justified。

可以选择通过MCU,DSP等来控制芯片,设定芯片的工作状态。

工作电压范围为2.7~3.6V,典型应用电压为3.3V。

数字输入要求为5V TTL 电平。

PCM1738则是28针SSOP封装的24bit(192 kHz)采样率的数模转换芯片。

它的动态范围高达117dB,信噪比也是117dB。

一种高效的超高精度dac的合成方法及装置

一种高效的超高精度dac的合成方法及装置一种高效的超高精度DAC(数字模拟转换器)合成方法及装置是指可以将数字信号转换为模拟信号的装置,并且能够实现非常高的精度和效率。

该装置的合成方法主要包括以下几个步骤:1. 数字信号输入:将需要转换的数字信号输入到DAC装置中。

数字信号可以通过各种传输方式传输,例如串行或并行输入。

2. 数字信号解码:DAC装置将输入的数字信号进行解码,将其转换为二进制码。

3. 输出电压量化:经过解码的二进制码将被转换为相应的电压值。

这个步骤需要使用一组合适的参考电压,并对其进行量化操作,以确保输出电压的精度和稳定性。

4. 数字到模拟转换:量化后的电压值将通过一组可变增益放大器或可编程增益放大器进行放大。

这些放大器可以根据需要调整放大倍数,以实现更高的精度和精确的输出。

5. 模拟滤波:放大后的电压信号可能会包含一些高频噪音或杂散信号。

为了去除这些信号,需要进行模拟滤波操作,使用一些滤波器或低通滤波器来去除非基频成分。

6. 输出模拟信号:经过滤波和调整后的电压信号将作为输出模拟信号供外部使用。

输出电压可以通过一组输出电缆或连接器传输到其他设备或系统。

除了上述的合成方法,高效的超高精度DAC装置还应该具备以下几个特点:1. 低噪声:为了实现高精度的信号转换,DAC装置应该具备较低的噪声水平。

这样可以保证输出的模拟信号不会受到噪声的干扰,从而提高转换的精度。

2. 高线性度:DAC装置应该具备较高的线性度,以保证输入数字信号和输出模拟信号之间的对应关系是准确的。

这样可以避免非线性失真,提高转换精度。

3. 高速率:高效的DAC装置应该具备较高的转换速率,可以快速将输入的数字信号转换为模拟信号。

这样可以提高转换的效率和响应时间。

4. 低功耗:为了提高装置的能效,高效的DAC装置应该具备较低的功耗。

这样可以减少能源消耗,并且降低系统的热量产生,提高系统的可靠性和寿命。

综上所述,一种高效的超高精度DAC的合成方法及装置包括数字信号输入、数字信号解码、输出电压量化、数字到模拟转换、模拟滤波和输出模拟信号等步骤。

TDA1541 USB DAC解码器(内置耳机放大器))

因不满意电脑声卡音质,早就想自己制作一台USB DAC解码器,解码三大经典芯片TDA1541、AD1865、PCM63中的TDA1541是公认的人声之皇,而且采用多比特调制方式,所以我就选用的这个芯片来制作,虽然它的量化精度为16bit,低于现在常见的24bit的芯片,但现在的音源大部分都是16bit的,因此用16bit的芯片也足够了。

我做的这个解码器内置了耳机放大器,既可能输出音频信号给音频功放,也可以直接推动耳机,我平时主要使用耳机听音,现在使用的耳机是飞利浦的SHP8000。

使用效果比我的电脑自带的声卡好多了,主要感觉是信噪比高,声音动态范围大,全频表现比较均衡。

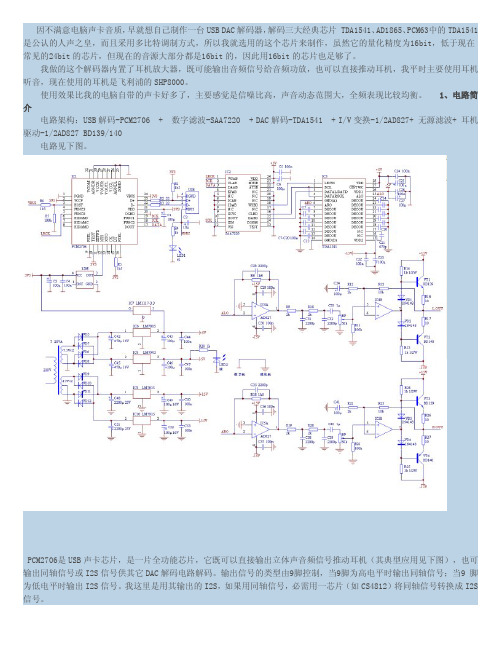

1、电路简介电路架构:USB解码-PCM2706+数字滤波-SAA7220+DAC解码-TDA1541+I/V变换-1/2AD827+无源滤波+耳机驱动-1/2AD827BD139/140电路见下图。

PCM2706是USB声卡芯片,是一片全功能芯片,它既可以直接输出立体声音频信号推动耳机(其典型应用见下图),也可输出同轴信号或I2S信号供其它DAC解码电路解码。

输出信号的类型由9脚控制,当9脚为高电平时输出同轴信号;当9脚为低电平时输出I2S信号。

我这里是用其输出的I2S,如果用同轴信号,必需用一芯片(如CS4812)将同轴信号转换成I2S 信号。

为了使电路工作更加稳定,使用了12M的有源晶振。

SAA7220是和TDA1541配对的数字滤波电路,一开始我采用的是无数字滤波的NOS电路,发现中低频醇厚,但高频表现稍欠佳,后来就加了SAA7220,感觉全频比较平衡。

由于TDA1541是电流型输出信号,因此输出信号要进行I/V变换,这里用运放作I/V变换电路,以左声道为例,电路由IC4A和R8、C28组成。

为了方便音量的控制,简化电路,LPF采用了无源滤波电路,由R9、R10、C31、C32等组成,其输出信号由IC4B、BD139、BD140放大后推动耳机或给后级功放提供音频信号。

一个12bit 800MSPS电流舵结构的高速DAC的设计 2021年0507

一个12bit 800MSPS电流舵结构的高速DAC的设计 2021年050712bit 800MSPS电流舵结构的高速DAC设计关保贞深圳集成电路设计产业化基地管理中心摘要:本文设计了一个分辨率为12位,采样频率为800 MHz的高速电流舵结构DAC。

该设计基于TSMC 0.18 um CMOS工艺,采用了二进制码控制和温度计码译码控制相结合的方式,从而在降低DNL误差和减小毛刺的同时,又能实现较小的芯片面积和功耗。

为达到高的精度和高的转换速度,该设计在系统结构、电路结构以及芯片版图等方面都做了优化。

关键词:电流舵温度计译码高速DAC1引言随着通信、多媒体技术和计算机技术的快速发展,D/A转换器(Digital-to-Analog Converter,DAC)被广泛应用于国防、生活、工业自动化等各领域。

速度、精度、功耗和芯片面积是DAC设计中的4个重要约束条件。

传统的电压分配或电荷分配DAC,在输出端都需要电流/电压转换的放大器,从而限制了DAC的速度与精度。

此外,传统的电流分配DAC需要用一个很大的器件来分配电流,会占用很大的面积。

目前,可内嵌的高速、高精度、低功耗DAC是模拟集成电路领域中的研究热点之一。

电流舵DAC(CSDAC)作为一种能实现更高速、更高线性度、更小面积的DAC,获得了广泛的应用。

CSDAC有二进制权值型和温度计译码型两种实现方式。

其中,二进制权值型DAC电路结构简单,但总谐波失真(THD)较大,单调性很差。

温度计译码型DAC需要复杂的译码电路,芯片面积较大。

综合二进制和温度型结构的优点,本文采用TSMC 0.18 um CMOS工艺设计了一个分辨率为12位、采样频率为800 MHz的DAC。

达到了在保持高采样率基础上保证单调性及降低谐波失真的目的。

2 CSDAC的结构及设计指标CSDAC的结构如图1所示,包括以下几个主要部分:电流基准单元,电流源阵列(SCA),电流舵开关,锁存器阵列,译码器和时钟驱动单元。

一种高效的超高精度dac的合成方法及装置与流程

一种高效的超高精度dac的合成方法及装置与流程近年来,随着科技的快速发展,对高精度数模转换器(DAC)的需求越来越迫切。

高精度DAC广泛应用于通信、测量、音频等领域,对精度和性能提出了更高的要求。

而超高精度DAC的合成方法及装置与流程,一直是学术界和工业界关注的焦点。

为了实现超高精度的DAC,我们首先需要选择合适的DAC结构。

常见的DAC结构有R-2R结构、Σ-Δ结构和时间交织结构等。

在选择合适的结构时,需考虑到性能、成本、功耗等方面的要求。

一般通过综合比较各种DAC结构的特点,选择最适合的结构。

在合成方法方面,我们可以采用数值计算与模拟仿真相结合的方式。

通过建立数学模型,利用数值计算方法求解模型的最优解,并借助仿真工具进行验证和优化。

在计算过程中,需将DAC的特性、非线性误差等因素考虑在内,以准确地获得所需的参数和指标。

此外,还可利用系统辨识的方法对DAC进行建模和参数提取。

在装置设计方面,需要充分考虑电路布局的优化和抗干扰能力的提升。

合理的布局设计可以最大程度地降低电路之间的互相干扰和噪声。

此外,还可采用抗干扰电路和滤波器等措施,提高系统的稳定性和抗干扰能力。

在整个流程中,还需要进行多次的验证和优化。

通过逐步优化电路参数、增加校准环节等方式,不断提升DAC的精度和性能。

同时,也需关注DAC的可放大性和集成度,以保证其在实际应用中的可行性和可靠性。

总之,实现超高精度DAC的合成方法及装置与流程是一个复杂而又关键的任务。

需要综合考虑结构选择、数值计算与模拟仿真、装置设计和多次验证与优化等因素。

只有在全面考虑并且不断改进上述各个方面的基础上,才能够有效地设计和实现超高精度DAC,满足现代高精度应用的需求。

采用TDA1541自制高品质DAC音响HIFI

采用TDA1541自制高品质DAC音响HIFI采用TDA1541自制高品质DAC一.电路设计有人曾对笔者说,DAC是属于数字产品,重点应在数字部分上,应在数字部分下大功夫,如加入二次锁相电路,模拟电路应属其次。

其实,之所以用数字方式来处理音乐,就是因为其失真度低,而音乐最后还是用模拟电路来放大再输出。

再者,看看国产的千元级的DAC 也用上了PCM63P。

IK作D/A转换,而几十倍价钱的进口I)AC也可能是用PCM63的,但两者的音质差别之大却是无法形容,这时总不可以说国产的。

DA C中用的PCM63P—K比进口的DAC中的差太远吧。

究其原因,两者最大的差异在于模拟输出电路,这才是进口高档DAC 与国产DAC的最大分别。

进口高档的DAC往往使用了极为复杂的晶体管输出电路。

笔者曾机缘巧合得到一片富士通的锁相模块,尝试过在一台DAC 中加入二次锁相环电路,效果比一般的锁相电路好。

但结果,提升也并不大,还不如将输出的NE5532换成OPA2604的区别大,原因可能是现在的DIR芯片的性能已相当不俗,与以前的YM3623之类的相比,其内部时钟锁相电路性能优异,令时钟的稳定性提高了不少。

当然,用二次锁相电路再提高时钟稳定性会更好,但并不是所有的锁相电路都能比CS8412内部的好,一个优良的锁相电路的成本也不菲,且元件难觅,倒不如将更多的资源放在其他效益高的方面。

一直以来笔者都很钟爱于.Philips的TDAl541A与DAC7(TDAl 547,此DAC的制作有机会再另文介绍),可能是个人的主观偏见,也因PCM系列的多比特D/A通常有LSB与MSB这两个调整端子,而笔者没有仪器去对此进行准确测试,未经调整会对D/A的转换精度有一定的影响,使PCM系列的芯片没能完全发挥,其他一些24bit精度的lbit的D/A芯片,声音又过于冷艳和单薄。

笔者认为TDAl 541A与DAC7这两片IC的设计是相当完美的。

DAC7相信不少朋友会认同其品质,而TDAl541A可能会有异议了,因其只是一个16bit.的早期设计,距今有20年的历史了。

自制胆DAC解码器

自制胆DAC解码器李怡南普通CD唱机的声音往往不够真实自然,尤其高频失真更为严重,例如铙钹的声音听起来会像高压空气泄漏时发出的声音一样。

加接一台DAC解码器可以使声音得到改善,但市场上出售的解码器往往很昂贵,廉价品种又不能令人满意。

这里介绍一款解码器的详细制作资料,供爱好者仿制。

一、电路组成一台音频DAC由四个主要部分组成,见图1,即:解码器、数字滤波器、DAC和模拟信号放大器。

●解码器:由转盘获得的数据格式为标准的Sony/Phillips数字接口格式(简称S/PDIF格式),其中除音频数据外,还包含有取样频率的时钟信号、录音时是否采取了预加重处理的标志等其它信息。

解码器的作用就是从串行的数据流中把这些信息提取出来,供下一步处理便用。

从理论上说,如果解码芯片的性能足够好的话(能获得十分稳定的时钟信号),转盘与解码器间采用何种传输方式(例如光学方式或同轴方式)以及使用何种品牌的信号线都不应存在任何效果上的差异。

本机所用的Crystal解码芯片CS8412-KP是一种很好的芯片,但仍不够完美,所以仍能听出不同信号线之间的差别。

笔者正在继续探索新的解决方案,例如用模拟芯片AD1890作为缓冲器并重建时钟信号。

有兴趣的读者也不妨自己探索一下。

●数字滤波器:其作用是利用有限脉冲响应技术(Finite Impulse Response technique)进行插值处理,即在真实的音频取样点之间插入一些由计算得出的虚拟采样点。

这种做法称为“超取样”,好处是可以使数模转换过程中产生的量化噪声的频谱向高频端移动,远离人耳可闻的频带,分离起来可以比较容易和彻底,整机信噪比会有所提高。

本机采用的芯片为8倍超样,即将其时钟频率提高到标准采样频率的8倍,因此量化噪声的频率可高达352KHz。

然而,笔者认为不应该把超取样的作用无限夸大,没有任何理由可以说8倍超取样的声音一定会比两倍或四倍取样更好,它的作用仅仅是改善信噪比。

一种基于WM8741的音频解码器研究与设计

一种基于WM8741的音频解码器研究与设计、A/V接收设备、CD/DVD播放器等。

其内部具有颤动数字内插值、精细辨别率音量控制和数字去加重功能、1个多比特∑-△调制器以及带有差动输出的开关多位电路级。

特有的可编程配置的高级数字滤波器允许用户灵便挑选群延时、相位延迟、脉冲响应等。

音频输入接口支持I2S、Left-justifted、Right-justified和DSD格式。

当以PCM信号输入时,器件能够接收字长度16~32位,采样转换速率32~192kHz。

该器件具有硬件和软件两种控制方式,并通过外部引脚举行切换挑选。

软件控制模式下,外部CPU通过2线或3线方式拜访其内部全部寄存器并设置参数。

WM8741的信噪比达128dB(单声道),动态范围达125dB,通道分别度达130dB,电源抑制比可达-80dB(100mVpp,lkHz)。

转换后的模拟电压采纳差动方式输出。

WM8741的数字部分的供电电压为3.0~3.6V,额定工作电压为3.3V;模拟部分的工作电压为4.5~5.5V.额定工作电压为5.0V。

该器件采纳28引脚SSOP封装。

3 解码器硬件设计3.1硬件组成图1是该解码器硬件结构框图,其中数字音频接收器采纳Logic公司的高速数字音频接收器CS8416,该器件支持包括S/PDIF在内的多种音频输入,取样频率范围为32~192kHz。

CS8416通过I2S接口与WM8741相衔接。

I2S只处理音频数据,其他控制信号必需单独传输。

CS8416的工作原理:接收器把接收到的S/PDIF格式的数字音频数据举行解码转换,同时重建音频数据中的时钟并提供应后续WM8741,音频数据则通过I2S总线接口发送给WM8741。

WM8741根据设定的参数完成数模转换后,再以差分形式输出左右通道的模拟音频信号,并经滤除高频谐波噪声,终于得到高质量模拟电压信号。

假如输出接口为RCA,还需将差分信号转换为单端信号。

3.2数字音频信号接收模块CS8416是数字音频信号接收电路的核心。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一款发烧DAC音频解码器的设计与制作摘要:随着数字音频时代的来临,数字音源也不断丰富,然而这些数字音频设备内建的DAC采用一体化设计,易受干扰,解码出来的声音并不尽人意。

一般的数字音源如CD、DVD、网络机顶盒等都配备了光纤和同轴输出接口,把数字音频信号绕开机内的DAC,直接送到专门的音频解码器,由专门的解码器完成D/A转换,实现声音的高保真重放。

本文本着hi-fi的设计原则,设计一款立体声DAC音频解码器,由LM317、TL431组成多路甲类并联稳压供电,采用经典的高性能的CS8412-CP负责数字信号的接收与解调、DF1700P数字滤波、R-2R架构的PCM1702-K做D/A转换、挑选发烧运放担任I/V和LPF,完成数字信号的接收并转换成高保真的音频信号,再通过一级电子管校音线路,输出驱动信号可以直接推动后级的甲类晶体管功放。

实现hi-fi 效果的重放。

关键词:DAC音频解码器 PCM1702-K 电子管校音高保真甲类并联稳压1. 引言:一些低中档数字音源输出的音频声音生硬,数码声重,音质刺耳烦躁,不耐听,满足不了音响发烧友的听觉需求。

主要是因为这些机器内建的音频DAC性能差,模拟滤波、放大器件普通,供电也过于简单造成。

好在这些机器一般都配有光纤或者同轴输出端口,提供数字音频信号输出,供高档的DAC音频解码还原高保真的声音。

有动手能力的烧友都喜欢DIY一台高性能的DAC音频解码器以重放hi-fi的音响效果,满足自己的听觉需求。

2. DAC音频解码器电路的设计2.1 DAC音频解码器电路组成DAC音频解码器由数字信号接收器、数字滤波器、D/A转换器、I/V转换器、LPF滤波器将数字音频还原还原成模拟音频信号,再通过电子管组成的和田茂氏线路校音、开机延迟吸合电路控制输出模拟音频信号推动后级功放。

电路的组成及其信号流如图1:图1 DAC音频解码器组成及信号流程2.2 数字信号接收与音频解码电路数字信号的接收与解码电路关系到音频信号还原的质量,想要得到高保真的声音,必需采用高性能的器件担当音频DAC解码的重任,这是重点部分,电路原理图见图2,下面对其原理作进一步的分析:2.2.1 数字信号接收器数字信号接收采用美国CRYSTAL公司的带有PLL的解调芯片CS8412-CP担任,能自动识别32K-48K采样率。

外部数字音源通过光纤线送来的信号被光纤接收头TORX179接收并转化成电信号,经电容C201、C202耦合到IC201的10脚,外来同轴信号(或者CN5插上音频蓝牙模块输出的同轴信号)经C203耦合到IC201的9脚,IC201内部自动识别信号源并将其选通,省去输入切换开关,简化电路。

当然光纤和同轴不能同时有信号输入,否则IC201无输出。

信号通过IC201内部处理,恢复时钟和同步信号,并把音频信号和数字数据进行分离,由12、11、26脚输出音频串行数据SCK(串行时钟)、LRCK(左右时钟)和SDATA(串行数据),音频串行输出信号的格式受M0、M1、M2、M3控制,M3=0时为标准串行格式,应用时置M3=0,M0、M1、M2设置与对应的8种音频数据输出格式见表1,应用时设置模式根据后接数字滤波,D/A芯片而定。

表1 CS8412-CP 采样频率与输出格式设置2.2.2 数字滤波器数字滤波器的作用是把接收解调后的数据信号进行运算,完成超采样、实现升频或降频,也可以进行I2S之类的格式转换,本机采用了BB公司28脚双列直插封装的DF1700P数字滤波器,具备8X超采样,其引脚功能与内部结构如图3图3 DF1700P引脚功能与内部结构6脚、7脚外接16.9344MHZ晶振,为了更好实现信号的同步性,16.9344MHZ主时钟信号(MCK)直接由IC201的19脚提供, 26、12、11脚将SDATA、SCK、FSYNC数据送到DF1700P的1、2、28脚,进入DF1700P内部运算,从24、23脚输出左右通道音频数据流,25脚输出WCK、26脚输出BCK进入音频解码级。

DF1700P的3、4脚设置采样率,16 、17脚切换比特率。

3、4,16、17脚设置与对应采样率、比特率见下表2:表2 DF1700P 采样率与比特率设置2.2.3 音频解码器这部分是DAC音频解码器的核心。

其实质是一个数模转换器,只不过人们习惯叫音频解码器罢了,在DAC芯片选择上有部分发烧友片面追求器件的高比特数和取样率。

认为具有24Bit/96KHz的芯片其音响效果就一定要好于低位数低取样率的产品。

这实际上是一个误解。

这里要强调的是作为CD格式其音频数码流为 16Bit/44.1Khz 。

这是CD盘的标准。

有些CD盘面标定20Bit、24Bit、96Khz、192Khz这是指在录音过程采用的记录格式,在烧录CD光盘时无一例外的要重新编码的16Bit/44.1Khz数据流。

作为CD音频DAC解码器都要工作在这个格式下。

不同采样率和比特率的芯片其音质是有差别的,高比特及高取样率只能说明该芯片可工作在不同数据流方式及能够达到的精度。

因而本机采用具有超低失真、低噪声、线性好的R-2R架构的D/A转换芯片PCM1702-K。

PCM1702-K是美国BB公司的高性能D/A转换芯片(K是这型号的最高级别),两片PCM1702-K担任左右声道的D/A 转换,具有20Bit的精度,完全胜任音频CD的解码。

芯片采用了数字+-5V和模拟+-5V分开供电,需要注意的是5脚为数字-5V的供电端,静态电流达30mA电源设计要考虑其功耗。

PCM1702-K的1、2、6脚分别接收来自DF1700送来的DATA、BCK、WCK信号,经内部D/A转换后,从11脚输出音频电流信号,11脚输出的音频电流具有超低失真、低噪声、线性好的特点。

2.2.4 I/V转换器从PCM1702输出的电流信号比较弱,大约为1mA左右,所以需要一个I/V转换器将PCM1702-K的电流信号转换成电压信号,由于I/V 转换级对音色的影响极大,在设计上本机采用了JRC公司旗舰版高性能双运放musec02来担任I/V转换。

musec02在日本音响届被号称"原音守护神",其声音谐波丰富,解析力高,音场宽广,层次分明,声音醇厚而通透,是一种音效全面的发烧运放。

与反馈电阻并联的电容取100-220P比较合适,取值太大会影响运放的速率,影响高音的细节。

2.2.5 LPF滤波器数字音频经过PCM1702-K进行D/A转换后,还需要一个LPF低通滤波器,去掉信号中不必要的高频成分,去除高频干扰。

常见的有源低通滤波有巴特沃斯滤波器、切尔雪夫滤波器等等,然而本机采用了BB公司专门为R-2R架构设计的GIC低通滤波器,有很好的线性相位特性,通带增益平坦,从而使音频信号通过滤波器后的失真很小,保证了音频信号的高质量。

如图2,GIC滤波由R402-R412以及双运放IC403、IC404、C403-408等组成3阶低通滤波器,按照图中阻容参数取值,截止频率为40KHZ。

2.3 线路放大器考虑到用电子管制作的前级电路音色圆润、人声甜美、音乐味浓,声音耐听、适合人声的演绎,本机设计了一级由电子管组成的线路放大器作输出,一来可以校声,二来提高解码器增益直推后级功放。

如图4,电子管线路放大参照了日本著名的和田茂氏线路,线路是以12AT7两级放大(约12倍)加一级用12AU7作SRPP阴极输出,减小输出阻抗和增大输出电流,增强带载能力。

放大后的信号经过电位器进行音量控制后输出到后级。

线路放大不设音调控制,信号直通,确保原汁原味。

图4 电子管线路放大与开机延迟吸合电路2.4 开机延迟吸合电路由于电子管通电时需要预热,预热期间工作点不稳定,会产生脉冲电流输出冲击功放级,逼使功放级进入保护。

所以在信号输出端加入了由STC单片机组成的开机延迟吸合电路,见图4:通电时单片机12C2052在特定的程序下运行,P1.0口电平高低交替变化,电源指示灯闪烁,表示机器热机;同时P1.1口为高电平,继电器失电常闭触电接通短路输出信号;大约30S之后单片机 P1.1口输出低电平驱动继电器吸合,常闭触点断开,短路解除,让信号通过RCA端子输出,同时P1.0口锁定低电平,电源指示灯变为常亮,机器进入正常的状态工作。

采用这种通过短路信号阻止其输出的控制方式回避了输出信号流经继电器的触点,减少音染。

2.5电源电路2.5.1 DAC主板供电电源部分在解码器中也是一个不可忽视的部分,主要克服电网中电波对电路的影响,还要克服数字电路部分对模拟电路的影响,更重要的是要具有极低的动态内阻。

高质量的电源可以令D/A芯片、高级运放的性能发挥的淋漓尽致,在试验时发现,普通的7805、7905、317、337这些三端稳压器件用于高级的D/A芯片和运放供电,主要是令中频的圆润、低频的弹性与力度变差,根本不能发挥D/A芯片和运放的性能,原因是78系列属于串联稳压器件,内阻大,影响了芯片性能的发挥。

然而并联稳压电源其动态内阻低,有利于电路能量的吸收,其性能接近与蓄电池,是DAC理想的电源。

甲类并联稳压电源缺点是功耗大、效率低,但在DAC电路的静态电流不算大的情况下,采用甲类并联稳压供电功耗也不是问题,所以本机设计了8组具有极低动态内阻的甲类稳压电源为DAC电路供电,数字与模拟分开供电,模拟地与数字地一点连接,并在交接处用电感磁珠隔离。

具体电路见图5图5 DAC解码板供电原理图整机采用3个电源变压器供电,其中2个35W的环牛提供双9V、双16V交流经整流滤波,由LM317T组成恒流源,TL431、MJE172G构成并联稳压电路输出D5V-1、D5V-2、D+5V、D-5V、A+5V、A-5V、 A+15V、A-15V为CS8412-CP、DF1700P、PCM1702-K、4个运放供电。

其工作原理:是LM317、R组成恒流源,恒流源的高内阻将电路与电网干扰隔离,R的大小决定恒流值,一般取电路静态电流的1.5-3倍比较合适,恒流数值计算公式I=1.25V/R(1.25V是LM317内部的基准电压),TL431与R端连接的上下电阻组成并联稳压得到2组5V为数字电路CS8412-CP和DF1700P供电,PCM1702-K用的D+-5V和低通滤波运放用的A+-15V,由于其工作电流较大些,TL431的功耗不够,需要用安森美MJE172G组成扩流再输出。

这电源设计是本机的特色,因为电源内阻很小,在实际试听中,高频解析力和低频力度和深度、人声的圆润上比串联稳压供电有很大的改善和提高。

2.5.2 电子管线路放大供电电子管线路供电采用了1个50W的电源变压器,见图8。

次级15V 绕组经过整流滤波、LM317稳压在12.6V为12AT7、12AU7灯丝供电,调节RP3可以改变输出电压,灯丝采用直流供电有利于提高信噪比;2组250V采用2只6Z4分成2路全波整流,再通过电容滤波,LM317稳压的得到2组270V电压分别为电子管的阳极供电,左右声道独立供电,这样可以提高了立体声分离度。