PLL频率综合器中整数和小数分频器设计与实现

小数分频器的设计及其应用

第24卷 增刊2005年9月国 外 电 子 测 量 技 术Foreign Elect ronic Measurement TechnologyVol.24,Suppl.Sep.,2005作者简介: 尹佳喜(1981-),华中科技大学电气与电子工程学院04级研究生,研究方向电力电子与电力传动。

研究与设计小数分频器的设计及其应用尹佳喜(华中科技大学电气与电子工程学院 湖北武汉430074)摘要:分频器是数字系统设计中最常见的电路之一,在数字系统设计中,经常需要对时钟进行小数倍分频。

本文给出了三种用于实现小数分频的方案,并将三种方案进行了比较。

在此基础上,介绍了小数分频器在直接数字频率合成技术和步进电机驱动速度控制中的两种常见应用。

关键词:小数分频器 直接数字频率合成 步进电机 频率The Design and Application of Decim al Fraction Frequency DividerY in Jiaxi(College of Elect ricit y and Elect ronic Engeneering ,H uaz hong Universit y of S cience and Techlonog y ,W uhan 430074,China )Abstract :Frequency division is one of t he mo st common circuit s in t he design of digital system.Generally ,decimal f raction f requency division is needed.In t his paper ,t hree met hods to realize deci 2mal f raction frequency division are given ,and t he comparison among t he t hree met hods is presented.Applications of decimal Fraction Frequency divider in t he area such as direct digital f requency syn 2t hesis technology and stepper motor drive speed controller are int roduced.K eyw ords :decimal f raction frequency divider ,direct digital frequency synt hesis (DDS ),stepper mo 2tor ,frequency.0 引言 现代电子系统设计中,数字电子系统所占的比例越来越大,现代电子系统发展的趋势是数字化和集成化。

任意数(整数、小数)分频器

任意数(整数、小数)分频器一、分频原理1.1偶数倍分频偶数倍分频通过计数器计数是很容易实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的偶数分频。

1.2奇数倍分频奇数倍分频通过计数器也是比较容易实现的,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

与此同时进行下降沿触发的模N 计数,到和上升沿触发输出时钟翻转选定值相同值时,进行输出时钟时钟翻转,同样经过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。

两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟。

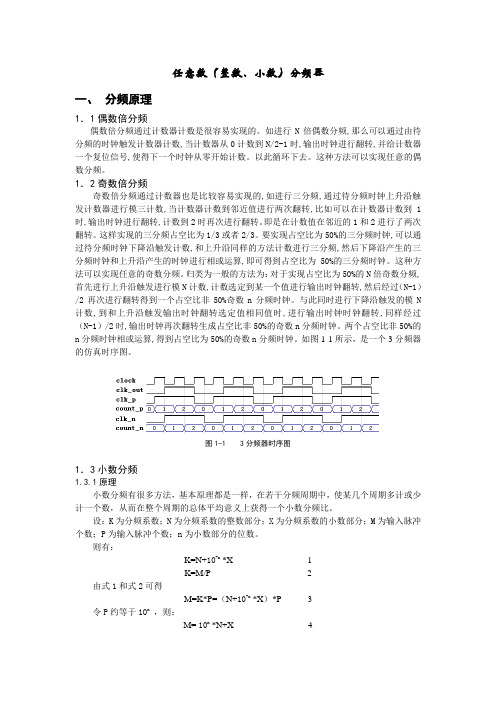

如图1-1所示,是一个3分频器的仿真时序图。

图1-1 3分频器时序图1.3小数分频1.3.1原理小数分频有很多方法,基本原理都是一样,在若干分频周期中,使某几个周期多计或少计一个数,从而在整个周期的总体平均意义上获得一个小数分频比。

设:K为分频系数;N为分频系数的整数部分;X为分频系数的小数部分;M为输入脉冲个数;P为输入脉冲个数;n为小数部分的位数。

基于FPGA的小数分频器的设计与实现

基于FPGA的小数分频器的设计与实现【摘要】本文首先分析了现有小数分频器的优缺点,在此基础上提出了一种改进型小数分频器的设计方法。

同时结合VHDL文本输入和原理图输入方式,在FPGA开发平台上进行了电路设计,最后利用EDA设计软件QuartusII对其可行性进行了仿真验证。

仿真结果表明:通过对参数的设置,该方案可实现等占空比的任意小数分频。

【关键词】FPGA;仿真;VHDL引言分频器是控制类电路中常用的模块之一。

在实际应用中,设计人员常常需要将一个基准频率通过加、减、乘、除简单的四则运算进行频率合成,以满足不同的电路需求。

常见的偶数分频、奇数分频等成整数关系的频率合成实现相对比较容易。

但在某些的情况下,这种成整数关系的分频技术无法解决频率调整间隔过大的缺点,在此情况下本文提出了一种基于FPGA的小数分频的设计方法。

一般情况下,小数分频器包括半整数分频器和非半整数分频器。

对于半整数分频器我们在《基于FPGA 的通用数控分频器的设计与实现》[1]中有过详细介绍。

本文主要介绍非半整数分频器的设计和实现,并在FPGA开发平台上,结合VHDL文本输入和原理图输入方式进行了电路设计,同时利用EDA开发软件QuartusII对其可行性进行仿真验证。

仿真结果表明:该方法实现的小数分频,具有精度高、转化速度快、资源消耗低,可编程等优点,同时克服了小数分频中等占空比不易实现的问题。

1.几种常见小数分频器假设分频系数为K,输入频率为fin,输出频率为fout,则有:(1)其中:K>1当分频系数为小数时,则K可以表示为:(2)或:(3)其中,M、N、N1、N2均为正整数,且。

1.1 用BCD比例乘法器4527实现对于公式(2),可以利用十进制BCD比例乘法器的加法级联来实现[4]。

如图1所示,为两个4527 BCD比例乘法器的级联。

CLOCK端输入基准频率信号fin。

A、B、C、D四个端口是置数端,用以控制比例乘法器输出脉冲序列的个数。

小数N分频频率合成器的原理和实现

2. 传统 F-NPLL 频率合器的原理

传统的 F-NPLL 频率合器的结构如图 1 所示,它是由鉴相器(PD),低通滤波器 (LPF),压控振荡器(VCO),双模分频器 (÷ N/N+1),累加器(P+Q)组成。

两起故障都具有失磁故障的特征:无 功反向。值班人员按规定迅速降低有功负 荷,机组进入失磁异步运行状态,在消除失 磁原因后,恢复励磁(启动备用励磁机、手

上接第 158 页 其中电荷泵(CP)部分可以很方便地 设置环路增益并简化积分器的实现(也可 不用),能够把误差信号转变为电流信号, 用于驱动环路滤波器。整个环路的工作原 理:先将压控振荡器频率预置在一个粗值 上,经分频器分频(通过改变分频比来减小 剩余相位抖动),分频后的频率与基准频率 在鉴相器中比相,产生的差值信号经环路 滤波器的积分和滤波,形成的直流信号加 到 VCO 上微调 VCO 输出频率,使其频率 锁定在预置频率上,其频率稳定度和准确

动 合 灭 磁 开 关 ),使 发 电 机 重 新 进 入 同 步,恢复正常工作状态。

5 结束语

同步发电机失磁异步运行时要从系统 吸取大量的无功功率,这无论对系统还是 发电机本身的安全运行都会带来不良的影 响。但是理论研究和运行经验都表明,在一 定的条件下,积极而谨慎地利用同步发电 机短时间的异步运行,采取措施恢复励磁, 使之迅速恢复同步,对于改善电力系统的 运行条件也是有利的。

汽轮发电机的转子是个圆柱体,纵轴 和横轴的磁导相差不大,因此两倍频率电 流在发电机中引起的机械振动较小,对机 械强度危害性较小。而对于转子是凸极式 的水轮发电机由于转子的直径较大,纵轴 和横轴的磁导相差较大,所引起的振动较 大,对机械强度有较大的危害性。

小数N分频低相噪频率合成器设计

小数N分频低相噪频率合成器设计摘要:频率合成器是无线通信系统的重要组成部分,被称为系统的心脏。

换频时间及其频率稳定度、频率分辨率、相噪噪声是其关键参数。

本文介绍一种基于小数N分频的锁相环(PLL),结合高稳压控振荡器(VCO),输出精度准确,换频时间短,频率步进小的频率合成器,能实现每秒1000跳及以上的频率变换,切换频时间部超过20us。

1 绪论1.1课题研究的背景和意义从20世纪80年代以来,随着计算机、数字信号处理、扩频通信、自适应通信等现代电子信息技术的发展,各种先进的电子技术和新型的元器件被广泛地应用在现代军事通信领域。

跳频通信作为扩频通信的一种主要形式,由于其具有抗干扰、保密、抗截获和抗衰落等特点,并能做到频谱资源共享,在当前军事抗干扰通信系统中被广泛应用。

跳频通信系统的一项重要参数是频率的跳变速度,它在很大程度上决定了跳频通信系统抗跟踪式干扰的能力,这一点在电子对抗中尤为重要。

因此,高速的频率合成器就成为跳频通信系统中的关键部件之一。

本课题的主要任务是研制一个高跳速、高分辨率、高频谱纯度的小型化频率合成器,其设计基于集成的PLL芯片及高度稳定的VCO,能够满足高分辨率、高频谱纯度的频率合成器,系统能快速适应风云变化的战场环境,提高通信装备的灵活性。

本课题运用当今先进的器件资源和设计思想,研究具有高跳速、高分辨率、高频谱纯度的小型化频率合成器,实践军事通信的前沿技术,因此这是一项值得深入研究的课题。

1.2 国内外的研究现状随着现代电子技术进步和器件制造工艺的提高,目前频率合成主有三种方法:直接模拟合成法、直接数字合成法和锁相环合成法。

直接模拟合成法利用倍频(乘法)、分频(除法)、混频(加法与减法)及滤波,从单一或几个参考频率中产生多个所需的频率。

该方法频率转换时间快(小于100ns),但是体积大、功耗大,目前已基本不被采用。

直接数字合成(DDS)是从相位概念出发直接合成所需波形。

DDS应用在射频段的一个缺点是它的时钟频率要高于输出信号至少两倍,而如此高的时钟频率是不易实现的,并且D/A变换器的速度也限制了DDS的工作频率。

资料:PLL格式

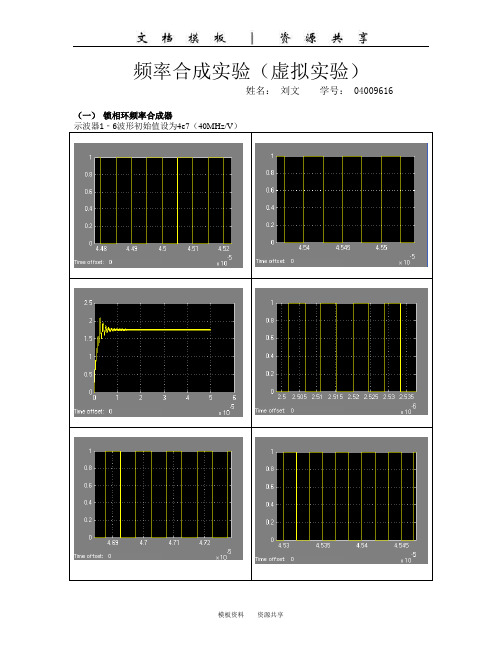

频率合成实验(虚拟实验)姓名:刘文学号: 04009616(一)锁相环频率合成器示波器1‐6波形初始值设为4e7(40MHz/V)分析:30M参考频率经过3分频fr即为10M,fo经过10倍分频等于fr,所以fo就是100m,如图所示。

示波器1为示波器6的波形经过3分频后的方波,频率为1MHz。

压控振荡器上的控制电压的变化情况:从0开始震荡到1.75。

示波器4上的方波频率为10MHz。

经过N分频后和参考频率异或形成示波器2中的方波。

低通滤波器的作用是平滑平滑VCO的控制电压。

如果将低通滤波器的带宽减小,那么环路锁定时间会增加,锁定后控制电压更稳定。

将synSen 的初始值设为3e6(3MHz/V),示波器1‐6波形将synSen 的初始值设为5e6(5MHz/V),示波器1‐6波形分析:(将synSen的初始值为3e6与5e6与初始情况作比较)两种情况稳定后结果均与synSen为4e6时相同,捕捉时间也基本相同,这是由于PLL换频时间仅与参考信号频率有关。

但由VCO控制信号波形可以看出,30M参考频率经过3分频fr即为10M,fo经过10倍分频等于fr,所以fo就是100m,如图所示。

由于灵敏度不同导致需要的压控电压不同,如图3M的压控电压明显大于5M时的压控电压。

synSen为3e6时,捕捉过程控制信号波动较大,稳定后控制信号波动也较大,这是由于VCO压控灵敏度小导致同样的频偏需要的控制电压更高。

synSen为5e6时,捕捉过程信号波动较小,稳定后信号波动也较小。

(二)小数频率合成器分析:小数分频既是双模分频,十分之七个循环周期的时间,进行3分频,其余时间进行4分频,导致3.3倍分频。

输入信号频率为10MHz。

由图像可以看出,输出信号频率约为103.1MHz,分频比为10.31,与要求基本相符。

从波形中我们可以看到,由于相位累加器每次大约约累计1/3*2π的相位,使得Carry信号频率大约1/3输入信号。

小数分频论文频率合成器论文

小数分频论文频率合成器论文摘要:本文进行了基于小数分频技术的频率合成器的研究与设计。

首先分析小数分频锁相的工作原理,随后设定了设计指标,进行控制部分设计、环路滤波器设计、压控振荡器的设计,从而实现基于小数分频技术的频率合成器。

并通过测试,其性能指标已达到设计要求。

关键词:小数分频;频率合成器;分频frequency synthesizer design based on fractional frequency division technologywang xiaoning(dalian air traffic controlstation,dalian116033,china)abstract:this article was based on fractional frequency synthesizer technology,research and design.first of fractional pll works,then set the design specifications,the control part of the design,loop filter design,the vco design,enabling technology-based fractional frequency synthesizer.and tested,its performance has reached the design requirements.keywords:fractional frequency division;frequencysynthesizer;frequency一、引言小数分频频率合成器是近年来出现的一种新技术,与传统的频率合成的技术方式相比,它具有分辨率高,相位噪声低的优点。

dds也是今年出现的一种新型技术,但是dds的工作频率一般较低,如果实现的频率合成器需要较高的频率,仅仅使用dds很难满足。

基于FPGA的任意数值分频器的设计

3

11

16

4

第 36卷第 2期

周殿凤, 等: 基于 FPGA 的任意数值分频器的设计

# 技术应用 #

到了最大。

5 结束语

图 4 3 161分频器波形图

4 任意数值分频器

加入控制模块就可以将上述 4种分频器集成到一 起, 变成任意数值分频器, 顶层原理见图 5。

文中介绍了任意数值分频器的设计, 可以方便地 对占空比和分频系数进行调节而不需要重新编程, 整 个程序占用逻辑资源不到 EP2C35 芯片的千分之一。 本设计有很 大的 通用 性, 可以 在不 同的 FPGA 甚至 CPLD芯片间移植, 不管对初学者还是程序设计人员 都有一定的参考价值。

通过分析分频器的原理探索出了一套简单明了的设计方法设计了一个任意数值通用分频器整数分频器偶数分频器的设计较为简单可以利用计数器实2n分频当计数器的值为0在计数器值为2n1时复位计数器如此循环下去即可实现占空比为都是预置数不同分频系数也就不同如果预置数是奇数则可实现占空比不等于50的奇数分频

第 36卷第 2期 2010年 2月

[ 1] 张静亚. FPGA 系统设计中资源分配的分析和研 究 [ J]. 信 息化研究, 2009, 35( 3) : 37-39.

[ 2] 周子昂, 王福 源, 魏军 辉. 基于 FPGA 的通 用分 频 器设 计 [ J]. 微计算机学报, 2009, 25( 3-2): 207-209.

[ 3] 潘松, 黄 继业. EDA 技术 实用 教 程 [ M ] . 北京: 科学 出 版 社, 2006.

关键词: FPGA; VHDL; 分频器 中图分类号: TP277

0引 言

FPGA 作 为 未来 数 字 系统 的 3 大 基 石 ( FPGA、 D SP、CPU ) 之一, 成为 目前硬 件设 计研 究的重 点 [ 1 ] 。 在数字系统的设计中, 设计人员会遇到各种形式的分 频需求, 如偶数分频、奇数分频、半整数分频、小数分频 和分数分频等。在某些设计中, 系统不仅对频率有要 求, 而且对占空比也有严格的要求。由计数器或计数 器的级联构成各种形式的偶数分频及非等占空比的奇 数分频实现起来较为简单, 但对半整数分频及等占空 比的奇数分频实现较为困难, 小数分频和分数分频更 困难 [ 2] 。为了解决这一问题, 本文首先分析了各种分 频器的设计方法, 然后将其综合起来成为一个通用分 频器。通过分析分频器的原理, 探索出了一套简单明 了的设计方法, 设计了一个任意数值通用分频器, 该分 频器没有毛刺且占用的逻辑资源较少。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

东南大学

硕实现

姓名:舒海涌

申请学位级别:硕士

专业:电路与系统

指导教师:李智群

20100306

PLL频率综合器中整数和小数分频器设计与实现作者:舒海涌

学位授予单位:东南大学

1.康建颖频率综合器中的分频器电路设计[学位论文]2009

2.余俊宽带CMOS锁相环中小数分频器的设计[学位论文]2009

3.朱凯应用于GPS接收机频率综合器分频器的设计[学位论文]2008

4.陆磊无线传感网频率综合器前置分频器的设计与实现[学位论文]2009

5.侯凝冰WSN频率综合器中PFD和CP设计与实现[学位论文]2010