图形电镀边缘效应的研究

PCB加工过程中图形电镀“凹坑”产生原因和解决方法

PCB加工过程中图形电镀“凹坑”产生原因和解决方法凹坑"是指图形电镀后在大铜面、线路、焊盘、金手指上出现的点状凹陷.在大铜面上出现的较轻微的"凹坑",用砂纸打磨平整,不影响外观、电气性能.但对线路、边接(焊)盘,尤其是金手指上的凹坑,用砂纸打磨难以整平,将影响其外观、插拔、焊接等,往往不能被客户接受.电镀"凹坑"问题不当,在全在线漫延,其损失报废是可怕的,对生产厂家来说,在生产的各工序严加把关,进行控制是至关重要的.以下是我们处理分析图形电镀最近发生"凹坑"的一些体验,供同行们参考.1.氯离子偏低.在高分散性硫酸盐光亮镀铜液中,加入活性强的氯离子,使阳极极化位提高,形成胶状的CuCl2吸附在阳极表面,抑制Cu-e→Cu+反应.如果氯离子偏低,则含磷铜电阳极在电解过程中因缺少CL-,而不能与Cu+化合形成胶体吸附在阳极表面,因而不能正常进行溶解,导致电镀铜层表面产生凹凸不平.2.光亮剂偏低.在酸性硫酸铜镀液中加入光亮剂,可电镀出平整光亮的镀铜层.光亮剂由多种成份组成,其中含有光亮剂、整平剂、润湿剂和分散剂.光亮剂是含硫的烷基或苯基磺酸盐类,对镀铜层起到光亮作用;整平剂能被吸附在阴极表面,尤其是微观凸出部位从而对电沉积起到抑制作用,使镀铜层平整.湿润剂、分散剂一般为非离子型表面活性剂,它能降低镀液的表面张力,起到湿润及对镀液相互扩散作用.3.镀液本身被油污及有机杂质污染.4.待图形电镀板不满足生产要求.例如,未电镀前覆铜板材凹凸不平,图形电镀不能把凹凸处电平整.其次,板面在图形电镀前被脏污污染或干膜显影不凈及干膜上的油污太多、粘在板上,按正常前处理难以去除污物,导致有污物在位置不能电镀上铜.5.图形电镀前处理液被污染或因浓度低,不足以去除板面的氧化、脏污.控制凹坑问题的途径针对凹坑产生的原因,结合公司设备及药水的情况,杜绝凹坑的发生,主要有以下几方面:1.按频率定期对镀铜液化验分析补加.如氯离子含量在40ppm以下图形电镀时,板面失去光泽、粗糙、凹凸不平.因氯离子含量较少,难免有误差,应根据平时做板质量的好坏及氯离子添加量多少的经验做参考.特别注意在清洗完铜球并电解预镀(拖缸),为生成新的阳极膜而消耗更多的氯离子.需把各成份调整到以下数值:硫酸铜为70g/l;硫酸100ml/l; 氯离子为70ppm;PCM光亮剂为3.0ml/l.2.按250ml/千安培.小时含量添加光亮剂,光亮剂消耗量的多少与温度、槽面的大小、打气量、碳芯过滤、电镀图形面积大小及镀铜厚度等因素有关,特别是电解预镀(扦缸)后光亮剂的补加,防止光亮剂的消耗量大于添加量,长时间导致光亮剂偏低,通过做赫尔槽片来确定光亮剂的被加量.3.当镀液中含有有机杂质及油污时,电解时板面沾到油污处不能电镀上铜,导致板面凹凸不平、粗糙,需定期采用碳芯过滤,去除镀液中的有机杂质及油污.4.控制好待图形电镀板的质量.如来料板面凹坑带到图形电镀工序,电铜不可能把凹坑整平.这时需在图形电镀前打磨平整.干膜显影不凈、板面残胶及板面脏污,按正常的图形电镀前处理,不能去除,致使某些位置不能电镀上铜,形成凹坑.5图形电镀线前处理液被污染或浓度低,难以去除板面氧化物、油污、脏污.对被污染的图形电镀前处理液应更换或对前处理各参数不在控制范围内时需进行调整,我们以除油浓度控制在200ml/l~250ml/l,粗化率在0.8um~1.0um,并且水洗充分干凈.小结从以上追踪结果可知,"凹坑"产生的根本原因是光成像图形转移工序保养不彻底造成.当然,产生"凹坑" 地原因还有很多.解决问题的途径也不一样.不管如何,作好图形电镀线点点滴滴的维护保养,控制也是至关重的.。

多物理场耦合研究电感线圈电镀铜

多物理场耦合研究电感线圈电镀铜苏世栋;冀林仙【摘要】采用多物理场耦合方法构建了电感线圈电镀铜模型,通过有限元分析获得了电感线圈电镀铜过程中铜离子浓度分布、线圈表面电流密度与镀层分布状况,探讨了象形阳极与阴阳极距离对镀层厚度分布的影响.数值模拟结果表明,采用象形阳极与绝缘挡板有助于提高线圈表面镀层的均匀性.当阴阳极距离较小时,采用象形阳极电镀铜,镀层极差降低为0.21μm,COV减小为0.5%.随着阴阳极距离的增加,镀层极差增大到9.5%,需要增加绝缘挡板来提高镀层均匀性.此时,镀层极差为0.14μm,标准偏差COV值为0.4%.%A model for copper electroplating on inductance coil was established based on multi-physics coupling technology. The characteristics of Cu2+ concentration distribution, current density of coil surface and thickness of copper electrodeposition were obtained by finite element analysis. The effects of pictographic anode and distance between anode and cathode on coating thickness distribution were discussed. The numerical simulation results show that it is helpful to improve the uniformity of copper electrodeposition on coil surface by adding pictographic anode and insulating baffle. When the distance between cathode and anode is small, the range of plating thickness is 0.21μm, the value of COV (Coefficient of Variance) is 0.5% under the condition of electroplating copper with pictographic anode. With the increase of the distance between the anode and cathode, coating thickness increased to 9.5%, and an insulating baffle was needed to improve the uniformity ofcoating. Then, the range of plating thickness is0.14 μm, the value of COVis 0.4%.【期刊名称】《电子元件与材料》【年(卷),期】2017(036)010【总页数】7页(P46-52)【关键词】印制电路;电感线圈;电镀铜;多物理场耦合;象形阳极;有限元分析【作者】苏世栋;冀林仙【作者单位】运城学院物理与电子工程系,山西运城 044000;运城学院物理与电子工程系,山西运城 044000【正文语种】中文【中图分类】O441.4信息、通讯、消费性电子产品制造业的快速发展,使电子产品日新月异,并朝着体积小、质量小、多功能的方向不断发展[1-2]。

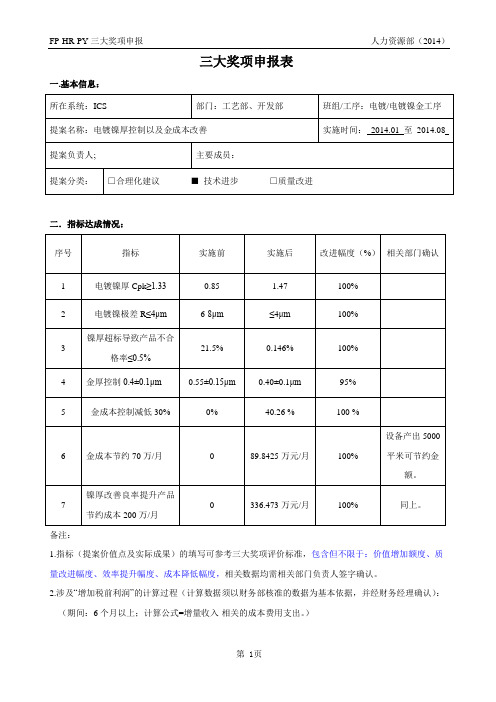

电镀镍厚控制以及金成本改善.

三大奖项申报表一.基本信息:二.指标达成情况:备注:1.指标(提案价值点及实际成果)的填写可参考三大奖项评价标准,包含但不限于:价值增加额度、质量改进幅度、效率提升幅度、成本降低幅度,相关数据均需相关部门负责人签字确认。

2.涉及“增加税前利润”的计算过程(计算数据须以财务部核准的数据为基本依据,并经财务经理确认):(期间:6个月以上;计算公式=增量收入-相关的成本费用支出。

)三.周边评价备注:周边评价部门为该提案实施以及应用中相关关联部门。

四.审核意见(详细内容请参阅总结报告):电镀镍厚控制以及金成本改善总结报告1.背景ICS封装基板电镀镍-金产品中,95%以上的客户对电镀镍金厚度以及手指宽度、间距提出明确的品质管控要求。

如手指宽度控制因客户工程文件要求存在一定制作难度以及前工序(蚀刻)制成能力偏差,这对电镀镍金工序的电镀镍厚控制提出更高要求。

ICS电镀镍金线设备初期电镀镍厚极差为6-8μm,这很难满足客户对电镀镍金产品的品质要求,使得前期电镀镍金产品因镍厚不合格产生大量报废,特殊产品报废率可达60%,制程能力低下。

因此改善电镀镍厚控制,提高镀镍制程能力具有积极的意义。

在封装基板生产过程中,金厚控制范围为0.3-1.0μm,金成本在整个ICS物料消耗中占据很大的组成部分。

因此通过提高镀金均匀性、优化板边设计、控制金厚以及减少金盐带出等手段对金成本控制具有非常显著以及积极的效果。

2.目标通过优化改善电镀镍厚控制,提高产品合格率,使得电镀镍极差R≤4μm,电镀镍镍金产品因电镀镍厚超标的报废率由最高50-60%降低至0.25%。

金成本减低30%左右。

实现电镀参数导入程序化、自动化,减少人为导入的错误,提高生产效率。

3.过程实施3.1电镀镍厚控制对电镀镍厚控制过程需结合电镀镍均匀性调整、飞巴与挂具间电镀镍厚偏差以及参数优化等过程。

其镍厚控制改善思路如下:3.1.1 电镀镍均匀性改善电镀镍均匀性提升主要通过改善设备几何尺寸、设计阴极挡板、阴极排布以及阴阳极相关位置。

电镀均匀性改善研究

电镀均匀性改善研究2008-8-15 17:02:04 源自: 作者:摘要:本文针对图形电镀线电镀均匀性不佳的状况,通过一系列细致的试验分析,完成了在缸体上部增加特定尺寸的阳极挡板,以及在浮槽侧面进行大小、间距适宜的开孔等改造措施,改善了该线的电镀均匀性,使其均匀程度由改善前的20.8%,提高到改善后10.3 %。

关键词:电镀均匀性;阳极挡板;浮槽1. 前言随着PCB 不断向轻、薄、短小高密度方向发展,给很多设备和生产工艺带来了更高要求。

其中线路板图形间距越来越小,而孔铜厚要求却越来越高,给图形电镀均匀性就提出了新的挑战。

我司旧图形电镀线在加工整板细密线路(最小间距3.5mil)的板子时,板边细密线路容易夹膜,导致报废。

且发现板上有规律的铜厚分布不均匀,导致半成品切片判断孔铜失误,不能有效对半成品的铜厚作出准确判断。

故决定对此线电镀均匀性进行专门测试分析,组织进行改善。

2. 测试说明:1)整个图形电镀线的电镀窗口为52×24(Inch2),深方向为24Inch;2)采用生益FR-4 板材,尺寸:24X24Inch2,2 块此尺寸板并排放置于电镀缸中进行测试;3)测试板距溶液表面0-1Inch,悬挂于溶液中间,不加分流条,22ASF,电镀60 分钟;4)深方向是指板子从镀液表面到溶液底部的方向;水平方向是指与阴极杆平行的方向;5)测量仪器采用的是德国Fischer 公司感应式表面铜厚测试仪,测量误差<0.5um;6)测试时每2×2Inch2 取一个测量点,用电镀后的铜厚减去电镀前的铜厚进行统计分析;7)因每进行一次测试,2 块板两面共有576 个数据,限于篇幅,文中只展示每次正面测量所作出示意图。

7 次测试的数据,作为附件,另附一个文档。

3. 改善目标:1)总体COV(标准偏差与总体平均值的比值百分数)<11%(业界参考标准为<=8-12%);2)深方向镀铜厚度平均差异(深方向极差)<3um。

边缘蚀刻快,中间蚀刻慢的边缘效应

边缘蚀刻快,中间蚀刻慢的边缘效应

边缘蚀刻快,中间蚀刻慢的边缘效应,是一种在制造业中常见的现象。

它指的是当物体的边缘进行蚀刻时,边缘部分的蚀刻速度比中间部分的蚀刻速度要快,从而造成边缘部分比中间部分更薄的现象。

这种边缘效应在很多领域都有应用,比如微电子制造中的光刻工艺,以及纳米技术中的纳米蚀刻等。

在这些应用中,边缘效应的存在是不可避免的,因为它与物体形状、材料特性等因素有关。

边缘蚀刻快,中间蚀刻慢的边缘效应的原因可以通过分子扩散理论进行解释。

在蚀刻过程中,蚀刻剂分子从溶液中扩散到物体表面,并与物体表面发生反应。

而由于物体表面积的不均匀分布,边缘部分的表面积相对较大,因此蚀刻剂分子在边缘部分的扩散速度比中间部分要快。

为了减小边缘效应对制造过程的影响,人们采取了一些措施。

例如,在光刻工艺中,可以使用较小的曝光剂量和较短的曝光时间,以减小边缘效应的程度。

此外,还可以调整蚀刻剂的浓度和蚀刻时间,以达到更加均匀的蚀刻效果。

边缘蚀刻快,中间蚀刻慢的边缘效应是制造业中一个重要的问题,对于制造高精度和高质量的产品具有重要意义。

通过深入研究边缘效应的机理,并采取有效的措施来减小边缘效应的影响,可以提高制造过程的稳定性和可控性,从而提高产品的质量和性能。

边缘蚀刻快,中间蚀刻慢的边缘效应是制造业中常见的现象,它与物体形状、材料特性等因素有关。

通过深入研究边缘效应的机理,并采取有效的措施来减小边缘效应的影响,可以提高制造过程的稳定性和可控性,从而提高产品的质量和性能。

图形电镀中渗镀、短路、断路成因的分析及对策

表 1

槽 位 序号 A A B B C C D D E E F F 上mil 下mil 上mil 下mil 上mil 下mil 上mil 下rail 上mil 下mil 上mil 下mil

(2)线 路 上针 孔 明显 、异常 ,经 化 验 分析 发 现 镀 铜 液有 油 污 点 ,可 确认 为活 性 炭 处理 存 在 异常 。

(3)规 则 断 路 ,大面 积 发 生 的主 要 原 因为 曝光 不 良:点状 断 路 的主 要 原 因为 显 影段 膜 屑 残 留(膜 屑 来 源板 边 干 膜 或 湿膜 残 留 ,带 入显 影 水洗 段 )。

(b)取 样 方 式 为 每 槽 前 Fly Bar均 匀取 六 点 ,具体 如 下 :

5 图形 电镀 槽液 分散 能 力调 查试 验报 告 (附 录)

(1) 宗 旨:针 对经 过 活 性 炭 处理 后 的图形 电镀铜 槽通过切片的方法收集数据 ,进行分散 能 力 的调 查 实验 报 告 ,以作 为 生产 过程 中调 整 作业条件的依据 ,从而 保汪 PCB产品品质

(2) 目的 :

① 获取 图形 电镀铜槽液的分散能 力数据 : ② 分析 各槽的 电镀 均 匀 度 ,控 制 夹膜 造 成 短 路 问题 发 生 。

-< ∞ ≯

前FLYBAR示意

夹点 边条 浮槽

(c)每个 样 进 行 灌胶 做ห้องสมุดไป่ตู้徽 切片 ,每个 切片 读六点数据 ,具体测量点如图 l:

2 现场 生 产 过程 发生 的不 良现 象 ,试 验 及 结 论 (嘉 兴 上村 电子有 限公 司)

(1)小 点状 渗 镀 异常 明显 ,‘经 检 验 分 析发 现 原板 上 有 油 污污 点 (水破 试 验小 于 4秒 ),可 确认 为 前处 理 存 在异 常 , 电镀 电流过 大 。

名词解释-边缘效应

名词解释-边缘效应

边缘效应(edge effect)指的是在实验、观察、测量等过程中,由于样品边缘和背景之间的界面位置不同,而产生的不均匀效应。边缘效应通常会导致样品边缘处的测量值明显偏高或偏低,影响实验的精度和准确性。

在科学研究和工程技品时,由于样品与背景的不同,边缘部分的光照相对强烈,导致边缘部分显得更亮或更暗;在电学测量中,由于电场分布不均匀,导致电势分布、电流密度等物理量在边缘处出现异常。

电镀过程中的屏蔽效应

电镀过程中的屏蔽效应全文共四篇示例,供读者参考第一篇示例:电镀是一种常见的表面处理工艺,通过在金属表面涂上其他金属层,以增强金属的性能、耐腐蚀性和美观度。

在电镀过程中,常常会出现屏蔽效应,即有些部分的金属很难被电镀,造成金属层的不均匀性。

今天我们就来探讨一下电镀过程中的屏蔽效应。

要了解电镀屏蔽效应的原因。

在电镀过程中,金属离子通过电解质导电,沉积到工件表面形成金属层。

由于工件表面的形状、大小和位置的不同,有些部分很难被金属离子所覆盖,造成了屏蔽效应。

有些凹陷处或细小的孔洞很难被金属覆盖,使得金属层的厚度不均匀。

在拐角处或者是曲线处,由于电场分布的原因,金属的沉积也不均匀,导致屏蔽效应的产生。

对于电镀屏蔽效应,需要有一些对策来解决。

可以通过设计工件的形状,避免出现凹陷或者细小的孔洞,使得金属离子能够较好地覆盖整个表面。

可以调整电解液的成分和温度,使得金属离子的沉积速度更加均匀,减少屏蔽效应的产生。

也可以通过使用专门的工艺设备,如遮盖剂或者电场分布器,来提高金属的沉积均匀度,减少屏蔽效应的影响。

还需要注意一些其他因素对电镀屏蔽效应的影响。

金属表面的清洁度和粗糙度会影响金属离子的沉积速度和均匀性,进而影响屏蔽效应的产生。

电镀过程中的电流密度和电场分布也会影响金属层的均匀性,需要进行合理的调节。

电解液的流速和搅拌方式也会影响金属沉积的均匀性,进而影响屏蔽效应的出现。

电镀过程中的屏蔽效应是一个常见的问题,但是可以通过合理的设计和选择工艺参数来解决。

通过对工件形状、电解液成分、工艺设备的调整和其他因素的考虑,可以减少屏蔽效应的影响,得到更加均匀和美观的金属层。

希望以上内容能够对大家有所帮助,如果有更多关于电镀屏蔽效应的问题,请继续关注我们的文章。

谢谢!第二篇示例:电镀是一种常见的表面处理过程,用于给材料表面镀上一层金属或合金以增加其硬度、耐腐蚀性和美观性。

在电镀过程中,往往会出现屏蔽效应,影响镀层的均匀性和质量。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

115

PCB Information

MA Y 2019 NO.3

图形电镀边缘效应的研究

文/广州兴森快捷电路科技有限公司 廉泽阳 陈蓓 李艳国

图形电镀生产中常存在铜厚、镍厚不均匀等问题,因整板高、低电流区差异造成板面与金属化孔壁镀层厚度差较大,部分孤立图形铜厚偏厚,给后续加工带来undercut、线宽公差过大等问题[1-4]。

目前,对于图镀镀层厚度不均所产生原因分析与机理研究尚少,本文依据静电场原理,对电镀边缘效应产生的过程和影响因素进行研究,针对不同图形电荷分布提出不同模型。

全板电镀的电力线分布类似于电容器静电场分布,中间电力线趋于均匀平行,边缘电力线趋于密集。

而图形电镀电力线分布则是根据图形分布情况重新分布,如图1、图2所示。

图形电镀电荷分布与电流密度、孤立距离和阴阳极距离有关。

根据每个因素影响的不同,建立如图3、4、5所示模型:

【摘 要】本文以理论分析为基础,依据静电场原理,对电镀边缘效应产生的过程和影响因素进行了研究。

根据不同图形的分布,建立了不同图形电荷分布模型。

研究发现,边缘效应的宽度与阴阳极距离有关,且符合X/d=0.5(X为阴阳极距离,d为边缘效应宽度);边缘效应的高度与电流密度有关,电流密度越大,边缘效应高度越大。

【关键词】图形电镀;边缘效应;阴阳极距离;静电场原理;电力线

第一作者简介:廉泽阳,男,硕士研究生,广州兴森快捷电路科技有限公司技术中心研发工程师。

0引言

1 图形电镀边缘效应模型建立

图1 全板电镀电力线分布情况

图2 图形电镀电力线分布

1.1 电流密度的影响

随着电流增大,阴极表面e -逐步增多,e -与e -之间产生相互排斥的库仑力(F=kQq/r 2),使得边缘e -居多,而阴阳极之间的e -与e +的吸引力使之趋于平衡,最终电力线分布表现为边缘密集(如图3)。

可见,边

缘效应的大小与电流密度有关。

2019年5月第3期

116

由图8可以看出,随着孤立线和大铜面距离的变化,孤立线的的铜厚依次增加。

当距离达到60mm 时,孤

图8 不同电流密度和不同距离条件下,孤立线与大

铜面铜厚比值趋势

2.1 电流密度对边缘效应的影响

分别采用电流密度为5、7、13ASF 对整板进行电镀,采用面铜测试仪对板面铜厚进行测量,剔除基铜值,整理结果如图6所示。

(边缘效应极限值=边缘铜厚/平均铜厚,边缘效应极限值即边缘效应高度)。

不同电流密度的边缘效应极限值满足:y= 0.03533x+1.13683(y:边缘效应极限值=边缘铜厚/平均铜厚,x:电流密度/ASF)。

实验结果表明,电流密1.3 阴阳极距离的影响

利用施瓦兹—克利斯多菲变换,可得出平行板电容器的静电场中的电势,进而得出边缘处的电荷分布、电场分布和电势分布。

当阴阳距离较小时,部分吸引力可抵消表面排斥力以达到平衡,当阴阳极距离增大,吸引力减小,排斥力增大,边缘电荷分布增多,边缘效应增大(如图5所示)。

进而可得X/d=0.5(X:边缘效应宽度 d:阴阳极距离)。

2模型验证与结果

图3 电荷分布情况

图4 图形电镀边缘效应产生过程

图5 不同阴阳极距离条件下电荷分布情况

图6 不同电流密度条件下边缘效应

图7不同电流密度边缘效应极限值

1.2 孤立距离影响

当图形与图形之间距离较近时,图形内表面e -相互排斥,同时,图形与图形边缘e -因近距离而产生排斥力,使得接近图形边缘的电子数少于图形另一边缘电子数。

随着距离再增大,达到各自孤立状态,图形与图形之间电荷不受排斥力影响,图形左右边缘电子数相等且平衡(如图4所示

)。

度越大,电流越大,阴极表面电荷越多,阴极边缘集中电荷越多,边缘效应越大。

同时,边缘效应宽度(距

板边距离)为固定值10cm,如图7所示。

2.2 孤立距离的界定

为统一面铜厚度,分别采用不同电流密度进行电镀。

采用金相显微镜对镀层厚度进行测量,结果统计如图8所示。

117

PCB Information

MA

Y 2019 NO.3本文依据静电场原理,对图形电镀边缘效应产生的过程和影响因素进行研究。

研究结果表明,图形电镀边缘效应跟图形间距离、电流密度和阴阳极距离有关。

边缘效应的宽度由阴阳极距离决定,符合X/d=0.5(X:边缘效应宽度,d:阴阳极距离);边缘效应

立线铜厚和大铜面铜厚的比值趋于平缓。

这是由于随着距离的增加,图形表面排斥力大于图形与图形边缘电荷排斥力,使得边缘铜厚越厚,当达到一定孤立距离时,图形与图形边缘电荷不发生排斥力作用,图形表面电荷达到平衡,铜厚不再增加。

因此,可界定出,不同电流密度条件下,图形完全孤立的极限距离约为60mm。

2.3 阴阳极距离对边缘效应的影响

采用电镀参数为7ASF *150min 对不同阴阳极距离条件下的整板进行电镀,采用面铜测试仪对板面铜厚进行测量,剔除基铜值,整理结果如图9、10所示。

本实验结果也符合X/d=0.5(X:边缘效应宽度,d:阴阳极距离)。

因此,缩短阴阳极距离,可减小边缘效应宽度,从而有效提高图形电镀均匀性。

图9 两极26cm距离下,边缘效应宽度和边缘效应高度趋势图

图10 两极20cm

距离下,边缘效应宽度和边缘效应高度趋势图

3 总结

的高度随电流密度的增加而增大,随距离的增加而增大。

参考文献

[1] 钟姚, 吴寿军, 汪海燕. 图形电镀均匀性改善研究[J]. 印制电路资讯, 2015(6):105-107.

[2] 李学明. 图形电镀铜层厚度的均匀性-辅助电极的位置在图形的周边缘[J]. 电子电路与贴装, 2005(3):4-10.

[3] 陈世金. 基于电镀均匀性改善的一些创新与改进[J]. 印制电路信息, 2016, 24(3):38-41.

[4] 田玲, 王卫文, 李志东. 不同间距精细线路图镀铜厚差异的探究[J]. 印制电路信息, 2009(S1):51-54.

[5] 谷长寿, 张颖, 曹力生. 平行板电容器边缘效应的研究[J]. 辽宁工业大学学报:自然科学版, 1994(3):80-82.

[6] Wan B Y, Zhang X S, Feng Q. Edge-effect in capacitance of non-parallel plate capacitor[J]. College Physics, 2012.

[7] 龙非池, 王慧. 基于Schwarz-Christoffel 变换的平板电容器电场电荷分布仿真[J]. 物理与工程, 2007, 17(06):25-27.

[8] Gilbarg D. A Generalization of the Schwarz-Christoffel Transformation[J]. Proceedings of the National Academy of Sciences, 1949, 35(35):609-12.

[9] Okubo T, Kodera T, Kondo K. Patterned copper plating layer thickness made uniform by placement of auxiliary grid electrode about ball grid arrays[J]. Chemical Engineering Communications, 2006, 193(193):1503-1513.

[10] 董久超, 王磊, 汤俊,等. 电镀层均匀性的Ansys 模拟与优化[J]. 新技术新工艺, 2008(11):114-117.

[11] 刘思远, 刘俊杰, 敖涛,等. 电流密度因子及其分布规律[J]. 应用基础与工程科学学报, 2004, 12(02):121-126.

[12] 刘太权. 电镀层均匀性的数值模拟及验证[J]. 电镀与环保, 2010, 30(02):11-13.

[13] 罗伟飞. 有关电镀均匀性问题[J]. 印制电路信息, 2012(10).。