(完整版)数字电子技术基础第五章答案

《数字电子技术基础》第五章习题(阎石主编,第四版)

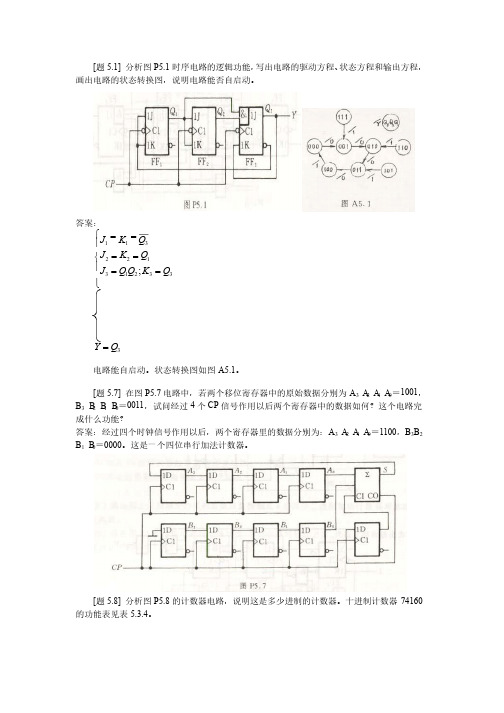

[题5.1] 分析图P5.1时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

画出电路的状态转换图,说明电路能否自启动。

答案:答案:11322131233;J K QJ K Q J Q Q K Q ì==ï==íï==î3Y Q =电路能自启动。

状态转换图如图A5.1。

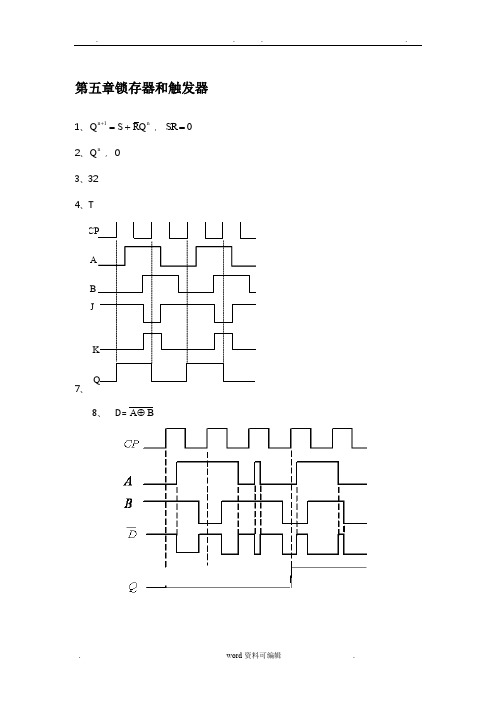

[题5.7] 在图P5.7电路中,若两个移位寄存器中的原始数据分别为A 3 A 2 A 1 A 0=1001,B 3 B 2 B 1 B 0=0011,试问经过4个CP 信号作用以后两个寄存器中的数据如何?这个电路完成什么功能?成什么功能?答案:经过四个时钟信号作用以后,两个寄存器里的数据分别为:A 3 A 2 A 1 A 0=1100,B 3B 2B 1 B 0=0000。

这是一个四位串行加法计数器。

这是一个四位串行加法计数器。

[题5.8] 分析图P5.8的计数器电路,说明这是多少进制的计数器。

十进制计数器74160的功能表见表5.3.4。

答案:答案:电路为七进制计数器。

图P5.8电路为七进制计数器。

[题5.9] 分析图P5.9的计数器电路,画出电路的状态转换图,说明这是多少进制的计数器。

十六进制计数器74LS161的功能表见表5.3.4。

答案:答案:。

这是一个十进制计数器。

电路的状态转换图如图A5.9。

这是一个十进制计数器。

[题5.10] 试用4位同步二进制计数器74LS161接成十二进制计数器,标出输入、输出端。

可以附加必要的门电路。

74LS161的功能表见表5.3.4。

答案:答案:见图A5.10 [题5.11] 试分析图P5.11的计数器在M=1和M=0时各为几进制。

74160的功能表见表5.3.4。

答案:答案:M=1时为六进制计数器,M=0时为八进制计数器。

时为八进制计数器。

[题5.16] 图P5.16电路是由两片同步十进制计数器74160组成的计数器,试分析这是多少进制的计数器,两片之间是几进制。

数字电子技术基础 第五章、第六章习题参考答案

第五章锁存器和触发器

1、1n n Q S RQ +=+, 0SR =

2、n

Q , 0 3、32

4、T

7、

A B

J

4-13题解图

8、

D=B A ⊕

第六章时序逻辑电路

1、输入信号,原来的状态

2、异

3、n

4、4,4

5、反馈清零、反馈置数

6、N

7、状态方程和输出方程:

8、激励方程

状态方程

输出方程

Z=AQ1Q0

根据状态方程组和输出方程可列出状态表,如表题解6.2.4所示,状态图如图题解6。

2.4所示。

14、

15、状态方程为:

24、解:74HC194功能由S1S0控制

00 保持,01右移10 左移11 并行输入

当启动信号端输人一低电平时,使S1=1,这时有S。

=Sl=1,移位寄存器74HC194执行并行输人功能,Q3Q2Q1Q0=D3D2D1D0=1110。

启动信号撤消后,由于Q。

=0,经两级与非门后,使S1=0,这时有

S1S0=01,寄存器开始执行右移操

作。

在移位过程中,因为Q3Q2、

Q1、Q0中总有一个为0,因而能

够维持S1S0=01状态,使右移操作

持续进行下去。

其移位情况如图题

解6,5,1所示。

该电路能按固定的时序输出低电平

脉冲,是一个四相时序脉冲产生电

路。

数电第五章习题答案 .doc

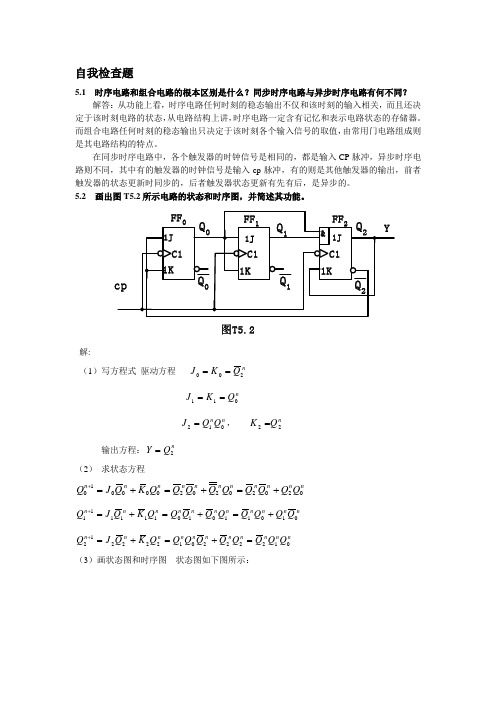

自我检查题5.1 时序电路和组合电路的根本区别是什么?同步时序电路与异步时序电路有何不同?解答:从功能上看,时序电路任何时刻的稳态输出不仅和该时刻的输入相关,而且还决定于该时刻电路的状态,从电路结构上讲,时序电路一定含有记忆和表示电路状态的存储器。

而组合电路任何时刻的稳态输出只决定于该时刻各个输入信号的取值,由常用门电路组成则是其电路结构的特点。

在同步时序电路中,各个触发器的时钟信号是相同的,都是输入CP 脉冲,异步时序电路则不同,其中有的触发器的时钟信号是输入cp 脉冲,有的则是其他触发器的输出,前者触发器的状态更新时同步的,后者触发器状态更新有先有后,是异步的。

5.2 画出图T5.2所示电路的状态和时序图,并简述其功能。

图T5.2解:(1)写方程式 驱动方程 nQ K J 200==n Q K J 011==n n Q Q J 012=, n Q K 22=输出方程:nQ Y 2= (2) 求状态方程nn n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 02020202000010+=+=+=+ n n n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 01011010111111+=+=+=+ n n n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 01222201222212=+=+=+(3)画状态图和时序图 状态图如下图所示:101时序图如下图所示:CP Q 0Q 1Q 25.3 试用边沿JK 触发器和门电路设计一个按自然态序进行计数的七进制同步加法计数器。

解:(1)状态图如下图:(2)求状态方程、输出方程CQ Q Q n n n /101112+++的卡诺图如下图所示:输出方程为nn Q Q C 12=状态方程:n n n n n Q Q Q Q Q 120112+=+ n n n n n n Q Q Q Q Q Q 0120111+=+ n n n n n Q Q Q Q Q 120110+=+驱动方程:n n n n n n n n n n n n n n n Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q 0122120121220112)(++=++=+n n n n n n Q Q Q Q Q Q 1021011+=+n n n n n Q Q Q Q Q 0012101)(++=+与JK 触发器的特性方程 比较,可以得到驱动方程 n n Q Q J 012= 、 n Q K 12=n Q J 01= 、n n Q Q K 021=n n n n Q Q Q Q J 12120=+= 10=K(4) 无效状态转换情况 111/1000 能自启动(5) 逻辑图如下图所示:5.4 画出用时钟脉冲上升沿触发的边沿D 触发器组成的4位二进制异步加法计数器和减法计数器的逻辑电路图。

数字电子技术基础课后答案阎石第五版第一章第五章时序电路习题解答

第五章部分习题解答5.8S a =0011 , S b =1001 , S a ^ S b T S a 计数循环共有7个状态,故此电路是七进制计数器。

5.2 (在画出电路的状态转换图。

”后加:解:作功能说明。

”)1•写方程式输出方程:y=A Q 2nQ 1n驱动方程:r D i =AQ 2—n nn nD 2=AQ 2 Q i =A(Q 2 +Q i ) 状态方程:n+1 —nQ i = D i =AQ 2 n+1n nQ 2= D 2= A(Q 2 +Q 1 )AQ :" Q-" Q 严Q 宀0 0 0 0 0 0 0 0 1 0 0 0 0 1 00 0 0 0 1 1 0 0 C 10 0 0 L 0 1 0 1 1 1 0 1 1 01 0 1 1 1 11 0 03. 从状态转换表画出状态转换图,如右图所示;4. 作功能说明:此电路是 “1111 ••序列检测器。

5.7四个CP 作用后,A 寄存器的状态:A 3A 2A 1A 0=1100 ; B 寄存器的状态:B 3B 2B i B o =OOOO 。

此电路是一个四位串行加法器(和不能超过四位) 。

5.24 (在原题后加: 用三片74LS194实现。

”)S i =高电平时,CP 上升沿作用后,将 升沿作用下,开始循环输出该序列。

0010110111 ”存入三片 74LS194内,S i =低电平后,在 CP 上5.4 (将图P5.4中的异或门改为同或门) 解: 1.写方程式_______n nn n输出万程:y=A Q 2 Q 1 A Q 2 Q 1 驱动方程: J 1=K 1=1 _____nJ 2=K 2=A O Q 1状态方程:n+1nnnQ 1 = J i Q i +K i Q 1 = Q 1QfQ 严 y000 i 110 0 1 00c0 1 0 0 1 0 0 1 I 1 0 0 1 0 00 I 0 1 0 1I 01 1 01 1 0 I 1 10 0 12.依次设定初态,代入方程求出次态和输出,如上表所示;再整理成状态转换图,如上图所示;3.作功能说明:此电路是同步两位二进制加/减计数器。

数字电子技术习题解答_杨志忠_第五章练习题_部分

教材:数字电子技术基础(“十五”国家级规划教材) 杨志忠 卫桦林 郭顺华 编著高等教育出版社2009年7月第2版; 2010年1月 北京 第2次印刷;第五章 集成触发器(部分习题答案)练习题5解答:(P213页)【5.1】、由与非门构成的基本RS 触发器,S D 和R D 端输入如图P5.1所示波形,试画出Q 和Q 的输出波形。

设触发器的初始状态为“0”。

解题思路:根据基本RS 触发器功能分段画图,并要注意与非门的基本RS 触发器是低电平有效。

当D S 和D R 端同时为有效低电平时,出现强制1态,有效电平同时撤去后(无效高电平)会出现不定态。

(不确定的状态,具体的状态取决两个与非门的翻转速度快慢)DS D RQ【5.2】、由或非门构成的基本RS 触发器,S D 和R D 端输入如图P5.2所示波形信号,试画出Q 和Q 的输出波形。

(设触发器的初始状态为“1”)。

解题思路:根据基本RS 触发器功能分段画图,并要注意或非门的基本RS 触发器是高电平有效,功能与与非门组成的RS 触发器功能相同。

当R D 和S D 端同时为有效高电平时,出现强制0态,有效电平同时撤去后(无效低电平)会出现不定态。

(不确定的状态,具体的状态取决两个与非门的翻转速度快慢)DS D RQ1≥1≥【5.4】、已知同步RS 触发器的输入CP,R 和S 的电压波形如题P5-4图所示的波形,试画出Q 和Q 的输出波形。

(设触发器的初始状态nQ =0)解题思路:同步钟控RS 触发器是电位型触发器(高电平敏感CP=1),在CP 有效触发期间的状态随输入信号发生变化,n 1n Q R S Q+=+,约束条件:RS=0,R=S=1时出现1Q Q 1n 1n ==++。

CPSQR【5.5】、已知同步D 触发器CP 和D 端的输入电压波形如P5.5图所示,试画出Q 端的输出波形。

(设触发器的初始状态nQ =0)解题思路:同步式触发器是电位型触发器(假定高电平敏感CP=1),在CP 有效触发期间的状态随输入信号发生变化,D Q1n =+。

万里学院数字电子技术第五章习题和参考答案

第五章习题1.题图5-1所示电路是用两片555组成的脉冲发生器,试画出Y 1和Y 2两处的输出波形,并标注要紧参数(参数只需估算)。

R 1C 133kR 233k 10题图5-12.题图5-2所示的555按时器组成的单稳态触发器及输入v I 的波形,求: (1)输出信号v O 的脉冲宽度T W ;(2)对应v I 画出v C 、v O 的波形,并标明波形幅度。

v I /V CC /3v Iv O题图5-23.由555按时器组成的多谐振荡器如图5-3所示,已知V DD =12V 、C =μF、R 1=15k Ω、R 2=22k Ω。

试求:(1)多谐振荡器的振荡周期;(2)画出的v C 和v O 波形。

v O /Vv C /V00tR Cv v OR题图5-34.由555按时器、3位二进制加计数器、理想运算放大器A 组成如题图5-4所示电路。

设计数器初始状态为000,且输出低电平V OL =0 V ,输出高电平V OH = V ,R d 为异步清零端,高电平有效。

(1)说明虚框(1)、(2)部份各组成什么功能电路?(2)虚框(3)组成几进制计器? (3)对应CP 画出v O 波形,并标出电压值。

题图5-45.用集成芯片555组成的施密特触发器电路及输入波形i v 如题图5-5所示,要求: (1)求出该施密特触发器的阈值电压V T +、V T -;(2)画出输出v o 的波形。

v I /V tv O /Vv v O题图5-56.用集成按时器555组成的电路及可产生的波形如题图5-6(a )、(b )所示,试回答: (1)该电路的名称;(2)指出(b )图中v C 波形是1~8引脚中,哪个引脚上的电压波形; (3)求出矩形波的宽度t W 。

v Iv O 0.3v v(a ) (b )题图5-67.题图5-7为简易门铃电路,设电路中元器件参数适合,R >>R 1,S 为门铃按钮,当按钮按一下放开后,门铃可响一段时刻。

《数字电子技术基础》课后习题及参考答案

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

《数字电子技术》黄瑞祥_第五章习题答案

第五章习题答案5-1分析题5-1图所示电路,画出时序图和状态图,起始状态Q0Q1Q2Q3=0001。

解时序图:CPQ0Q1Q2Q35-2分析题5-2图所示电路,画出电路的状态图。

解5-3 JK触发器组成5-3图所示电路。

分析该电路为几进制计数器,并画出电路的状态图。

该电路为五进制计数器5-4JK触发器促成如图5-4图所示的电路。

(1)分析该电路为几进制计数器,画出状态图。

= 1,电路为几进制计数器,画出其状态图。

(2)若令K3解:(1为7进制计数器5-5 试画出题5-5图(a)所示电路中B,C端的波形。

输入端A,CP波形如题5-5图(b)所示,触发器的起始状态为零。

1 5 6 123456789 10 11 12 13 14 15 16 17 18 19CPAQ0Q1BC5-6分析题5-6图所示电路,画出电路的状态图,说明电路能否自启动。

该电路能够自启动5-7 分析题5-7图所示电路,画出电路的状态图,说明电路能否自启动。

由状态图可见,电路图能够自启动5-8画出题5-8图所示电路的状态图和时序图,简要说明电路的基本功能。

解:状态图:功能分析:根据状态图可知:电路为三位格雷码发生器。

5-9 画出题5-9图所示的状态图和时序图。

解:状态图:时序图:5-10 如题5-10图所示,FF0为下降沿触发的JK触发器,FF1为上升沿触发的D触发器,试对应给定的RD ,CP,J,K的波形,画出Q,Q1的波形。

5-11图所示。

解:电路图:态图如题5-12图所示。

解:电路图如下:5-13 试用下降沿触发的边沿型JK触发器和与非门,设计一个按自然态序进行的七进制同步加法计数器。

解:电路图:5-14 试用上升沿触发的边沿型D触发器和与非门,设计一个按自然态序进行计数的十进制同步加法计数器。

解:电路图:5-15 试用JK触发器设计一个同步十进制计数器,要实现的状态图如题5-15图所示。

解:电路图如下:5-16 试设计一个具有如题5-16图所示功能的计数器电路,图中M为控制变量。