数字逻辑电路 答案作业3

数字逻辑课程三套作业及答案

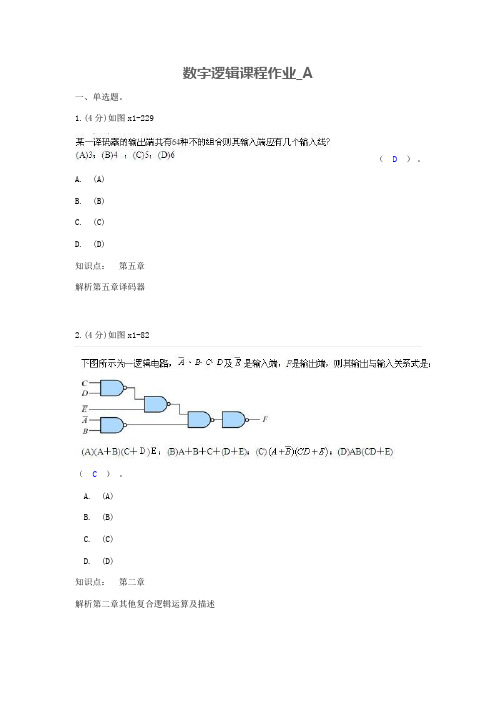

数字逻辑课程作业_A一、单选题。

1.(4分)如图x1-229(D)。

A. (A)B. (B)C. (C)D. (D)知识点:第五章解析第五章译码器2.(4分)如图x1-82(C)。

A. (A)B. (B)C. (C)D. (D)知识点:第二章解析第二章其他复合逻辑运算及描述3.(4分)N个触发器可以构成最大计数长度(进制数)为(D)的计数器。

A. NB. 2NC. N2次方D. 2N次方知识点:第九章解析第九章计数器4.(4分)n个触发器构成的扭环型计数器中,无效状态有(D)个。

A. A. nB.C. C.2n-1D. D.2n-2n知识点:第九章解析第九章集成计数器5.(4分)如图x1-293(A)。

A. (A)B. (B)C. (C)D. (D)知识点:第十一章解析第十一章数字系统概述6.(4分)如图x1-317(D)。

A. (A)B. (B)C. (C)D. (D)知识点:第二章解析第二章其他复合逻辑运算及描述7.(4分)EPROM是指(C)。

A. A、随机读写存储器B. B、只读存储器C. C、光可擦除电可编程只读存储器D. D、电可擦可编程只读存储器知识点:第十章解析第十章只读存储器8.(4分)如图x1-407(B)。

A. (A)B. (B)C. (C)D. (D)知识点:第十一章解析第十一章数字系统概述9.(4分)为实现将JK触发器转换为D触发器,应使(A)。

A. J=D,K=D非B. B. K=D,J=D非C. =K=DD. =K=D非知识点:第六章解析第六章各种触发器的比较10.(4分)一位8421BCD码计数器至少需要(B)个触发器。

A. 3B.C.D.知识点:第九章解析第九章计数器11.(4分)为把50Hz的正弦波变成周期性矩形波,应当选用(A)。

A. A、施密特触发器B. B、单稳态电路C. C、多谐振荡器D. D、译码器知识点:第六章解析第六章集成触发器12.(4分)下列描述不正确的是(A)。

数字电路第三章答案

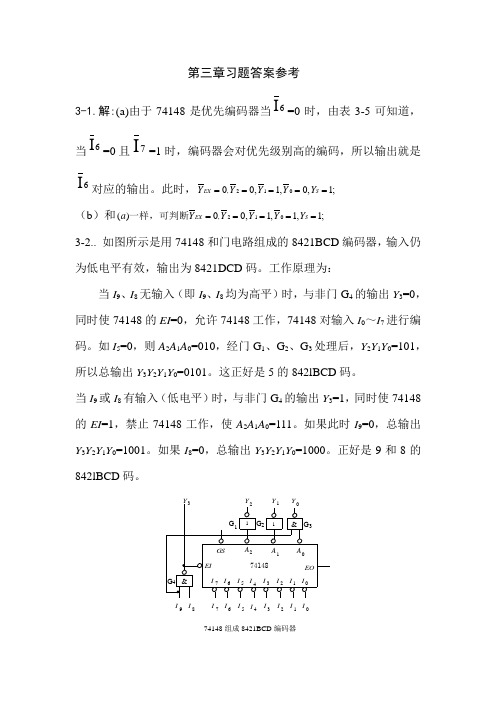

第三章习题答案参考3-1.解:(a)由于74148是优先编码器当6I =0时,由表3-5可知道,当6I =0且7I=1时,编码器会对优先级别高的编码,所以输出就是6I 对应的输出。

此时,,21000,1,0,1;EXS YY Y Y Y =====(b )和,210()00,1,1,1;EX S a Y Y Y Y Y =====一样,可判断3-2.. 如图所示是用74148和门电路组成的8421BCD 编码器,输入仍为低电平有效,输出为8421DCD 码。

工作原理为:当I 9、I 8无输入(即I 9、I 8均为高平)时,与非门G 4的输出Y 3=0,同时使74148的EI =0,允许74148工作,74148对输入I 0~I 7进行编码。

如I 5=0,则A 2A 1A 0=010,经门G 1、G 2、G 3处理后,Y 2Y 1Y 0=101,所以总输出Y 3Y 2Y 1Y 0=0101。

这正好是5的842lBCD 码。

当I 9或I 8有输入(低电平)时,与非门G 4的输出Y 3=1,同时使74148的EI =1,禁止74148工作,使A 2A 1A 0=111。

如果此时I 9=0,总输出Y 3Y 2Y 1Y 0=1001。

如果I 8=0,总输出Y 3Y 2Y 1Y 0=1000。

正好是9和8的842lBCD 码。

I I 457I 162I I I 03I I I 98I74148组成8421BCD 编码器3-3由于74147时优先编码器,优先级别为从9到1依次降低,而且是低电平有效,对照引脚图与真值表所以有(1)引脚为1.3.5时,看引脚5,即是8I,输出为:0111(2)引脚为2.4.10时,看引脚10,即是9I,输出为:0110(3)引脚为3.5.11时,看引脚5,即是8I,输出为:0111(4)引脚为4.10.12时,看引脚10,即是9I,输出为:0110(5) 引脚为5.10.13时,看引脚10,即是9I,输出为:0110(6) 引脚为10.11.13时,看引脚10,即是9I,输出为:01103-4(1)解:F1(A,B,C)=AB+C=1m+m3+m5+m6+m7=71m mmmm365实现的电路图如下:(2)解:F2(A,B,C)=m1+m2+m4+m5+m6=m6m1m5m2m4实现的电路图如下:(3)解:F 3(A,B,C )=∑)(5,3,1m =531m m m 实现的电路图如下:(4)解:F 4(A,B,C )=∑),(6,2,10m =6210m m m m 实现的电路图如下:(5)解:F 5(A,B,C )=∑),(6,5,30m =6530m m m m 实现的电路图如下:(6)解:F 6(A,B,C )=∑),(7,5,21m =7521m m m m 实现的电路图如下:(7)解:F7(A,B,C)=∑)m=72(7,6,3,mm2m3m6实现的电路图如下:(8)解:F8(A,B,C)=∑)m=7(7,4,1mm41m实现的电路图如下:3-5(1)解:F1(A,B,C,D)= ∑)9107811132m14,35,612,,,(14,,,,,,,=14mmmmmmmmmmmmm61091112131m823475实现的电路图如下:(2)解:F2(A,B,C,D)= )11102145m,(15,,,,=15mmmmm10142m115实现的电路图如下:=12mmmmmmm7896452m实现的电路图如下:(4)解:F4(A,B,C,D)= ∑)1011,61m4(14,,,,,,12=14mmmmmmm611120m1041实现的电路图如下:=15mmmmmmm911813472m实现的电路图如下:(6)解:F6(A,B,C,D)= ∑)4,27m9,,,,(11 =11mmmmm290m74实现的电路图如下:3-6 解:利用真值表,可以将Y 换成Y ,易得如下的表达式:A A A A Y123=A A A A Y 01231=A A A Y122=A A A Y 0123=A A A Y 0124= A A A Y125=A A A Y126=A A A Y 0127=A A Y38=A A Y 039=3-7解:根据题3-6的结果,F 1(A,B,C,D)= YY Y 52=A A A A A A A A A A 0120120123=A 3同理可得:F 2(A,B,C,D)= Y Y Y 641=A 3 F3(A,B,C,D)= Y Y Y 973=A A 03波形图如下:3-8解:波形如图所示:3-9解:图中的C in接地,为0,得全加器的函数式: S=B ABA+C o u t=AB+(A+B) C in得:1ACD BCDF=+2()() AB AB CD DF=++ 3-10设计如图所示:3-12解:(1)在八选一选择器74151中令A2=A ,A1=B ,A0=C 将F 1 (A,B)加多一个C ,换成F 1 (A,B,C)得F 1(A,B)= F1(A,B,C)=∑),,(543,2m 得D2=D3=D4=D5= 1 D0=D1= D6=D7=0(2)在八选一选择器74151中令A2=A ,A1=B ,A0=CF2(A,B,C)=∑),,(421,0m 得D0=D1=D2=D4=1 D3=D5=D6=D7=0(3)在八选一选择器74151中令A2=A ,A1=B ,A0=CF3(A,B,C)=∑),,(7,6,5,421m 得D1=D2=D4= D5=D6=D7=1 D0=D3= 0(4)在八选一选择器74151中令A2=A ,A1=B ,A0=CF4(A,B,C)=∑),,(6,5,4,321,0m 得D0=D1=D2=D3=D4=D5=D6=1 D7=0(5)在八选一选择器74151中令A2=A ,A1=B ,A0=C F4(A,B,C,D)=∑),,(13,12,1198,3m得D4= D6=1 D1= D5=D D0= D2= D3=D7=0(6)在八选一选择器74151中令A2=A ,A1=B ,A0=CF6(A,B,C)=∑),(6,5,30m 得D0= D3= D5=D6=1 D1=D2= D4=D7=0(7)在八选一选择器74151中令A2=A ,A1=B ,A0=CF7(A,B,C)=∑),(7,6,31m 得D1= D3= D6= D7=1 D0 =D2= D4= D5= 0(8)在八选一选择器74151中令A2=A ,A1=B ,A0=CF8(A,B,C,D)=∑),,(13,1110,54,3m得D2= D5=1 D1= D6 =DD0= D3= D4=D7=03-13解:设计如图所示:14解:输出的逻辑图如下:得逻辑表达式:Y=DBAA++CDBBA15解:如图所示:。

数字逻辑电路第三章部分答案

Hale Waihona Puke 根据与非与非式即可画出逻辑图其实将余3码直接当作一个二进制数十进制bcd代码再加3减去3就还原成为一位十进制数的bcd码设输出变量为ryg且低电平时点亮led即低电平输出有效

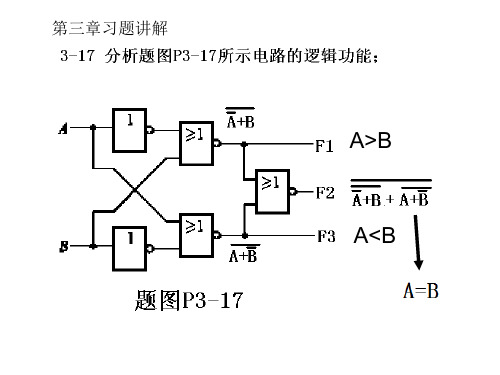

第三章习题讲解

A>B

A<B

同或电路

2线—4线译码电路

结果:

根据与非与非式即可 画出逻辑图

其实,将余3码直接当 作一个二进制 数(十进 制BCD代码再加3), 减去3就(还原)成为 一位十进制数的BCD码

8-1 MUX74151 功能表

功 能 表

S2 X 0 0 0 0 1 1 1 1 输入 S1 X 0 0 1 1 0 0 1 1 S0 X 0 1 0 1 0 1 0 1 使能 E 1 0 0 0 0 0 0 0 0 输出 Y 0 D0 D1 D2 D3 D4 D5 D6 D7 Y Y

设输出变量为R、Y、G,且低电平时点亮LED(即低电平输出有效)。 故可以列出真值表如下:

经变换 ,可以列出真值表如下:

列出最小项表达式 如下:

经变换 ,可以列出真值表如下:

列出最小项表达式 如下:

经变换 ,可以列出真值表如下:

卡诺图:

经变换 ,可以列出真值表如下:

根据简化后的与非与非式,选择合适的门电路 (与非门、OC输出门等)实现电路功能

11

D00 D D11 D D22 D D33 D D44 D D55 D D66 D D77 D

根据:

可得:

D0、D3、D4、D6为1; D1、D2、D5、D7为0。

则F的状态依次为: D0、D1、D2、D3、D4、D5、D6、D7、D0、D1………… 1 0 0 1 1 0 1 0 1 0 : D0、D3、D4、D6为1; D1、D2、D5、D7为0。

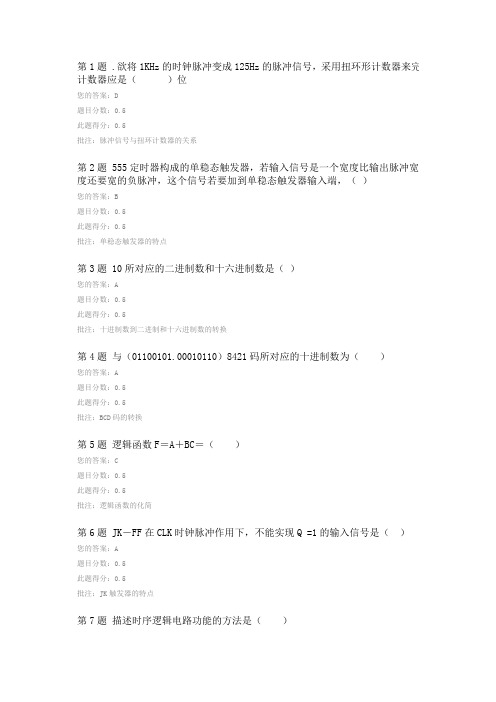

中石油 数字逻辑 在线作业三

第1题 .欲将1KHz的时钟脉冲变成125Hz的脉冲信号,采用扭环形计数器来完成计数器应是()位您的答案:D题目分数:0.5此题得分:0.5批注:脉冲信号与扭环计数器的关系第2题 555定时器构成的单稳态触发器,若输入信号是一个宽度比输出脉冲宽度还要宽的负脉冲,这个信号若要加到单稳态触发器输入端,()您的答案:B题目分数:0.5此题得分:0.5批注:单稳态触发器的特点第3题 10所对应的二进制数和十六进制数是()您的答案:A题目分数:0.5此题得分:0.5批注:十进制数到二进制和十六进制数的转换第4题与(01100101.00010110)8421码所对应的十进制数为()您的答案:A题目分数:0.5此题得分:0.5批注:BCD码的转换第5题逻辑函数F=A+BC=()您的答案:C题目分数:0.5此题得分:0.5批注:逻辑函数的化简第6题 JK-FF在CLK时钟脉冲作用下,不能实现Q =1的输入信号是()您的答案:A题目分数:0.5此题得分:0.5批注:JK触发器的特点第7题描述时序逻辑电路功能的方法是()您的答案:C题目分数:0.5此题得分:0.5批注:时序逻辑电路的定义第8题在下列集成芯片中,属于组合逻辑电路的是()您的答案:C题目分数:0.5此题得分:0.5批注:组合逻辑电路的定义第9题 RAM进行字扩展时,各芯的地址线应()您的答案:A题目分数:0.5此题得分:0.5批注:RAM扩展第10题 ROM存储器中的内容,当电源断电后又接通,其内容()您的答案:A题目分数:0.5此题得分:0.5批注:ROM存储器的特点第11题集电极开路门( OC 门)在使用时须在()之间接一电阻您的答案:C题目分数:0.5此题得分:0.5批注:OC门的使用第12题交流电流表或电压表的读数通常是指正弦交流电的()您的答案:B题目分数:0.5此题得分:0.5批注:电压表读数的定义第13题时序逻辑电路的一般结构由组合电路与()组成您的答案:B题目分数:0.5此题得分:0.5批注:时序逻辑电路的构成第14题能起到定时作用的电路是()您的答案:D题目分数:0.5此题得分:0.5批注:定时电路定义第15题下列门电路,不属于基本逻辑门的是()您的答案:A题目分数:0.5此题得分:0.5批注:逻辑门电路定义第16题只有稳态的电路是()您的答案:B题目分数:0.5此题得分:0.5批注:稳态电路的种类第17题不带缓冲输出的HCMOS电路系列是()您的答案:C题目分数:0.5此题得分:0.5批注:HCMOS电路特点第18题()触发器可以用来构成移位寄存器您的答案:D题目分数:0.5此题得分:0.5批注:触发器特点第19题下列触发器中没有约束条件的是()您的答案:D题目分数:0.5此题得分:0.5批注:触发器特点第20题 Moore型时序逻辑电路的输出( )。

《数字逻辑电路》试题及参考答案

《数字逻辑电路》在线作业参考资料一、单选题1. 一位8421BCD计数器,至少需要(B)个触发器A 3B 4C 5D 102. 在(A)的情况下,函数运算的结果是逻辑“1”A全部输入是“0” B任一输入是“0” C任一输入是“1” D全部输入是“1”3. 表示两个相邻脉冲重复出现的时间间隔的参数叫(A )A.脉冲周期B.脉冲宽度C.脉冲前沿D.脉冲后沿4. 只能读出不能写入,但信息可永久保存的存储器是(A)A.ROMB.RAMC.RPROMD.PROM5. 在(D)的情况下,函数Y=AB运算的结果不是逻辑“0”。

A全部输入是“0”B任一输入是“0”C任一输入是“1”D全部输入是“1”6. 下列哪些信号一定不属于数字信号(A)A.正弦波信号B.时钟脉冲信号C.音频信号D.视频图像信号7. 在(B)的情况下,函数Y=/(AB)运算的结果不是逻辑“0”。

A全部输入是“0”B任一输入是“0”C任一输入是“1”D全部输入是“1”8. 符合六变量m5的相邻最小项,有下列(C )说法成立A. 共有5 个相邻最小项B. m0、m4、m7、m13是它的相邻项C. 共有6 个相邻最小项D. m4、m21、m13、m38是它的相邻项9. 下列器件中,属于时序部件的是(A)A.计数器B.译码器C.加法器D.多路选择器10. 在n变量的逻辑函数F中,有(C )A. 若mi为1,则Mi也为1B. 若F所有mi为0,则F为1C. 若F所有Mi为1,则F为1D. F的任一最小项标记为mni( i = 1~2n )11. 半加器的逻辑功能是(A)A. 两个同位的二进制数相加B. 两个二进制数相加C. 两个同位的二进制数及来自低位的进位三者相加D. 两个二进制数的和的一半12. 1路—4路数据分配器有(A)A.一个数据输入端,两个选择控制端,四个数据输出端B.四个数据输入端,两个选择控制端,一个数据输出端C.一个数据输入端,一个选择控制端,四个数据输出端D.四个数据输入端,一个选择控制端,一个数据输出端13. 全部的最小项之和恒为(B)A.0B.1C.0或1D.非0非114. 对于四变量逻辑函数,最小项有(D)个A.0B.1C.4D.1615. 逻辑表达式A+BC=( C )A. ABB. A+CC. (A+B)(A+C)D. B+C16.在(A)的情况下,函数运算的结果不是逻辑“1”A全部输入是“0” B 任一输入是“0”C任一输入是“1” D全部输入是“1”17. 十进制数25用8421BCD码表示为(B )。

数字电路习题答案-第三章

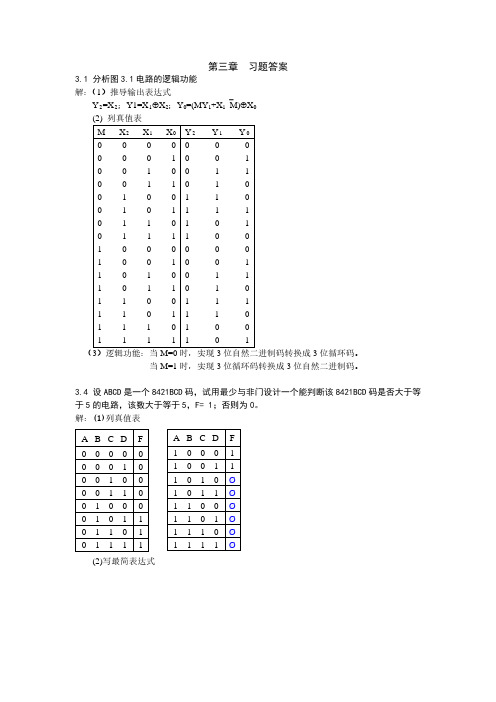

ABCD F

1000 1 1001 1 1010 Ø 1011 Ø 1100 Ø 1101 Ø 1110 Ø 1111 Ø

CD

AB

00

01

11

10

00

01

1

1

1

11

φ

φ

φ

φ

10

1

1

φ

φ

F = A + BD + BC=A · BD · BC (3)画逻辑电路,如下图所示:

D

&

B

&

C

所以,此时电路中存在功能冒险。

2.当 ABCD 从 1000 向 1101 变化时: 先判断是否有功能冒险,函数 F 的卡诺图如下图所

ABCD00 01 11 10 00 1

01 1

1

11 1 1 1 1

10 1 1 1

示: (1) F(1,0,0,0)=F(1,1,0,1); (2) 有 2 个变量同时变化; (3) AC对应的卡诺圈中全部为“1”; 所以,此时电路中不存在功能冒险。 再判断是否有逻辑冒险:

10 1 1 Ø = ABC·CD·AB·AD

画逻辑电路,如下图所示:

C&

D

A&

B

A&

D

A B

&

C

&

F

3.9 人的血型有 A、B、AB、O 四种。输血时输血者的血型与受血者的血型必须符合图 P3.4 中箭头指示的授受关系。试设计一个逻辑电路,判断输血者与受血者的血型是否符合上述规 定。 解:设00代表血型A、01代表血型B、10代表血型AB、11代表血型O。输血者的血型用逻辑 变量WX表示,受血者的血型用YZ表示,则由图中所指示的授受关系,列真值表:

电子科技大学14秋《数字逻辑设计及应用》在线作业3答案

B.正确

?

正确答案:A

A.错误

B.正确

?

正确答案:A

4.若AB=AC,一定是B=C。

A.错误

B.正确

?

正确答案:A

5.施密特触发器是一种双稳态电路。

A.错误

B.正确

?

正确答案:B

6.若AB+AC=1,则一定是A=1。

A.错误

B.正确

?

正确答案:B

7.施密特触发器可以用来鉴别脉冲幅度。

A.错误

B.正确

?

正确答案:B

8.若A+B=A+C,则一定是B=C。

A. 1位

B. 3位

C. 4位

D. 8位

?

正确答案:B

4.下列电路中,是时序电路的是

A.二进制译码器

B.移位寄存器

C.数值比较器

D.编码器

?

正确答案:B

5.属于组合逻辑电路的部件是()

A.编码器

B.寄存器

C.触发器

D.计数器

?

正确答案:A

6.一个多输入的或非门,输出为1的条件是

A.只要有一个输入为1,其余输入无关

A.数据选择器

B.数值比较器

C.加法器

D.触发器

?

正确答案:AB

2.逻辑代数的三种基本运算是

A.与

B.或

C.非

D.相除

?

正确答案:ABC

三,判断题

1.扭环形计数器都是不能自启动的。

A.错误

B.正确

?

正确答案:A

2.数据选择器是一种时序电路。

A.错误

B.正确

?

正确答案:A

3.任何一个逻辑函数的最简与或式一定是唯一的。

数字电路第三章习题答案

解: 根据题意,该控制电路有三个输入A,B,C; 三个输出G, Y,R。G代表绿灯,Y代表黄灯,R代表红灯。状态赋值如下:1 表示水在电极之上,0表示水在电极之下; 0表示灯亮,1表示灯灭。 按照题意列出的真值表如下。由真值表画出的卡诺图:

数字电路第三章习题答案

3-11

GABAB YABCABC RC

F10 C DAB

F30 CD AB

F20 C DAB

F40 CDAB

解:5号译码器因 E5 0 ,始终处于译码器状态。而1号,2号,3号,4号译码器要受

5号译码器输出控制。(1)当 CD=00时, 只1号译码器译码,其他译码器不译码。当

CD=01时, 只2号译码器译码。(3)当 CD=10时, 只3号译码器译码。当 CD=11时,

Y 1AB A C (B C ) m (1,2,3,7) Y2ABAB m (2,3,4,5)

Y3(AB)(AC) m (0,1,5,7)

Y4ABC ABC m(0,7)

解:先进行化简变换为最小相之和形式:

Y 1 A A B B A C C A A B B C A B C A B C C A BC

数字电路第三章习题答案

3-13 F ( A 3 B 3 ) • ( A 2 B 2 ) A 1 (B 1 ) A 0 ( B 0 )

A和B相等的条件是:最高位相等并且低三位也相等。 所以有:

(A3B3)1 (A 2 B 2 )A 1 ( B 1 )A 0 ( B 0 ) 1 可以把 (A3B3)作为74138待分配的数据,加载到G1控 制端;A2A1A0,B2B1B0分别作为138和151的通道选

数字电路第三章习题答案

3-5 列出题示逻辑图的真值表。图中T331为输出低电平有效的8421码译码器。

数字电路与数字逻辑3组合逻辑电路习题解答

3 33习 题1.解: CO =AB +BC +ACAC BC AB C B A ABC CO C B A ABC S +++++=+++=)()(AC BC AB C B A ABC )(+++=AC BC AB C AC BC AB B AC BC AB A ABC +++= A B AB C AC C A B C BC B A ABC +++= C B A C B A C B A ABC +++=真值表A B C S CO A B C S CO 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 011111111电路功能:一位全加器,A 、B 为两个加数,C 为来自低位的进位,S 是相加的和,CO 是进位。

2.解:处于工作状态的译码器C 、D 应输入的状态C D ① 0 0 ② 0 1 ③ 1 0 ④11逻辑功能:由74LS139构成的4线—16线译码器3.解:由图可见,74HC138的功能扩展输入端必须满足E 1=1、032==E E 才能正常译码,因此E 1=A 3=1;542A A E =,即A 4=1,A 5=1; 0763=+=A A E ,即A 6=0,A 7=0。

所以,该地址译码器的译码地址范围为A 7A 6A 5A 4A 3A 2A 1A 0=00111A 2A 1A 0=00111000~3 3400111111,用十六进制表示即为38H ~3FH 。

输入、输出真值表如表P3.3-1所示。

表3.3-1 地址译码器的真值表4.解:由图写出逻辑函数并化简,得02460246L Y Y Y Y Y Y Y Y A BC ABC ABC ABC C ==+++=+++=5. 解:F AB B C A B C AB C ABC ABC =+=+++3 359.解:4选1数据选择器的逻辑表达式为: 301201101001D A A D A A D A A D A A Y +++=将A 1=A ,A 0=B ,D 0=1,D 1=C ,C D =2,D 3=C 代入得 ABC C B A BC A C B A C B A ABC C B A BC A B A Y ++++=+++=根据表达式可画出波形图:C ABL10.解:(1)写出逻辑函数表达式: C AB C B A BC A C B A C B A L ++++=(2)用卡诺图化简3 3611.解:567m m m ABC C B A ABC C AB AC AB L ++=+++=+=13. 解:D C B D C D D C A D C B D C C A F +++=++=)(0⋅+++=+++=CD D C D C A D C AB D C B D C D C A D C A令A 1=C ,A 0=D ,AB D =0,A D =1,D 2=1,D 3=0 连线图:14. 解:3 371。

数字逻辑电路习题解答3

第3章习题解答 章习题解答

1 分析图 所示电路,写出电路输出Y1和Y2的逻辑函数表达式, 分析图3-1所示电路,写出电路输出 的逻辑函数表达式, 所示电路 列出真值表,说明它的逻辑功能。 列出真值表,说明它的逻辑功能。

1

CT74151 D7 D6 D5 D4 D3 D2 D1 D0

15 用一片集成 线—8线译码器 用一片集成3线 线译码器 线译码器CT74138和必要的门电路 和必要的门电路 实现下列多输出组合逻辑函数。 实现下列多输出组合逻辑函数。

F1=ABC+A(B+C) F2=AB+AB F3=(A+B)(A+C) F4=ABC+ABC F1=ABC+A(B+C)=ABC+AB+AC=m1+m2+m3+m7 =m1 · m2 · m3 · m7 =Y1 · Y2 · Y3 · Y7 F2=AB+AB=m2+m3+m4+m5=m2 · m3 · m4 · m5 =Y2 · Y3 · Y4 · Y5 F3=(A+B)(A+C)=BC+AB+AC=m2+m3+m4+m6 =m2 · m3 · m4 · m6 =Y2 · Y3 · Y4 · Y6 F4=ABC+ABC=m0+m7=m0 · m7 = Y0 · Y7

F=F1=F2=CIAB+CIAB+CIAB+CIAB=m1+m2+m4+m7 =m1 · m2 · m4 · m7 =Y1 · Y2 · Y4 · Y7 CO1=CIAB+CIAB+CIAB+CIAB=m3+m5+m6+m7 =m3 · m5 · m6 · m7 =Y3 · Y5 · Y6 · Y7 CO2=CIAB+CIAB+CIAB+CIAB=m1+m4+m5+m7 =m1 · m4 · m5 · m7 =Y1 · Y4 · Y5 · Y7 CO=KCO1+KCO2

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第3章作业答案

3-11图P3-11是用或非门构成

的基本RS触发器。

已知S D和R D的波

形,试画出输出端Q和Q的波形。

解:如右图。

3-12 图P3-12是用与非门构成

的基本RS触发器。

已知D

S和D

R的

波形,试画出输出端Q和Q的波

形。

解:如右图。

3-18 图P3-18是主从JK触发器CT7472。

假如J1=1,K1=K2=K3=1,并已知输入信号的波形如图P3-18所示,试画出输出端Q的波形。

解:如下图。

3-19 图P3-19给出了集成D触发器CC4013的逻辑符号和输入信号的电压波形,试画出输出端Q和的电压波形。

解:如右图。

3-21 图P3-21是D触发器74LS74的符号。

已知输入信号波形如图所示,试画出输出端Q 和的电压波形。

解:如右图。

3-22 图P3-22是JK触

发器74LS76A的符号。

已知

其输入信号波形如图所示,

试画出输出端Q的电压波形。

解:如右图。

3-24 设图P3-24中各触发器的初始状态皆为0,试画出在CP信号连续作用下各触发器输出端的电压波形。

题3-24图

解:波形画于下图。

题解3-24图

3-25 由CMOS 反相器及电阻构成的施密特触发器电路如下图所示。

已知R 1=10 k Ω,R 2=30 k Ω。

G 1、G 2门为CMOS 反相器,V DD =15V 。

试计算其回差电压△V T 。

解:取V th =V DD /2=7.5V

V 102V )311(V )R R 1(V DD th 2

1

T =⋅+=+=+ V 52V )311(V )R R 1(V DD th 21

T =⋅-=-=-

V 5V V V T T ==∆-+ 3-26 采用TTL 集成与非门和二极管构成的施密特触发器电路如下图所示。

设二极管的正向导通电压为0.7V ,G 1门的阈值电压为1.4V 。

(1) 分析电路的工作原理,试求回差电压△V T 为多少?

(2) 若输入波形v I 如图P3-26 (b) 所示,试画出v O 的波形;

(3) 画出v O ~ v I 的关系曲线(电压传输特性曲线)。

解:V I =4V , G 1输入端电位大于V TH ,所以G 1输出1,

,

V 6.3v O =v O =0.3V 。

当v I 下降至0.7V ,v I3=1.4V= V TH ,

G 3转为关门输出1,即v O =3.6V ,

V 3.0v O =,所以V T -=0.7V 。

v I 下降至1.4V ,G 1转为关门输出1,不改变输出状态。

v I =0V , G 1输出1,G 3输出0,即

,V 6.3v O =v O =0.3V 。

当v I 上升至0.7V ,v I3=1.4V= V TH ,不改变

输出状态,v I 上升至1.4V , v I1=1.4V >V TH ,G 1

转为开门输出0,即使,V 6.3v O =v O =0.3V 。

所以V T+=1.4V 。

电路回差电压为:

△V T = V T+-V T -=1.4V -0.7V=0.7V ,其波形

和传输特性如右图所示。

题3-25图

题3-26图

题解3-26图

3-29 由CMOS 门电路组成的电路如下图所示,设

门电路输入端无保护二极管,输入信号v I1为一正极性

窄脉冲。

已知电源电压为V DD 。

要求:

(1) 定性画出v O1,v I2及v O 的波形图;

(2) 输出v O 脉冲宽度t w 的表达式。

解:由图可知,电路为单稳态触发器,波形如右图所示,

对于CMOS 门有V TH =V DD /2,

2ln RC V )(v )

0(V )(v ln RC t T H 2I 2I 2I W =-∞-∞=+

3-30 如下图(a )是74121集成单稳态触发器的逻辑符号,其功能表见本章3.4.2节表3-11,图中1A 、2A 、B 为触发脉冲输入端。

(1) 若已知1A 、2A 、B 信号如下图(b )所示,画出芯片正常工作时,Q 端的波形。

(2) 若已知输出脉宽t w 为0.7ms 的脉冲,采用内接电阻R in t (2k Ω)时,外接电容C ext 应取多大?若采用外接电阻的方法,取C ext =0.04µF ,则R ext t 应取多大?画出这两种接法74121芯片的接线图。

解:(1) 只有B=’H ’, 1A 、2A 同时由高到低的下降沿,或1A 、2A 同为L ,B 由低到高的上升沿两种情况,电路才被触发进入暂稳态。

题3-29图 题解3-29图

题解3-30图(a )

(2) 用CT74121的内部定时电阻R i n t =2kΩ,t W =0.7ms ,C ext =0.5μF 。

CT74121用外接定时电阻,C ext =0.04μF ,t W =0.7ms ,R ext =25kΩ,。

连线图下图所示。

3-33 如右图所示电路中,CMOS 集成施密特触发器的电

源电压V DD =15V ,V T+=9V ,V T -=4V 。

要求:

(1)要得到占空比为50%的输出脉冲,R 1与R 2的比值应取

多少?

(2)若取R 1=3 k Ω,R 2=8.2k Ω,C =0.05µF ,忽略二极管的正

向导通压降,输出信号的频率及占空比各是多少?

解:当v O =H 时,v O 通过R 2对C 充电,从v C =V T -至v C =V T +,使v O =L ,所以 C R 6.0915415ln C R V V V V ln C R V )(v )

0(v )(v ln C R T 22T DD T DD 2T C C C 21≈--≈--=-∞-∞=+-+。

当v O =L 时,C 通过R 1放电,从v C =V T+ 至v C =V T -,使v O =H ,所以

C R 8.049ln C R V 0V 0ln C R V )(v )

0(v )(v ln C R T 11T T 1T C C C 12≈≈--=-∞-∞=-+-。

(1)占空比为50%时R 1与R 2的比值:

0.6R 2C=0.8R 1C ,R 1/R 2=0.75

(2)振荡周期

ms 246.010

05.0102.86.0C R 6.0T 6321=⨯⨯⨯⨯==- ms 12.01005.01038.0C R 8.0T 6312=⨯⨯⨯⨯==-

ms 366.012.0246.0T T T 21=+=+=

则振荡频率为:kHz 73.210366.0/1T /1f 3≈⨯==-。

占空比为:672.0366.0/246.0)T T /(T q 211≈=+=

题解3-30图(b )

题3-33图 图P6-15

3-39 对如图P3-39(a) (d)所示V O与V I对应关系的波形图,各应选取何种电路才能实现?

解:(a)用施密特触发器,其特性应是V T+和V T-很接近。

(b)可用555组成的单稳态电路实现,也可以用施密特触发器整形,再触发单稳态]电路实现。

(c)用一个单稳态触发器完成t W1的延迟,触发极性应为上升沿,再用第二个单稳态触发器形成t W2宽度的脉冲。

触发极性应为下降沿。

(d)用一个单稳态触发器完成,稳态时输出应为高电平,触发极性应为上升沿。