基于DSP的低功耗高速数据采集系统设计

基于DSP的高精度数据采集系统设计

图 1 DS P数 据 采集 系统 原 理 框 图

收 稿 日期 :0 0年 3 1日 , 回 日期 :0 0年 3月 2 21 月 修 21 8日

作者 简介 : 马福 民, , 男 高级工 程师 , 研究方 向 : 装备监造 与研 究。梁 晓峰 , , 男 工程师 , 研究方 向 : 装备可靠性 。

管 理技 术 自动关 闭空 闲状 态 的外 设 、 内存 和 内核 功

能 单元 , 以实现 在 极 低 功 耗 下 运 行 , 而 延 长 了系 从

统 的工作 时 间 。

2 系统 简 介

本文研 究 的基 于 D P的数 据 采 集 系统 由模 拟 S

板 和数字 板两 部 分 组 成 , 结 构 框 图如 图 1所 示 。 其 模拟 板 主要完 成 对 矢 量 水 听 器 输 出原 始 信 号 进行 放 大 、 波等 信 号 调 理 功 能 , 字 板 主 要 完 成 系 统 滤 数

关键 词 T 3 0 5 0 A; F卡 ; 据 采 集 ; 量 水 听 器 MS 2VC 5 9 C 数 矢 T 24 P 7

中图分号

D e i n o a a Ac u s to s e g e i i n Ba e n D S s g f D t q i ii n Sy t m Hi h Pr c s o s d o P

M a Fu i Li i of ng m n ang X a e

( i t r p e e t tv r a fNa a q im e tDe a t e t i o g i g Ae a M l a y Re r s n a ie Bu e u o v lE u p n p rm n n Ch n qn r ,Ch n d 6 0 0 ) i eg u 1 10

基于DSP技术的高速数据采集系统

J.数 字 信 号 数 据 采 集 的准 确 性 和 实 时性 是 关 系 到 整 个 系 统 精 度 的关 键 问 题 。受 运 算 速 度 及 算 l, t

章 启 成

( 南京 工程 学 院 , 江苏 南 京 2 】0 ) 110

【 摘 要 】 传输带宽和抗干扰能力是评价数据采集系统性能的重要指标 。本文采用高速数字信号处

理 ( i t i a P ̄'s g 简称 D P 心 片 T S 2 C 0构 成嵌 入 式数据 采 集 系统 , Dga Sg l l e i , il n sn S )4 4 - M 30 5 实现 数 据 的 高速 采 集 、 佶输 和存储 , 块化设 计 思 想及 大规模 可 编程 器件 的采 用 , 系统 具备 较 强 的可扩 展 性 。 模 使

【 关键词】 数据采集

D P 存储器 S

数 据 的正 确 实 时 采 集 是 系 统 数 据 分 析 和实 施 监 测 、 制 的前 提 , 控 因而 数 据 采 集 系 统 往 往 是 系 统

设计 和 歼 发 人 员 所非 常 关心 的 问题 。对 于数 据 采 集 系 统 的 性 能 , 从 以下 几 个 方 面 进 行 评 估 : 应

友好 等 特 点 。

系统 应 在 一 定 范 围 内 随指 标 要 求 变 化 可 扩 展 ;

( ) 机 交互 能 力 工 作 于 现 场 的采 集 器 还 应 具 备 便 携 性 、 于操 作 、 定 参 数 方 便 , 机 界 面 4人 易 设 人 小 文 没计‘ 数据 采 集 系 统 是 “ 字式 闭环 控 制 系统 ” 子 系 统 , 于 大 型 高 速 旋 转 机 械 的 多 参 的 数 的 用 数 实 时控 制 与监 测 。 虽 然 大 系统 采 用 双 闭环 反 馈 控 制 方 式 , 负 反 馈 本 身 只 能 对 前 项 通 道 上 出 现 但

一种基于DSP+FPGA的高速数据采集系统设计

对采集到的数据进行滤波及 FT变换等处理。 PA F FG 作为外设, 主要对 AD芯片、S 芯片等进行控制。该 / UB 系统电路结构简单、 功耗低、 数据传输速度快, 可用于电压 、 电流等模拟量的采集及数字信号的采集。

关键 词 : 数据 采 集; 浮点 DP FG ;S S ;PA UB

D T =( tes >Z ) A A< o r = ; h

wh n s2 e t 2=>

c nv n< 1;s n o =… c <=… wrt n =’ ’ 1; i e < 1;

— —

ra n e d <=’’ac <=’’ 1; th l 0;

—

AD

—

D T = ( tes >Z) A A< ohr = ;

到上位机 。

系统 的 I / O需求和 门数要求 。高速 AD芯片采用 /

A I 司的 AD 9 8该 芯片可 以 同时采样 8路模拟 D公 73 , 量信 号 , 有两个 转 换核 , 行 输 出数据 , 具 并 实现 了高 速数据 的采集 与传 输 。为 了更 方便 的与 P C机通讯 ,

wh n s2 => e t

co n y

—

n … c n <= 1;s <=’’ it n … 1; wr e <= 1;

— _ _

ra n e d <=’’a c <=’。 1; th l 0; AD

—

RW 信号及 P G 1 / A E 信号的组合逻辑对 F G P A进行

读/ 写操作 。

2 系统 组 成

高速数据 采集 系统结 构框 图如 图 1 所示 。该 系

设计 选用 了 P L S公 司生 产 的 IP 5 1 HIP S 18 ,完 全符

一种基于DSP的高速数据采集系统的设计与实现

一种基于DSP 的高速数据采集系统的设计与实现ΞDesign and R ealization ofA High 2Speed Data Acquisition SystemB ased on DSP谢 煜1,黄 为2(1.商丘师范学院物理系 河南商丘476000;2.西南交通大学电气工程学院 四川成都610031)【摘 要】 研究了一种以数字信号处理器(DSP )为核心的高速多通道数据采集系统,详细讨论了该数据系统的结构与软、硬件实现,分析了计算机并口处于EPP 模式下和DSP 进行通讯的原理,设计了在EPP 模式下采用FIFO 实现高速数据传输的电路,并论述了数据采集软件开发中的若干关键技术。

现场运行表明,该数据采集系统具有速度快、控制方便、可靠性高等优点。

关键词:数据采集,DSP ,增强并行口(EPP ),先进先出存储器(FIFO )【Abstract 】 This paper introduces a multi 2channel high 2speed data acquisition system based on DSP (digital signal processor ),discusses the architecture of this system and the realization of hardware and software ,analyses the principle of communication between the parallel ports of PC in EPP mode and DSP ,designs the high 2speed data transmission circuit which is realized with FIFO in EPP mode ,and illustrates several key technologies in developing the data acquisition software.Field running shows that the data ac 2quisition system has many advantages such as high 2speed ,easy 2to 2control ,high reliability ,and so on.K eyw ords :data acquisition ,digital signal processor ,enhanced parallel port (EPP ),first in first out (FIFO )1 引 言随着信息技术革命的深入和计算机技术的飞速发展,数字信号处理技术已逐渐成为一门主流技术,在许多领域得到了广泛应用。

基于DSP和USB的高速数据采集与处理系统设计

基于DSP和USB的高速数据采集与处理系统设计在图像数据处理系统中,经常需要对高速信号举行采集与处理。

例如,在光传感技术中对光脉冲散射信号的测量,在雷达工程中对电磁脉冲信号的测量等,都需要对高速信号举行采集与运算,而且此类高速信号的测量,往往对数据采集与处理系统提出严格的要求。

本文设计并实现一种基于和的高速数据采集与处理系统。

该系统容易,牢靠性好,具有一定的通用性,并且可以举行多通道扩展。

1 原理概述基于DSP和USB的高速数据采集与处理系统的原理框图1所示。

系统上电后,DSP、分离由各自的FLASH加载程序,采集与处理系统开头运行。

在A/D变换器完成转换后由FPGA向DSP发送中断0申请信号,DSP从A/D FIFO RAM中读取数据,并举行小波变换去噪处理,处理结束后DSP 向USB控制器发送中断申请信号,USB控制器将处理后的数据发送至PC机,由主机应用程序显示数据。

主机应用程序还可以对囫囵采集、处理系统举行控制,主要设定三个功能:接收处理后的数据,接收处理前的数据,设定A/D的采样频率和采样点数。

2 系统硬件设计系统硬件设计主要分为三大部分:DSP部分、FPGA部分、USB部分。

2.1 DSP部分设计本系统用法的DSP芯片为TI()公司的TMS320VC33,它是TI公司推出的性价比极高的32位浮点型数字信号处理芯片,是目前在国内外用法最为广泛的浮点DSP之一。

TMS320VC33具有以下特点:哈佛结构;流水线操作;专用的硬件乘法器;特别的DSP命令;迅速的命令周期。

另外,TMS320VC33还具有强大的浮点运算能力,运算速度可达150MFLOPS(每秒百万次浮点运算),处理能力达到75(每秒百万次命令周期)。

而且,它还采纳3.3V I/O第1页共4页。

基于DSP的高速数据采集系统设计与实现

基于DSP的高速数据采集系统设计与实现近年来,数字信号处理(Digital Signal Processing,DSP)得到了广泛的应用,特别是在高速数据采集系统中。

高速数据采集系统的设计和实现,对于科学研究和工业控制等领域至关重要。

因此,本文将重点讨论基于DSP的高速数据采集系统的设计和实现。

一、引言高速数据采集系统是一种用于采集高速数字信号的电子设备。

它们广泛应用于无线电通信、医疗仪器、控制系统、航空航天等领域。

为了更好地满足市场需求,高速数据采集系统需要具有高分辨率、高速率、高精度和低噪声等特性。

目前,市场上的高速数据采集系统大多采用DSP芯片作为数据处理核心。

DSP 芯片具有高性能、低功耗、灵活性强等特点,可以大大提高数据采集、处理和储存的效率。

因此,DSP技术已经成为高速数据采集系统设计的重要手段之一。

二、基于DSP的高速数据采集系统的设计和实现基于DSP的高速数据采集系统可以分为以下几个部分:信号输入模块、信号调理模块、数据处理模块和数据输出模块。

1. 信号输入模块信号输入模块是高速数据采集系统的核心组成部分之一。

其主要功能是将来自传感器和信号源的传输数据进行采集。

在设计信号输入模块时,需要考虑到信号源的信号特性以及传输介质的特性。

一般情况下,采用ASIC(Application Specific Integrated Circuit)芯片实现数据采集的模拟前端电路。

在信号输入模块中,需要进行信号放大、滤波、采样和数据转换等一系列操作。

这些操作需要满足系统对信号采集的高分辨率、高速率、高精度和低噪声的要求。

2. 信号调理模块信号调理模块用于对采集到的原始数据进行处理和提取。

该模块的主要任务是对信号进行滤波、去噪、分频和分析等操作,以便更好地适应后续的数据处理和分析。

信号调理模块的实现方式通常采用DSP芯片进行数据处理。

DSP芯片可以根据不同的信号特性,运用不同的算法进行信号调理。

在设计信号调理模块时,需要根据信号的特性和需求选择和设计合适的算法。

基于DSP的高速数据采集系统设计与实现

void maxl25——isr(void)

f

Portl=0x03;

//选择A组4路通道

/,启动转换,IOPF6上升沿

‘PFDATDIRI=0X0040;//IOPF6=I

‘PFDATDIR&=0XFFBF;//IOPF6--0

*PFDATDIRt=0X0040;//IOPF6=I //查询转换是否完成

。跚

图4多任务启动流程图 Fig.4 Flow diagram ofmultitask start

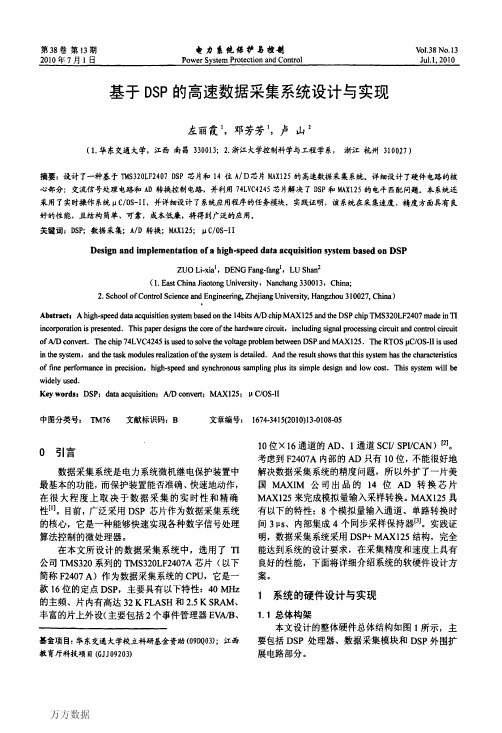

2.3主要采样程序的实现 (1)AD采样中断程序max]25 isr() AD采样是在GPTimer3的周期中断中完成的,

当MAXl25全部8路通道AD转换后,发消息给 Pd Task()任务进行采样点处理。AD采样中断程 序程序应尽可能短小,其示意代码如下所示:

理电路、AD转换芯片和电平转换电路。整个系统

掰刊惆掣 对外可提供8路的A/D转换通道,下面将详细介

绍系统的交流采样模块。

爿 ^-

r

DSP处理器

SRAM

¨ ADC

^_ r

划RTnEEPROMI

(TM¥320

{MAXl25)

——鼍—‰『

LF2407A)

^_ r

剖JTAG接El

妻蒺b

^_ r

=爿通f寺摆fJ

『也路

图1数据采集系统硬件结构图 Fig.1 Hardware structure of data acquisition system

平,由DIR管脚确定其传输方向。 MAX 1 25的输出接入74LVC4245锁存后进行

电平转换,再进入DSP。74LVC4245的1DIR、2DIR 接MAXl25的W爪引脚,输出允许/OE端接

一种基于DSP的高速高精度信息采集系统设计

一种基于DSP的高速高精度信息采集系统设计【摘要】科学研究和工业生产,对测控系统信息采集的速度和精度提出了越来越高的要求。

本文利用TMS320C6713B芯片高速度高效率的信号处理能力,结合高精度A/D转换芯片MAX1403,提出了一种高速高精度的信息采集系统设计方案,并以热电偶温度传感器的应用为例,给出了实用的温度信号采集电路。

【关键词】DSP;信息采集;温度传感器0 引言信息采集技术应用极为广泛,在工农业生产、科学研究、国防现代化、消费娱乐等各行各业都有大量应用,是现代信息技术的三大支撑技术之一,在信息系统中是首要的基础的一环[1]。

信息采集技术的优劣影响着信息传输和信息处理的质量。

随着全社会信息化水平的提高,业界对信息采集技术提出了更高的要求。

速度和精度是衡量信息采集技术优劣程度的关键指标,设计高速高精度的信息采集系统具有重要的实用价值。

1 硬件设计考虑信息采集系统对高速高精度的要求,本文利用TI公司的浮点DSP芯片TMS320C6713B作为处理器。

TMS320C6713B是TI公司继C62X系列定点DSP 芯片后开发的一种32bit新型浮点DSP芯片,该芯片的内部结构在C62X基础上改进,具有如下特点:(1)处理速度快,工作主频最高可达到300MHz,峰值运算能力为2400MIPS/1 800MFLOPS;(2)硬件支持IEEE格式的32bit单精度与64bit双精度浮点操作;(3)集成了32×32bit的乘法器,其结果可为32bit或64bit;(4)C62X指令无需任何改变即可在C6713B上运行[2]。

要完成高精度的信息采集需要高精度A/D转换芯片,本文中选用MAXIM 公司的MAX1403。

其主要特点为:(1)精度为18bit(480SPS),16位无漏码,INL:±0.001%;(2)自带恒流源输出,可方便的与传感器相连;(3)供电电压为3.3V,方便应用于DSP系统中;(4)低功耗;(5)3个全差分测量通道,2个额外的全差分校正通道;(6)片内可编程的增益放大器,1~128倍放大;(7)过采用技术和数字滤波器;(8)SPI串口输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于DSP的低功耗高速数据采集系统设计

随着电子技术的发展及新器件的不断涌现,电子系统在手持设备、便携

医疗仪器以及野外测试仪器等领域得到了广泛的应用。

在这些领域的应用中,

由于客观条件的限制,通常采用电池或蓄电池为仪器设备提供电源。

在这种情

况下,如要实现系统长时间工作,必然对仪器设备系统功耗的要求较高,因此

低功耗系统的设计在这些应用领域中得到广泛重视。

1 TMS320VC5509 简介

TMS320VC5509(以下简称VC5509)是德州仪器(TI)公司针对低功耗应用领域推出的一款低功耗高性能DSP,采用1.6V 的核心电压以及3.3V 的外围接口电压,最低可支持0.9V 的核心电压以0.05mW/MIP 的低功耗运行。

VC5509 支持丰富的外设接口,最高支持144MHz 的时钟频率,片内具有双乘累加器,每周期可执行一条指令或两条并行指令,具有高达288MIPS 的处理能力。

VC5509 内部存储器采用统一编址,带有128K 字RAM,其中包括32K 字双存取RAM(DARAM)以及96K 字单存取RAM(SARAM),另外还有

64KB 片内只读ROM,并可以实现高达4MB 的外部存储空间扩展,是一款具

有较高性价比的低功耗DSP 芯片。

VC5509 的结构框图如图1 所示。

2 系统设计与实现

本系统要求实现四通道同步采样,每通道采样频率为50kHz,系统供电为

+5V,全速运行时整体功耗低于250mW。

针对这些技术指标,本系统以低功耗DSP 芯片TMS320VC5509 为核心,采用串行EEPROM 作为程序存储器,选用四片微功耗12 位ADC 实现四个通道模拟信号的同步采集。

系统中设计铁电存储器(FRAM)作为掉电保护数据存储器,并设计一个异步串口实现与外部系

统的通讯。

系统原理框图如图2 所示。

在保证实现系统功能的前提下,本系统。