门电路2

第三章 门电路 - 第二部分

负载 高电平输出等效电路

47

电子工程学院

TTL反相器的静态输出特性

1. 高电平输出特性

T4、D2导通,T2、T5截止。电流流出门(拉电流) •空载时:vO= vOH ≈ 5-2×0.7=3.6V •加上负载RL时: 当RL较大,iL< 5mA时,由于是射极跟随器输出, 内阻低,输出电平随输出电流iL的变化不大,基 本保持为VOH 。 随着RL的减小,iL增大,R4上的压降也随之增大, 最终使T4的集电结变为正偏,T4进入饱和状态, 失去射极跟随功能,输出vO随iL绝对值的增加而 几乎线性地降低。 受功耗限制,实际器件高电平输出时iL的最大值 比5mA小得多,74系列手册上规定iL不能超过 0.4mA。

I A + I B = 2 I IH ≤

2. 或非门

或非门的输入端和输出 端电路与反相器相同, 所以输入特性和输出特 性也和反相器一样。

A

A+B

—

A+B

A+B

—

B

输入特性:当输入为高或低电平时,总电流均等于各输入端电流之和。 与输入端个数有关。

动态电流

当输出从低电平转换为高电平的过程中,T4从截止变为导通,T5从深 度饱和变为截止, T5转换所需的时间比T4长,因此在过渡过程中会出 现短时间内T4和T5同时导通的状态,此时有很大的瞬时电流流过T4和 T5 ,使电源电流出现尖峰脉冲。

尖峰电流的影响:使电源电流平均值加大了。 在计算电源容量时应考虑尖峰电流的影响。应 采取措施抑制尖峰电流导致的系统内部噪声。

输入特性:输入电流与输入电压之间的关系,即iI = f(vI)

电流为正

iI

43

电子工程学院

TTL反相器的静态输入特性

第二章门电路

7

§2.2 半导体三极管的开关特性 一. 双极型三极管的结构 IC

IB

VBC – + + + VCE VBE – – IE

NPN Si管

8

二. 特性

1.电流:IE =IB +IC 2.工作状态: 工作状态分类 导通 截止

IC1

T2 • IE2 • Y ° T5

R3

•

IR3

IB5

N—表示N个发射极。

41

●T1的状态:

∵VB1=VBC1+VBE2+VBE5=2.1V ∴T1处于倒置状态。 I C1 I B1 N反 I B1

I B1 VCC VB1 R1

0.73mA

● T2、 T5的状态:

T2、 T5饱和VO=0.3V

45

二.TTL与非门 • R1 4K • Vcc =5V

°

R2 1.6K

•

R4 130

T4

A

B

T1

T2

• R3 1K • 倒相级

D3

• T5 Y °

输入级

输出级

46

三.负载能力分析 负载——指门电路输出端所接的其它 电路。 NO——扇出系数,表示能够驱动同类门的数目。 灌电流负载——负载电流从后级门注入前级门 负载

14

5)饱和条件及特点 条件:IB >IBS IB — 进入饱和以后的基流。 IBS—临界饱和基流。 求IB 、 IBS的步骤: Vi VBE a)I B Rb

b)I CS c)I BS VCC VCES VCC RC RC I CS

(数字电子技术基础)第2章. 门电路

• 小规模集成电路(SSI-Small Scale 小规模集成电路(SSI(SSI Integration), 每片组件内包含10~100 10~100个元件 Integration), 每片组件内包含10~100个元件 10~20个等效门 个等效门) (或10~20个等效门)。 • 中规模集成电路(MSI-Medium Scale 中规模集成电路(MSI (MSIIntegration),每片组件内含100~1000 100~1000个元件 Integration),每片组件内含100~1000个元件 20~100个等效门 个等效门) (或20~100个等效门)。 • 大规模集成电路(LSI-Large Scale 大规模集成电路(LSI (LSIIntegration), 每片组件内含1000~100 000个 Integration), 每片组件内含1000~100 000个 元件( 100~1000个等效门 个等效门) 元件(或100~1000个等效门)。 • 超大规模集成电路(VLSI-Very Large Scale 超大规模集成电路(VLSI (VLSIIntegration), 每片组件内含100 000个元件 Integration), 每片组件内含100 000个元件 1000个以上等效门 个以上等效门) (或1000个以上等效门)。

•

+5V

R1

T1

T5 R3

•

(2-30)

前级

后级

灌电流的计算

饱和

I OL

5 − T5压降 − T1的be结压降 = R1

5 − 0.3 − 0.7 ≈ 1.4mA = 3

(2-31)

关于电流的技术参数

名称及符号 输入低电平电流 IiL 输入高电平电流 IiH IOL 及其极限 IOL(max) IOH 及其极限 IOH (max) 含义 输入为低电平时流入输 入端的电流-1 入端的电流 .4mA。 。 输入为高电平时流入输 入端的电流几十 几十μ 。 入端的电流几十μA。 当 IOL> IOL(max)时,输出 不再是低电平。 不再是低电平。 当 IOH >IOH(max)时, 输出 不再是高电平。 不再是高电平。

数字电路第2章 门电路

2)输入负载特性 (ui R )

R1 3k b1 A B C T1 R2 750 R4 100

+5V

c1

T3

T2

3k

T4

R5 T5

F

ui

V

R

R3

360

R较小时 设:T2、T5 截止

A B C

R1 3k b1

+5V

R4

R2

c1

T1

T2

R5

T3

T4 F T5

R

ui

R3

R (5 U ) 4.3R ui be1 R1 R 3 R

I BS vcc vCES 5 0.3 mA 0.094mA βRc 50 1

V CC = +5V Rc iC 1kΩ vo c R b 10kΩ b β = 40 iB e

②vi=0.3V时,iB=0,三极管 工作在截止状态,ic=0。因 为ic=0,所以输出电压: vo=VCC=5V

IB 0

IC 0

VCE VCC

7

三极管的开关特性

+UCC 3V 0V RB RC uO T

+UCC

RC 3V

饱和时, VCE ≈ 0,C、 E极间电阻 很小 0V 截止时, IC ≈ 0,C、 E极间电阻 很大

C E

uO 0

相当于 开关闭合

ui

饱和 截止

+UCC RC

C E

uO UCC

避免!

0V 0

VL(max)

低电平

分立元件门电路和集成门电路:

分立元件门电路:用分立的元件和导线连 接起来构成的门电路。简单、经济、功耗低, 负载差。 集成门电路:把构成门电路的元器件和连 线都制作在一块半导体芯片上,再封装起来, 便构成了集成门电路。现在使用最多的是CMOS 和TTL集成门电路。

第二章_门电路

第二章 门电路三、高低电平获取方法开 关5V V H1+5V0V V L 02.1 概述第二章门电路2.3 分立元件门电路一、二极管与门V A V B V Y0V0V0V3V3V0V3V3VA B Y0000101001110.7V0.7V0.7V3.7V2.3 分立元件门电路第二章门电路二、二极管或门V A V B V Y0V0V0V3V3V0V3V3VA B Y0000111011110V2.3V2.3V2.3V2.3 分立元件门电路第二章门电路三、三极管非门V i Vo0V V CCV CC0.2VA Y01102.3 分立元件门电路第二章门电路1)结构TTL反相器由三部分构成:输入级、中间级和输出级。

1、TTL反相器的结构和原理一、TTL逻辑门2.4 TTL集成门电路第二章 门电路A 为高电平时(3.4V),V B1≈2.1V ,T 1倒置,VB2≈1.4V ,T 2和T 5饱和,T 4和D 2截止,Y 为低电平。

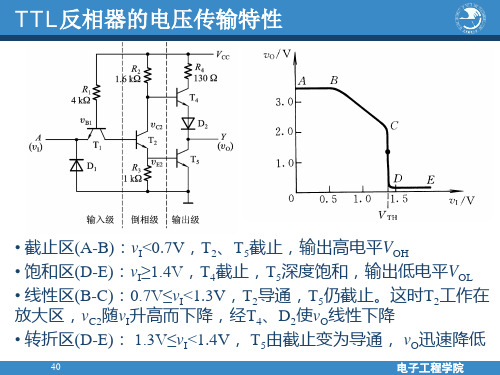

2)原理A 为低电平时(0.2V) ,T 1饱和,V B1≈0.9V ,V B2≈0.2V ,T 2和T 5截止,T4和D2导通,Y 为高电平;2.4 TTL 集成门电路第二章 门电路分为四个区段:AB 段:Vi <0.6伏,截止区;BC 段:0.6伏<Vi <1.3伏,线性区;CD 段:Vi ≈1.4伏,转折区;DE 段:Vi >1.4伏,饱和区。

输出高电平:V OH =3.4V 输出低电平:V OL =0.2V 阈值电压:V TH =1.4VV THVi (V)2.4 TTL 集成门电路2.4 TTL 集成门电路(略)一、TTL 与非门的基本结构及工作原理1.TTL 与非门的基本结构B A C+V RP CC (+5V )P PP N N NN+V 13(+5V )CC A B CT b1R 12.4 TTL 集成门电路第二章 门电路 2.4 TTL 集成门电路第二章 门电路CB A L ⋅⋅=该发射结导通,V B 1=0.9V 。

第九讲 CMOS门电路(二)

VDD RL (nIOH mIIH ) VOH

VDD VOH RL (max) nIOH m IIH

内容回顾

CMOS与非门

内容回顾

或非门:

带缓冲级的CMOS门电路

内容回顾

二、漏极开路输出的门电路(OD门) P94 为了满足输出电平的变换,输出大负载电流,以及 实现“线与”功能,将CMOS门电路的输出级做成漏 极开路的形式,称为漏极开路输出的门电路,简称OD (Open-Drain Output)门 1.结构和符号

HC---High-Speed CMOS HCT High-Speed CMOS,TTL Compatible AHC---Advanced High-Speed CMOS AHCT--Advanced High-Speed CMOS,TTL Compatible LVC---Low-Voltage CMOS

3.3.7 CMOS数字集成电路的各种系列

自 20 世 纪 60 年 代 CMOS 电 路 问 世 以 来 , 随 着 CMOS制造工艺水平的不断改进,CMOS电路的性能 得到了迅速提高。到了20世纪80年代以后,在减小单 元电路的功耗和缩短延迟时间两个主要方面进展尤为 迅速。到目前为止,已经生产出的标准化、系列化的 CMOS 集成电路产品有 4000 系列、 HC/HCT 系列、 AHC/AHCT 系 列 、 VHC/VHCT 系 列 、 LVC 系 列 、 ALVC系列等。 最早投放市场的4000系列传输延迟时间长(可达 100ns 左右)、带负载能力弱,因此,目前它已基本 上被后来出现的HC/HCT系列产品所取代。

数字电路基础第2章门电路

提高了开关速度。

SBD iD

i ib

(a)

(b)

抗饱和三极管

2.4 TTL门电路

三、TTL系列门电路

性能比较好的门电路应该是工作速度既快,功耗又小的 门电路。因此,通常用功耗和传输延迟时间的乘积(简称功 耗—延迟积)来评价门电路性能的优劣。功耗—延迟积越小, 门电路的综合性能就越好。

❖ 低电平UL:

输入低电平UIL 输出低电平UOL

❖ 逻辑“0”和逻辑“1”对应的电压范围宽, 因此在数字电路中,对电子元件、器件 参数精度的要求及其电源的稳定度的要 求比模拟电路要低。

2.2 半导体二极管和三极管的开关特性

2.2.1 半导体二极管的开关特性 一、二极管伏安特性 反向击穿电压

iD(mA)

①74:标准系列; ②74H:高速系列; ③74S:肖特基系列;

④74LS:低功耗肖特基系列;74LS系列成为功耗延迟积较 小的系列。74LS系列产品具有最佳的综合性能,是TTL集成 电路的主流,是应用最广的系列。 ⑤74AS:先进肖特基系列;

④74ALS:先进低功耗肖特基系列。

2.4 TTL门电路

- 开关闭合 - 开关断开

2.3 分立元件门电路

一、二极管与门

VD1 A

VD2 B

+VCC(+5V) R

Y

uA uB

uY

VD1 VD2

0V 0V 0.7V 导通 导通

0V 5V 0.7V 导通 截止

5V 0V 0.7V 截止 导通

5V 5V 5V 截止 截止

AB

Y

Байду номын сангаас00

0

第2章 门电路学习指导

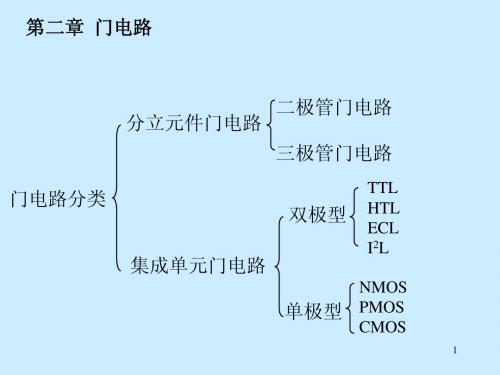

第二章门电路一、内容提要本章系统地讲述了数字电路的基本逻辑单元——门电路。

由于门电路中的二极管和三极管经常工作在开关状态,所以首先介绍了它们在开关状态下的工作特性。

然后,重点讨论了目前广泛使用的TTL门电路和CMOS门电路。

对于每一种门电路,除了讲解它们的工作原理和逻辑功能以外,还着重介绍了它们作为电子器件的电气特性,特别是输入特性和输出特性,以便为实际使用这些器件打下必要的基础。

二、重点难点虽然这一章讨论的只是门电路的外特性,但无论集成电路内部电路多么复杂,只要它们和这一章所讲的门电路具有相同的输入、输出电路结构,则这里对输入、输出特性的分析对它们也同样适用。

因此,这一章是全书对电路进行分析的基础。

本章的重点内容包括以下三个方面:1、半导体二极管和三极管(包括双极型和MOS型)开关状态下的等效电路和外特性;2、TTL电路的外特性及其应用;3、CMOS电路的外特性及应用。

为了正确理解和运用这些外特性,需要了解TTL电路和CMOS电路的输入电路和输出电路结构及它们的工作原理。

内部的电路结构不是重点内容。

鉴于CMOS电路在数字集成电路中所占的比重已远远超过了TTL电路,建议在讲授时适当加大CMOS电路的比重,并相应压缩TTL电路的内容。

TTL电路的外特性是本章的一个难点,同时也是一个重点。

尤其是输入端采用多发射极三极管结构时,对输入特性的全面分析比较复杂。

从实用的角度出发,只要弄清输入为高/低电平时输入电流的实际方向和数值的近似计算就可以了。

三、习题精解知识点:三极管饱和、截止的分析判断。

例2.1 电路如图2.1所示。

求使三极管截止的v imax ;保证三极管饱和的v imin ,已知三极管β=30,V BE =0.7V ,V CES =0.3V 。

解 三极管的开关条件分别为:V BE ≤0,三极管截止,I B ≥I BS 三极管饱和导通。

当三极管截止时,其等效电路如图2.2(a )所示。

I B=0,则01010221≤-++=R R R v V i BE图2.1图2.2 即010*******≤-ΩΩ+Ω+V k k k Vv i解得 v i ≤2V 即 v imax ≤2V当三极管饱和导通时,其等效电路如图2.2(b)所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

逻辑门电路

一、选择题

1. 对三态门,是正确的说法。

A.输出有高阻态、0态、1态

B.输出高阻态时相当于输出悬空

C.输出电压不高不低

D.用于总线传输

2. 以下电路中可以实现“线与”功能的有。

A.与非门

B.三态输出门

C.集电极开路门

D.漏极开路门

3.以下电路中常用于总线应用的有。

A.T S L门

B.O C门

C.漏极开路门

D.C M O S与非门

4.对于T T L与非门闲置输入端的处理,可以。

A.接电源

B.悬空

C.接地

D.与有用输入端并联

5.C M O S数字集成电路与T T L数字集成电路相比突出的优点是。

A.微功耗

B.高速度

C.高抗干扰能力

D.电源范围宽

二、判断题(正确打√,错误的打×)

1.TTL与非门的多余输入端可以接固定高电平。

(√)

2.当TTL与非门的输入端悬空时相当于输入为逻辑1。

(√)

3.普通的逻辑门电路的输出端不可以并联在一起,否则可能会损坏器件。

(√)

4.CMOS或非门与TTL或非门的逻辑功能完全相同。

(√)

6.三态门的三种状态分别为:高电平、低电平、不高不低的电压。

(×)

7.TTL集电极开路门输出为1时由外接电源和电阻提供输出电流。

(√)

8.一般TTL门电路的输出端可以直接相连,实现线与。

(×)

9.CMOS OD门(漏极开路门)的输出端可以直接相连,实现线与。

(√)

10.TTL OC门(集电极开路门)的输出端可以直接相连,实现线与。

(√)

三、填空题

1.集电极开路门的英文缩写为门,工作时必须外加和。

2.O C门称为门,多个O C门输出端并联到一起可实现功能。

第三章答案

一、选择题

1.ABD

2.CD

3.A

4.ABD

5.ACD

二、判断题

1.√2.√3.√4.√

6.×7.√ 8.×9.√ 10.√

三、填空题

1.OC 电源负载

2.集电极开路门线与。