第2章 逻辑门电路-习题答案

第一章数字逻辑基础思考题与习题

第一章 数字逻辑基础 思考题与习题题1-1将下列二进制数转换为等值的十六进制数和等值的十进制数。

⑴(10010111)2 ⑵(1101101)2⑶(0.01011111)2⑷(11.001)2题1-2将下列十六进制数转换为等值的二进制数和等值的十进制数。

⑴(8C )16 ⑵(3D.BE )16⑶(8F.FF )16⑷(10.00)16题1-3将下列十进制数转换为等值的二进制数和等值的十六进制数。

要求二进制数保留小数点以后4位有效数字。

⑴(17)10⑵(127)10⑶(0.39)10 ⑷(25.7)10题1-4将十进制数3692转换成二进制数码及8421BCD 码。

题1-5利用真值表证明下列等式。

⑴))((B A B A B A B A ++=+ ⑵AC AB C AB C B A ABC +=++⑶A C C B B A A C C B B A ++=++ ⑷E CD A E D C CD A C B A A ++=++++)( 题1-6列出下列逻辑函数式的真值表。

⑴ C B A C B A C B A Y ++=⑵Q MNP Q P MN Q P MN PQ N M Q NP M PQ N M Y +++++=题1-7在下列各个逻辑函数表达式中,变量A 、B 、C 为哪几种取值时,函数值为1?⑴AC BC AB Y ++= ⑵C A C B B A Y ++=⑶))((C B A C B A Y ++++= ⑷C B A BC A C B A ABC Y +++=题1-8用逻辑代数的基本公式和常用公式将下列逻辑函数化为最简与或形式。

⑴ B A B B A Y ++=⑵C B A C B A Y +++=⑶B A BC A Y += ⑷D C A ABD CD B A Y ++= ⑸))((B A BC AD CD A B A Y +++= ⑹)()(CE AD B BC B A D C AC Y ++++= ⑺CD D AC ABC C A Y +++=⑻))()((C B A C B A C B A Y ++++++= 题1-9画出下列各函数的逻辑图。

数字逻辑第六版习题答案2

W= AB+ACD X = BC+BD+BCD Y = CD+CD Z=D

A 0 0 0 0 0 1 1 1 1 1

B 0 1 1 1 1 0 0 0 0 1

C 1 0 0 1 1 0 0 1 1 0

D 1 0 1 0 1 0 1 0 1 0

W 0 0 0 0 0 0 0 0 1 1

X 0 0 0 0 1 1 1 1 0 0

Y 0 0 1 1 0 0 1 1 0 0

Z 0 1 0 1 0 1 0 1 0 1

这是一个余三码 至 8421 BCD 码转换的电路

7. 下图是一个受 M 控制的 4 位二进制码和格雷码的相互转换电路。M=1 时,完 成自然二进制码至格雷码转换;M=0 时,完成相反转换。请说明之

解:Y3=X3

Y2 X2 X3

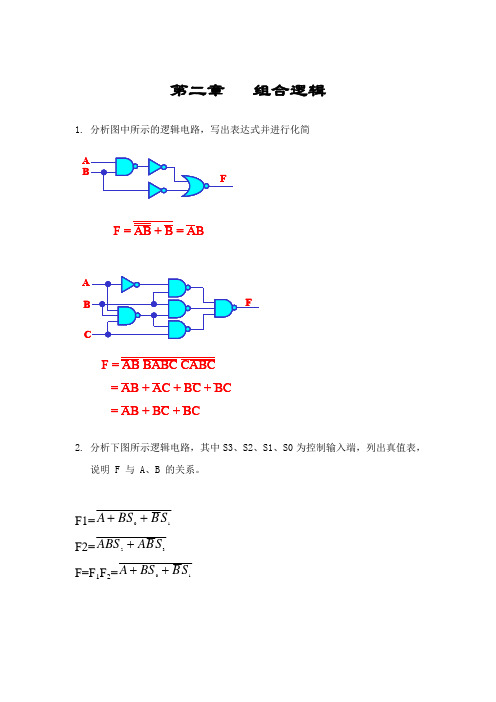

F=F1F2 F1 F1 F1 F1

S3 S2 S1 S0 × × × × × × × × 0 0 1 1 0 1 0 1

F=F1F2 A AB AB 0

3. 分析下图所示逻辑电路,列出真值表,说明其逻辑功能。

解: F1= AB C 真值表如下:

ABC A BC B C = A B C A BC ABC

Y2 0 0 0 1 0 1 1 1

Y3 1 0 0 0 0 0 0 0

Y1 A B C Y 2 BC A( B C )

于是得: Y 3 A B C A B C

10. 用两片双四选一数据选择器和与非门实现循环码至 8421BCD 码转换。

解:(1)函数真值表、卡诺图如下;

十进制数 0 1 2 3 4 5 6 7 8 9 8421码 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 余三码 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100

(数字电子技术基础)第2章. 门电路

• 小规模集成电路(SSI-Small Scale 小规模集成电路(SSI(SSI Integration), 每片组件内包含10~100 10~100个元件 Integration), 每片组件内包含10~100个元件 10~20个等效门 个等效门) (或10~20个等效门)。 • 中规模集成电路(MSI-Medium Scale 中规模集成电路(MSI (MSIIntegration),每片组件内含100~1000 100~1000个元件 Integration),每片组件内含100~1000个元件 20~100个等效门 个等效门) (或20~100个等效门)。 • 大规模集成电路(LSI-Large Scale 大规模集成电路(LSI (LSIIntegration), 每片组件内含1000~100 000个 Integration), 每片组件内含1000~100 000个 元件( 100~1000个等效门 个等效门) 元件(或100~1000个等效门)。 • 超大规模集成电路(VLSI-Very Large Scale 超大规模集成电路(VLSI (VLSIIntegration), 每片组件内含100 000个元件 Integration), 每片组件内含100 000个元件 1000个以上等效门 个以上等效门) (或1000个以上等效门)。

•

+5V

R1

T1

T5 R3

•

(2-30)

前级

后级

灌电流的计算

饱和

I OL

5 − T5压降 − T1的be结压降 = R1

5 − 0.3 − 0.7 ≈ 1.4mA = 3

(2-31)

关于电流的技术参数

名称及符号 输入低电平电流 IiL 输入高电平电流 IiH IOL 及其极限 IOL(max) IOH 及其极限 IOH (max) 含义 输入为低电平时流入输 入端的电流-1 入端的电流 .4mA。 。 输入为高电平时流入输 入端的电流几十 几十μ 。 入端的电流几十μA。 当 IOL> IOL(max)时,输出 不再是低电平。 不再是低电平。 当 IOH >IOH(max)时, 输出 不再是高电平。 不再是高电平。

数字电路第2章 门电路

2)输入负载特性 (ui R )

R1 3k b1 A B C T1 R2 750 R4 100

+5V

c1

T3

T2

3k

T4

R5 T5

F

ui

V

R

R3

360

R较小时 设:T2、T5 截止

A B C

R1 3k b1

+5V

R4

R2

c1

T1

T2

R5

T3

T4 F T5

R

ui

R3

R (5 U ) 4.3R ui be1 R1 R 3 R

I BS vcc vCES 5 0.3 mA 0.094mA βRc 50 1

V CC = +5V Rc iC 1kΩ vo c R b 10kΩ b β = 40 iB e

②vi=0.3V时,iB=0,三极管 工作在截止状态,ic=0。因 为ic=0,所以输出电压: vo=VCC=5V

IB 0

IC 0

VCE VCC

7

三极管的开关特性

+UCC 3V 0V RB RC uO T

+UCC

RC 3V

饱和时, VCE ≈ 0,C、 E极间电阻 很小 0V 截止时, IC ≈ 0,C、 E极间电阻 很大

C E

uO 0

相当于 开关闭合

ui

饱和 截止

+UCC RC

C E

uO UCC

避免!

0V 0

VL(max)

低电平

分立元件门电路和集成门电路:

分立元件门电路:用分立的元件和导线连 接起来构成的门电路。简单、经济、功耗低, 负载差。 集成门电路:把构成门电路的元器件和连 线都制作在一块半导体芯片上,再封装起来, 便构成了集成门电路。现在使用最多的是CMOS 和TTL集成门电路。

《数字电路-分析与设计》第二章习题及解答 北京理工大学出版社

5. A ⊕ B = A ⊕ B = A ⊕ B ⊕1

证明: 左边=AB+AB 中间= AB+AB=(A+B)(A+B)=AB+AB=左边 右边= (AB+AB)1+(AB+AB)1= AB+AB=中间 或者:根据 1⊕A=A,右边=中间

F1=(A+B)(B+C)(C+A)=ABC+ABC F2=(A+B)(B+C)(C+A)=ABC+ABC=F1 所以 F1=F2

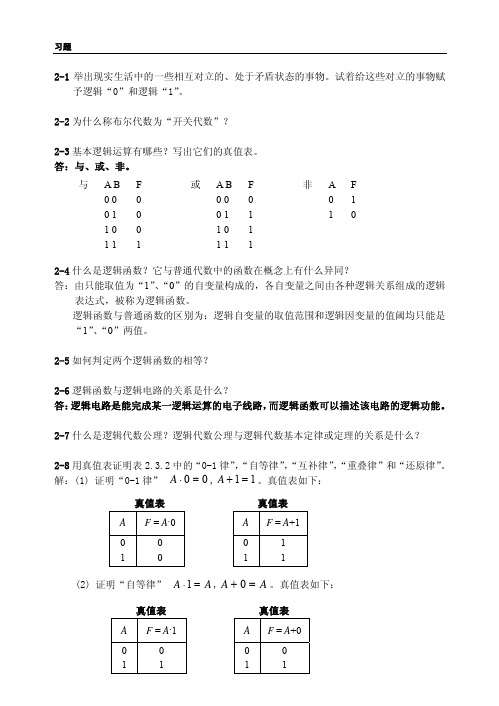

习题

2. F1 = ABC + A B C , F2 = AB + BC + CA

由 1.知:F1=F2

3. F1 = C D + A B + BC , F2 = ABC + AB D + BC D

= AB + AC + BC

F = ( A + B) ⋅ ( A + C) ⋅ (B + C) = ( A + AB + AC + BC) ⋅ (B + C) = AB + ABC + BC + AC + ABC + AC + BC = AB + AC + BC

2-12 证明下列等式。

1. A ⊕ 0 = A

9. A( A + B ) = A

证明:左边=A+AB=A=右边,得证。 用真值表法略。 2-10 用逻辑代数演算证明下列等式。

第2章 逻辑门电路

+VCC Rb b c Rc

uo=0.3V 0.3V

b c

Rc

uo=+VCC ui=UIH

iB≥IBS 0.7V

e

e

+V C C =+5V 例: 1kR c i C Ω uo c Rb b ui β =40 i 10k Ω B e

①ui=1V时,基极电流: 时 基极电流:

第2章 逻辑门电路 章

②ui=0.3V时,因为 BE<0.5V,iB=0, 时 因为u , , 三极管工作在截止状态, 三极管工作在截止状态,ic=0。因 。 为ic=0,所以输出电压: ,所以输出电压:

回首页

第2章 逻辑门电路 章 +VCC=+5V Rc

1kΩ uo c Rb b ui β=40 i 10kΩ B NPN 型三极管截止、放大、饱和 3 种工作状态的特点 e

iC

2、三极管的开关特性

工作状态 条 件

截

止

放

大

饱

和

iB=0 发射结反偏

0<iB<IBS 发射结正偏 集电结反偏 uBE>0,uBC<0 iC=βiB uCE=VCC- iCRc 可变

A

电路图 逻辑符号

Y 1 0

0 1

数字电路 第二章门电路

DA

DB B

DC

Y

C

R

–5v

第2章 2.2

由以上分析可知: 只有当A、B、C全为 低电平时,输出端才 为低电平。正好符合

或门的逻辑关系。

A

B C

>1

Y

Y= A+B+C

三、 非门电路

第2章 2.2

RA A

RB

+5V

Rc uY=0.3V 设 uA= 3.6V,T饱和导通

• Y

uY= 0.3V

T

Y= 0

3. CMOS与非门

TP1 与TP2并联,TN1 与TN2串联;

当AB都是高电平时TN1 与TN2

TP2

同时导通TP1 与TP2同时截止;

输出Y为低电平。

当AB中有一个是低电平时, B

TN1 与TN2中有一个截止,

TP1 与TP2中有一个导通, 输出Y为高电平。

A

第2章 2. 3

+VDD

TP1 Y

正逻辑:L=0,H=1 ; 负逻辑:H=0,L=1 。

2. 1 半导体二极管、三极管和 MOS管的开关特性

一、理想开关的开关特性: 1 .静态特性 2. 动态特性

二、半导体二极管的开关特性 1.静态特性:

半导体二极管的结构示意图、符号和伏安 特性

一、二极管等效模型

(b)为理想二极管+恒压源模型 (c)为理想二极管模型

当D、S间加上正 向电压后可产生 漏极电流ID 。

第2章 2. 1

UDS

。

S UGS G

D ID

N++

NN++

N型导电沟道

耗尽层

数字逻辑电路与系统设计习题答案

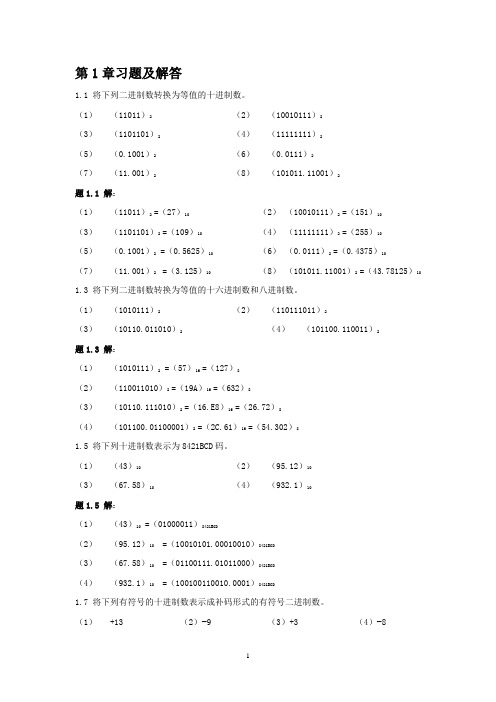

第1章习题及解答1.1 将下列二进制数转换为等值的十进制数。

(1)(11011)2 (2)(10010111)2(3)(1101101)2 (4)(11111111)2(5)(0.1001)2(6)(0.0111)2(7)(11.001)2(8)(101011.11001)2题1.1 解:(1)(11011)2 =(27)10 (2)(10010111)2 =(151)10(3)(1101101)2 =(109)10 (4)(11111111)2 =(255)10(5)(0.1001)2 =(0.5625)10(6)(0.0111)2 =(0.4375)10(7)(11.001)2=(3.125)10(8)(101011.11001)2 =(43.78125)10 1.3 将下列二进制数转换为等值的十六进制数和八进制数。

(1)(1010111)2 (2)(110111011)2(3)(10110.011010)2 (4)(101100.110011)2题1.3 解:(1)(1010111)2 =(57)16 =(127)8(2)(110011010)2 =(19A)16 =(632)8(3)(10110.111010)2 =(16.E8)16 =(26.72)8(4)(101100.01100001)2 =(2C.61)16 =(54.302)81.5 将下列十进制数表示为8421BCD码。

(1)(43)10 (2)(95.12)10(3)(67.58)10 (4)(932.1)10题1.5 解:(1)(43)10 =(01000011)8421BCD(2)(95.12)10 =(10010101.00010010)8421BCD(3)(67.58)10 =(01100111.01011000)8421BCD(4)(932.1)10 =(100100110010.0001)8421BCD1.7 将下列有符号的十进制数表示成补码形式的有符号二进制数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

第2章 逻辑门电路

2.1 题图2.1(a)画出了几种两输入端的门电路,试对应题图2.1(b)中的A、B波形画出各门的输出F1~

F6的波形。

题图2.1

解:

2.2 求题图2.2所示电路的输出逻辑函数F1、F2。

题图2.2

解:

2

2.3 题图2.3中的电路均为TTL门电路,试写出各电路输出Y1~Y8状态。

题图2.3

解: Y1=0, Y2=0, Y3=Hi-Z, Y4=0, Y5=0, Y6=0, Y7=0, Y8=0.

2.4 题图2.4中各门电路为CMOS电路,试求各电路输出端Y1 、Y2和Y的值。

题图2.4

解: Y1=1, Y2=0, Y3=0.

2.5 6个门电路及A、B波形如题图2.5所示,试写出F1~F6的逻辑函数,并对应A、B波形画出

F1~F6的波形。

3

题图2.5

解:

2.6 电路及输入波形分别如题图2.6(a)和2.6(b)所示,试对应A、B、C、x1、x2、x3 波形画出F端波

形。

题图2.6

解:

4

2.7 TTL与非门的扇出系数N是多少?它由拉电流负载个数决定还是由灌电流负载决定?

解: N≤8 N由灌电流负载个数决定.

2.8 题图2.8表示三态门用于总线传输的示意图,图中三个三态门的输出接到数据传输总线,D1D2、

D3D4、…、DmDn为三态门的输入端,EN1、EN2、ENn分别为各三态门的片选输入端。试问:EN信

号应如何控制,以便输入数据D1D2、D3D4、…、DmDn顺序地通过数据总线传输(画出EN1~EN

n

的对应波形)。

题图2.8

解:用下表表示数据传输情况

2.9 某工厂生产的双互补对称反相器(4007)引出端如题图2.9所示,试分别连接成:(1)反相器;

(2)三输入与非门;(3)三输入或非门。

5

题图2.9

解: (1) 反向器

(2)与非门 (3)或非门

2.10 按下列函数画出NMOS电路图。

1

2

3

()()()FABCDEHGFABCDABCDFAB

解:(1)

6

(2) (3)

2.11 将两个OC门如题图2.11连接,试写出各种组合下的输出电压uo及逻辑表达式。

题图2.11

解:

7

2.12 写出题图2.12的电路表达式,并对表达式进行简化。

题图2.12

解: CABCABCABY

2.13 按下列函数画出CMOS电路图。

CDABF

1

BAF

2

解:(1)CDABCDABF1

8

(2) BABABAABABBAF2

2.14 TTL与非门输入端悬空相当于什么电平?输入端阈值电压VT等于多少?输出端F = 0时,能带

动几个同类型TTL与非门?负载个数超出扇出系数越多,输出F变得越高还是越低?

解:TTL与非门输入端悬空相当于高电平;

输入端阈值电压VT=1.4V;

输出端F = 0时,能带动8个同类型TTL与非门;

负载个数超出扇出系数越多,输出F变得越高。

2.15 题图2.15中,G1为TTL三态门,G2为TTL非门,K为开关,电压表内阻为200 k。求下列

情况下,电压表读数F1和G2输出电压F2分别为多少?

(1)A = 0.3 V,B = 0.3 V,C = 0.3 V,K接通。

(2)A = 0.3 V,B = 3.6 V,C = 0.3 V,K断开。

(3)A = 3.6 V,B = 0.3 V,C = 3.6 V,K接通。

(4)A = B = 0 V,C = 3.6 V,K断开。

(5)A = B = 3.63 V,C = 0.3 V,K接通。

题图2.15

解: (1) F1=3.6V, F2=0V

(2) F1=3.6V, F2=0V

(3) F1=3.6V, F2=0V

(4) F1无读数, F2=0V

(5) F1=0V, F2=3.6V

9

2.16 电路如题图2.16(a)所示,试对应2.16(b)的输入波形画出F1、F2的对应波形。

题图2.16

解: EN=0时,F1=BA,F2=BABA

EN=1时,F1=1,F2=A 据此刻在图2.16(b)上画出F1.F2波形如下:

2.17 写出题图2.17中NMOS 电路的逻辑表达式。

题图2.17

解: (a)ABCCBAY1

(b)BABAY2

(c)BABAY3

2.18 写出题图2.18(a)~(c)中各TTL电路的输出逻辑表达式F1、F2和F3,并对应题图2.18(d)所示的

输入A、B、C波形画出F1、F2、、F3波形。

10

题图2.18

解: (a)CACCAFFCCACAFCC111101,1,0,0,1

(b) CBACACBACACABFAFCCABFCC)(,1,0,0,1222

(c) 11,1,01,0,1333CCFFCCFCC

2.19 题图2.19中,G1、G2 为“线与”的两个TTL OC门,G3、G4、G5为三个TTL与非门,若G1、

G2皆输出低电平时,允许灌入的电流IOL为15 mA;G1、G2门皆输出高电平时允许的IOH小于

200 A。G3、G4和G5它们的低电平输入电流为IIL=1.1 mA,高电平输入电流IIH=5 A。Ec(VCC)

= 5 V,要求OC门输出的高电平VOH≥3.2V, 低电平VOL≤0.4V,求负载电阻RL应选多大。

11

题图2.19

解:

maxmin3/5.03.23.27 k(20.230.05)10LCCOHOHIH

RVVnImI

minmax3/5.00.40.39 k(1531.1)10LCCOLOLIL

RVVImI

所以,选定的RL值应在3.27 k与0.39 k之间,可以取RL = 1~2 k。

2.20 写出题图2.20(a)~(c)各TTL门电路的输出逻辑表达式F1、F2和F3。

题图2.20

解: (a) '1AAF

(b) '3'2'13211AAAAAAF

12

(c) BABABABABABAABF3

2.21 写出题图2.21中CMOS电路的输出逻辑表达式F1和F2。

题图2.21

解:

2.22 画出实现下列逻辑函数的CMOS电路。

F1(A、B、C) = AB + C

F2(A、B、C) = AB + CD

解: 1.

2.

13

2.23 简述CMOS电路驱动TTL电路和TTL电路驱动CMOS电路的技术要求。

解: 1.通过第2章中表2-17可以看出,CMOSCC4000系列电路可以直接驱动TTLCT4000系列电路,

这是因为CMOS VOH=4.95V,大于CT4000VIH(2V),VOL=0.05V小于VIL(0.8V);CMOS

IOH=0.5mA大于IIH(20uA),符合匹配原则,故可以直接驱动。

因为IOL

CMOS-TTL电平变换电路有CC4049,CC4050等。

2.TTL电路驱动CMOS电路

因为TTL电路的VOH小于CMOS电路的VIH,所以TTL电路不能直接驱动CMOS电路,可采

用加上接电阻RUF的办法提高TTL电路的输出高电平,如图所示,RUF的电阻值对于CT1000

系列可在209~4.7K之间选择,如果CMOS电路的ED>5V,则须加电平变换电路

2.24 把题图2.24所示的或非门电路变成与或门电路。

题图2.24

解: 与或门电路如右图。

2.25 把题图2.25所示的门电路变换成与非门电路。

14

题图2.25

解: 与非门电路如右图。