第二章逻辑门电路2

数电讲义--2章

1.0

VOL(max)0.5

输入标 准低电

平

0.4V

VNL

D VNH

E

V V 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

SL VOFF VON

SH

Vi (V)

输入标准

高电平

2. 输入特性

+VCC

1) 输入伏安特性

iI

R1 3kΩ

1

-1.6 mA

<50 uA vI A

31

B

T1

1.4 V

和边沿,T4放大。 VO随iOH变化不大。 当由i于Oi以OHH受↑:线时功性,R耗变4上的化压限。降制增,大i0,H过T大3 、会T4烧饱毁和T,4管V,O随所

功耗 1mW IOH 400 A

输出高电平时的扇出系数 3.6V

R2 750Ω 2T3 Vc2 1 3 R4

VO

+VCC

R 4 +5V 100Ω

抗干扰能力越强。 高电平噪声容限

VNH= VSH ¯ VON 。

VNH越大,输入为1态下

抗干扰能力越强。

Vo (V)

4.0 A B

3.5

3.0

VOH(min)2.5 2.4V

C

2.0

1.5

A(0V, 3. 6V) B(0.6V, 3.6V) C(1.3V, 2.48V) D(1.4V, 0.3V) E(3.6V, 0.3V)

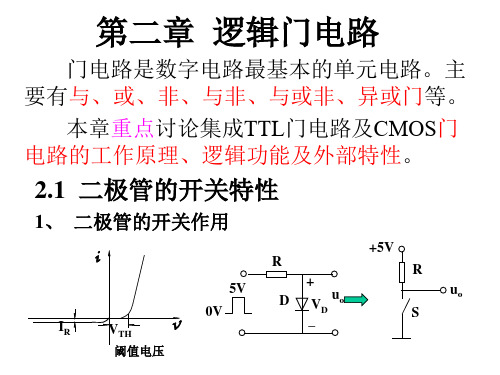

• 导通(VD>VTH) • 2、二极管的开关时间

截止5V(VDR<VT+H)

0V

D VD

uo

_

VF Vi

二极管开关状态的转换需要时间:

t1 t2

第二章逻辑门电路

B

+V’CC RL

A B

&

线与

F A BC D

C

D

& CD

+V’CC RL & &

RL

构成总线输出

:多个逻辑门分时段

&

1

总线负载

共用同一条输出线

20

2.5.6

三态门

VT3

三态门符号 +VCC

VT4 VT2

A B EN

&

EN

VT1

A B EN

D

A B EN

F

VT5

vi vi vo

tpd tpd

vo

应大于tpd ,输出信号vo才能 完成响应。 如输入脉宽小于tpd ,则输出vo 不能产生完整响应,vo会保持 在原电平上基本不变。

(对称方波)

fmax=1/(2tpd)

fmax :

3

传输延迟的仿真

由仿真知, 门延迟 tpd 150nS. 见

vi

25KHz

20uS

IIS IIS 。 1.4mA。

VCC VB1 R1

IIS

vI /V

1.4V

-0.5

IIS

-1.0 -1.5 -2.0

1V

I IS

3K IIS

R1

VCC

vB1

VT2 R3

VO=VOH

VT5

&

IIS

11

或非门(或门) 输入端有多个并接时:

并接接地时, 每个输入端流出电流IIS

IIS

A A•B=A+B VCC

-2~ -1.5V : VIL

第2章 逻辑门电路-习题答案

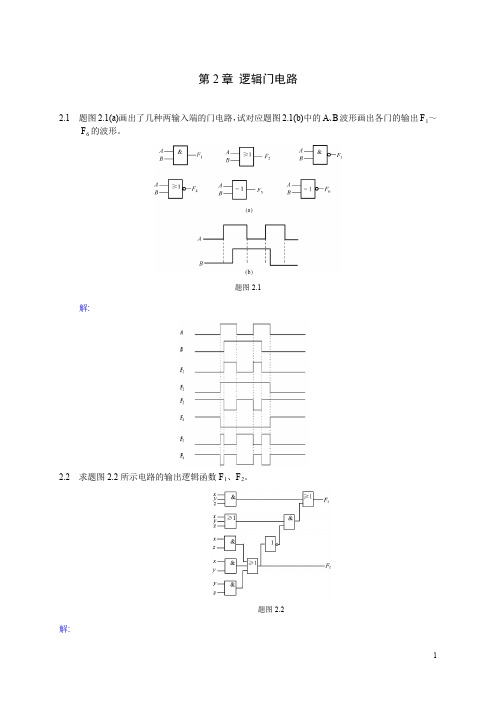

第2章逻辑门电路2.1 题图2.1(a)画出了几种两输入端的门电路,试对应题图2.1(b)中的A、B波形画出各门的输出F1~F6的波形。

题图2.1解:2.2 求题图2.2所示电路的输出逻辑函数F1、F2。

题图2.2解:2.3 题图2.3中的电路均为TTL门电路,试写出各电路输出Y1~Y8状态。

题图2.3解: Y1=0, Y2=0, Y3=Hi-Z, Y4=0, Y5=0, Y6=0, Y7=0, Y8=0.2.4 题图2.4中各门电路为CMOS电路,试求各电路输出端Y1、Y2和Y的值。

题图2.4解: Y1=1, Y2=0, Y3=0.2.5 6个门电路及A、B波形如题图2.5所示,试写出F1~F6的逻辑函数,并对应A、B波形画出F1~F6的波形。

题图2.5解:2.6 电路及输入波形分别如题图2.6(a)和2.6(b)所示,试对应A、B、C、x1、x2、x3波形画出F端波形。

题图2.6解:2.7 TTL与非门的扇出系数N是多少?它由拉电流负载个数决定还是由灌电流负载决定?解: N≤8 N由灌电流负载个数决定.2.8 题图2.8表示三态门用于总线传输的示意图,图中三个三态门的输出接到数据传输总线,D1D2、D3D4、…、D m D n为三态门的输入端,EN1、EN2、EN n分别为各三态门的片选输入端。

试问:EN信号应如何控制,以便输入数据D1D2、D3D4、…、D m D n顺序地通过数据总线传输(画出EN1~EN n 的对应波形)。

题图2.8解:用下表表示数据传输情况2.9 某工厂生产的双互补对称反相器(4007)引出端如题图2.9所示,试分别连接成:(1)反相器;(2)三输入与非门;(3)三输入或非门。

题图2.9解: (1) 反向器(2)与非门 (3)或非门2.10 按下列函数画出NMOS 电路图。

123()()()F AB CD E H G F A B CD AB CD F A B=+++=+++=⊕解:(1)(2) (3)2.11 将两个OC门如题图2.11连接,试写出各种组合下的输出电压u o及逻辑表达式。

第2章 逻辑门电路解题指导

第2章 逻辑门电路解题指导【例2-1】 试用74LS 系列逻辑门,驱动一只V D =1.5V ,I D =6mA 的发光二极管。

解:74LS 系列与之对应的是T4000系列。

与非门74LS00的I OL 为4mA ,不能驱动I D =6mA 的发光二极管。

集电极开路与非门74LS01的I OL 为6mA ,故可选用74LS01来驱动发光二极管,其电路如图所示。

限流电阻R 为Ω=--=--=k V V V R OL D CC 5.065.05.156【例2-2】 试分析图2-2所示电路的逻辑功能。

解:由模拟开关的功能知:当A =1时,开关接通。

传输门导通时,其导通电阻小于1k Ω,1k Ω与200k Ω电阻分压,输出电平近似为0V 。

而A =0时,开关断开,呈高阻态。

109Ω以上的电阻与200k Ω电阻分压,输出电平近似为V DD 。

故电路实现了非逻辑功能。

【例2-3】 试写出由TTL 门构成的逻辑图如图2-3所示的输出F 。

&≥1F≥1A B图2-3 例2-3门电路解:由TTL 门输入端悬空逻辑上认为是1可写出【例2-4】 试分别写出由TTL 门和CMOS 门构成的如图2-4所示逻辑图的表达式或逻辑值。

B F图2-4 例2-4门电路解:由TTL 门组成上面逻辑门由于10k Ω大于开门电阻R ON ,所以,无论 A 、B 为何值 。

由CMOS 门组成上面逻辑门由于CMOS 无开门电阻和关门电阻之说,所以, 。

第3章 组合逻辑电路解题指导【例3-1】 试分析图3-2所示电路的逻辑功能。

VV V 020011DD F ≈+=DD DD 44DD 599F 210101021010V V V V ≈+≈⨯+=A B A F =++⋅=110≡F AB F=FBA 0 5图3-2 例3-1 的逻辑图解:题示电路中74138的A 2=0,使74138变成2线-4线译码器。

AB =00时,00=F ,1321===F F F 。

第02章 逻辑门电路

OC门的几种主要应用

实现线与逻辑

电路如右图所示,逻辑关系为

L L1 L2 AB CD

实现电平转换

如下图所示,可使输出高电平变为+12V

+12V

R

A& 3.4V 0.3V

12V F

0.3V

用作驱动电路

右图是用来驱动发光二极管的电路。

2.3.5 三态门

R1 4K

R2 1.6K

A

T1

T2 B

输出低电平时:NOL = IOLmax / IiLmax 输出高电平时:NOH = IOHmax / IiHmax

考虑最坏的情况,扇出系数:N = min(NL , NH)

TTL与非门的灌电流与拉电流负载

2.3.2 TTL与非门的特性及参数

平均传输延迟时间

tpd = 0.5(tpdL + tpdH ) 输出信号略滞后于输入信号. 典型值:纳秒级

Vo(V) VOH A 2.7

电压传输特性及相关参数 (1) 输出高电平 VOH

R1 4K

R2 1.6K

R4

VCC

130

A

B

B

T1

T3

T2

ቤተ መጻሕፍቲ ባይዱ

D3

F

D1

D2

R3

T4

1K

典型值VOH ≥ 3.4V

VOHmin是满足输出电流指标时, 输出高电平允许的最低值,一 般要求 VOHmin ≥ 2.7V

C

(2) 输出低电平 VOL

(5) 关门电平 VOFF

保证T4截止 输出高电平 时, 输入低电平的最大值.

VOFF ≥ 0.8V

2.3.2 TTL与非门的特性及参数

数字电子技术基础第三版第二章答案

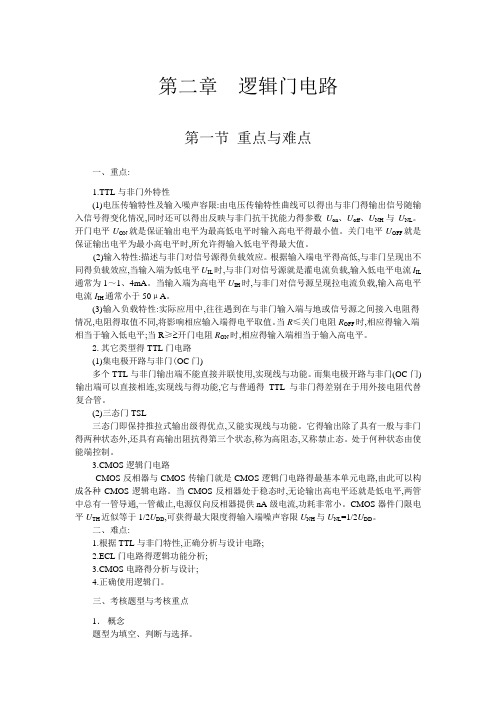

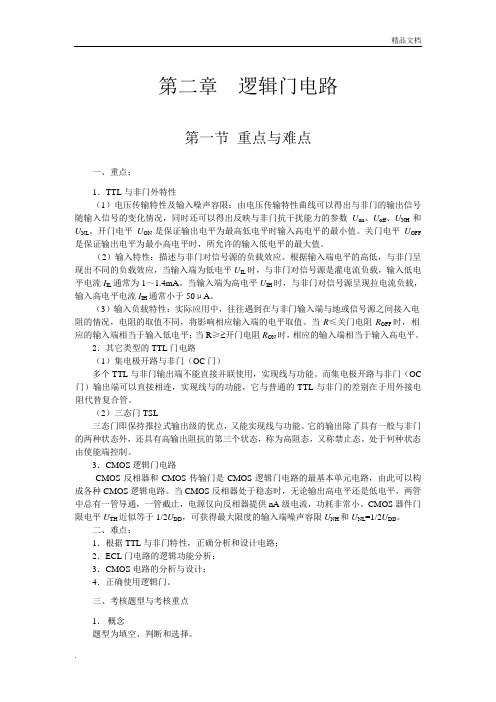

第二章逻辑门电路第一节重点与难点一、重点:1.TTL与非门外特性(1)电压传输特性及输入噪声容限:由电压传输特性曲线可以得出与非门得输出信号随输入信号得变化情况,同时还可以得出反映与非门抗干扰能力得参数U on、U off、U NH与U NL。

开门电平U ON就是保证输出电平为最高低电平时输入高电平得最小值。

关门电平U OFF就是保证输出电平为最小高电平时,所允许得输入低电平得最大值。

(2)输入特性:描述与非门对信号源得负载效应。

根据输入端电平得高低,与非门呈现出不同得负载效应,当输入端为低电平U IL时,与非门对信号源就是灌电流负载,输入低电平电流I IL 通常为1~1、4mA。

当输入端为高电平U IH时,与非门对信号源呈现拉电流负载,输入高电平电流I IH通常小于50μA。

(3)输入负载特性:实际应用中,往往遇到在与非门输入端与地或信号源之间接入电阻得情况,电阻得取值不同,将影响相应输入端得电平取值。

当R≤关门电阻R OFF时,相应得输入端相当于输入低电平;当R≥ 开门电阻R ON时,相应得输入端相当于输入高电平。

2.其它类型得TTL门电路(1)集电极开路与非门(OC门)多个TTL与非门输出端不能直接并联使用,实现线与功能。

而集电极开路与非门(OC门)输出端可以直接相连,实现线与得功能,它与普通得TTL与非门得差别在于用外接电阻代替复合管。

(2)三态门TSL三态门即保持推拉式输出级得优点,又能实现线与功能。

它得输出除了具有一般与非门得两种状态外,还具有高输出阻抗得第三个状态,称为高阻态,又称禁止态。

处于何种状态由使能端控制。

3.CMOS逻辑门电路CMOS反相器与CMOS传输门就是CMOS逻辑门电路得最基本单元电路,由此可以构成各种CMOS逻辑电路。

当CMOS反相器处于稳态时,无论输出高电平还就是低电平,两管中总有一管导通,一管截止,电源仅向反相器提供nA级电流,功耗非常小。

CMOS器件门限电平U TH近似等于1/2U DD,可获得最大限度得输入端噪声容限U NH与U NL=1/2U DD。

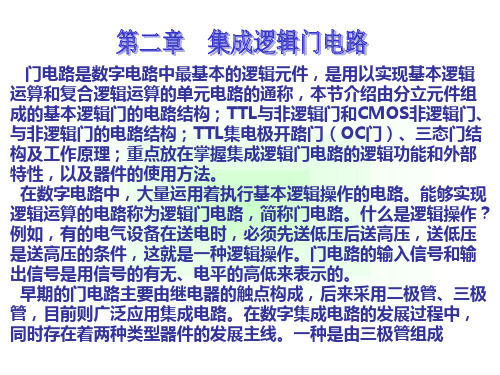

第2章集成逻辑门电路

2.3.2

TTL集电极开路门

TTL集电极开路门(Open Collector Gate)也称为OC门。 在用门电路组成逻辑电路时,如果能将输出端直接并联(称为 “线与”逻辑),可以使电路简化许多。前面所介绍的TTL与非 门却不能这样使用,原因有两个:一是TTL与非门无论输出为高 电平还是低电平,输出电阻都很小;二是两个TTL与非门连在一 起以后,如果一个门输出为高电平,另一个输出为低电平,那么 会有很大的电流从截止门的三极管VT4流到导通门的三极管VT5, 此电流大大超过正常工作电流,严重时会损坏门电路。解决的办 法是把TTL与非门电路的输出级改为集电极开路的三极管结构,

图2.25

二极管的开关电路特性

2.双极型三极管的开关特性 双极型三极管的输出特性曲线如图2.26所示。由输出特性曲线 可知,三极管可分为三个区域:截止区、放大区和饱和区。特别 当三极管工作在截止区和饱和区时,电参数也表现为对立的两个 状态,可以作为开关使用。

图2.26

三极管的输出特性曲线

2.2

晶体二极管和三极管的开关特性

第一个字母C代表中国,T代表TTL;它们对应型号的门电路逻辑 功能和引脚图与国际标准基本是一样的。本书电路举例将以最常 用的74XX系列和74LSXX系列门电路为主。本章讨论的集成逻辑门 属于小规模集成电路(SSI)。

2.3.1

TTL与非门电路

1.电路结构 每个系列的TTL与非门基本都是由输入级、中间级(倒相级) 和输出级组成。图2.30为TTL与非门的基本电路。 输入级通常由多发射极晶体三极管组成,如图中VT1。我们可 以把VT1看成是发射极独立而基极和集电极分别并联在一起的三 极管。输入级完成“与”逻辑功能。 中间级由VT2组成,其集电极和发射极输出的信号相位相反。 由这两个相位相反的信号去控制输出级的VT3和VT5,所以中间级 也称倒相级。 输出级由VT3、VT4和VT5组成,采用推拉式结构。其中VT3、

数字电子技术基础第三版第二章答案

第二章逻辑门电路第一节重点与难点一、重点:1.TTL与非门外特性(1)电压传输特性及输入噪声容限:由电压传输特性曲线可以得出与非门的输出信号随输入信号的变化情况,同时还可以得出反映与非门抗干扰能力的参数U on、U off、U NH和U NL。

开门电平U ON是保证输出电平为最高低电平时输入高电平的最小值。

关门电平U OFF 是保证输出电平为最小高电平时,所允许的输入低电平的最大值。

(2)输入特性:描述与非门对信号源的负载效应。

根据输入端电平的高低,与非门呈现出不同的负载效应,当输入端为低电平U IL时,与非门对信号源是灌电流负载,输入低电平电流I IL通常为1~1.4mA。

当输入端为高电平U IH时,与非门对信号源呈现拉电流负载,输入高电平电流I IH通常小于50μA。

(3)输入负载特性:实际应用中,往往遇到在与非门输入端与地或信号源之间接入电阻的情况,电阻的取值不同,将影响相应输入端的电平取值。

当R≤关门电阻R OFF时,相应的输入端相当于输入低电平;当R≥ 开门电阻R ON时,相应的输入端相当于输入高电平。

2.其它类型的TTL门电路(1)集电极开路与非门(OC门)多个TTL与非门输出端不能直接并联使用,实现线与功能。

而集电极开路与非门(OC 门)输出端可以直接相连,实现线与的功能,它与普通的TTL与非门的差别在于用外接电阻代替复合管。

(2)三态门TSL三态门即保持推拉式输出级的优点,又能实现线与功能。

它的输出除了具有一般与非门的两种状态外,还具有高输出阻抗的第三个状态,称为高阻态,又称禁止态。

处于何种状态由使能端控制。

3.CMOS逻辑门电路CMOS反相器和CMOS传输门是CMOS逻辑门电路的最基本单元电路,由此可以构成各种CMOS逻辑电路。

当CMOS反相器处于稳态时,无论输出高电平还是低电平,两管中总有一管导通,一管截止,电源仅向反相器提供nA级电流,功耗非常小。

CMOS器件门限电平U TH近似等于1/2U DD,可获得最大限度的输入端噪声容限U NH和U NL=1/2U DD。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电路中D 3、D 4的作用是提高开关速度,当U o 由1跳到0时,经D 3、D 4提供放电回路,加速U o 的下降速度。

R 4电阻由接地改为接在U o 上的目的是降低静态功耗,R 1电阻取值改为20k Ω也是为了降低电路的功耗。

该电路的电阻值比TTL 门电路相应的电阻值大,主要目的是降低电路的功耗。

实现的是与非的逻辑功能。

电路中二极管采用肖特基二极管,其正向导通压降为,而肖特基三极管的发射极的正偏电压为,集电极的正偏电压为。

因此,电路的阈值电压将变为:D BE5BE2T U U U U -+==+输出的高低电平值:U OH = U OL =。

输入端的短路电流I IL =0.23mA 200.45=- 习题 习题图TTL 与非门电路所示的电路中,若在某一输入端与地之间接一电阻R ,其余输入端悬空,试问:⑴保证与非门可靠关闭时的最大电阻即关门电阻R OFF 为多大值 ⑵保证与非门可靠开通时的最小电阻即开门电阻R ON 为多大值解:若在输入端A 与地之间接一电阻R i ,则R i 与地之间的电压U i 为:(1)i ii R R R U U U ⨯+-=1be1cc ≤OFF U即i R ⨯+-R 30.75≤ R i ≤? R OFF ?700?(2) i ii R R R U U U ⨯+-=1be1cc ≥on U 即i R ⨯+-R30.75≥ 由此可得:R i ≥? , 一般选R ON =2k?1.4V T 1be1cc ==⨯+-U R R R U U i i工程计算:得 R ON =R OFF ??习题 习题图所示电路由TTL 与非门组成。

设G 1~G 4门的平均传输延迟时间相同为30ns ,现测得输出端F 的振荡频率为,试求G 5的平均传输延迟时间t pd5。

解:根据F 的频率求出F 的振荡周期,T =,由于五个与非门输出为原信号的非,所以延迟时间应为T /2≈156ns ,则第五个与非门的延迟时间为36ns 。

习题图F习题 有两个TTL 与非门芯片,测得它们的关门电平分别为U OFFA =,U OFFB =;开门电平分别为U ONA =,U ONB =。

它们输出的高电平和低电平相同,试判断哪一个门的抗干扰能力大解:描述门电路的抗干扰能力的大小通常用噪声容限U N 来衡量。

通常噪声容限电压U N越大,门电路的抗干扰能力越强。

低电平噪声容限U NL 是指在保证输出高电平的前提下,允许叠加在关门电平U OFF 上的最大正向干扰电压。

OL OFF NL U U U -=高电平噪声容限U NH 是指在保证输出低电平的前提下,允许叠加在开门电平上的最大负向干扰电压。

ON OH NH U U U -=由于两个门的输出的高电平和低电平相同,而开门电平和关门电平却不相同,因此抗干扰能力是不同的。

低电平噪声容限U NL :OL OL OFFA NLA 1.1 U U U U -=-= OL OL OFFA NLB 0.9U U U U -=-=可知: NLA U ≥NLB U 高电平噪声容限U NH :3.1 OH ONA OH NHA -=-=U U U U 7.1OH ONB OH NHB -=-=U U U U可知:NHA U ≥NHB U综上分析可知:门A 的抗干扰能力比门B 大。

习题 习题图(a )所示电路中,输出 F 与C 1和C 2之间具有与逻辑关系,称为线与,用 虚线框标注。

试写出F 与C 1和C 2之间的电平关系表、真值表和逻辑式,并画出等效的逻辑图。

解:由电路图可知,当A 和B 中有一个为高 电平时,设A 为高电平,它所对应的三极管T 1将 饱和导通,C 1为低电平,此时输出F 也为低电平。

当A 和B 中全为低电平时,两个三极管T 1 和T 2均截止,C 1和C 2为高电平,此时输出F 也为高电平。

由此可得出电路的电平关系表如习题表所示采用正逻辑体制进行描述,高电平用逻辑1来表示,低电平用逻辑0来表示,可得描述电路逻辑关系的真值表如习题表所示。

由真值表写出电路的逻辑表达式:21C C F ⋅=电路的等效图如习题图(b )所示。

习题 若要实现习题图中各TTL 门电路输出端所示的逻辑功能,各电路的连接是否正确习题图C FA C 1 C 2F(b )(a )如果不正确,试说明理由。

解:本题目涉及TTL 门电路的正确使用的问题,解题时主要从以下几个方面来判断: 1. 门电路的多余输入端的处理; 2. 门电路输入负载的要求; 3. 输出端不能直接相接;4. 带载能力的问题。

(a) 正确;(b) 错误,F =0; (c) 错误,F =0;(d) 正确;(e) 错误,TTL 门电路输出端不能直接并联; (f) 错误,F =0。

习题 习题图(a)所示的电路中, 输出F 与E 1和E 2之间具有或逻辑关系,称 为线或,用虚线框标注。

试写出F 与E 1和 E 2之间的电平关系表、真值表和逻辑式,并画出等效的逻辑图。

解:由习题图(a)(设A 为高电平),它所对应的三极管T 1饱和导通,E 1为高电平,此时输出F 为高电平。

当A 和B 中全为低电平时,两个三极管T 1和T 2均截止,E 1和E 2为低电平,输出F 也为低电平。

由此可得出电路的电平关系表如习题表所示。

(a ) A B A C 习题图F 1=ABB F 4=A +B (d ) A B5=ABCD (e ) DA B F 2=AB (b ) A B F 3=A +B (c ) F 6=AB +CD (f ) B C D F A (a) 习题图(b)FE E采用正逻辑体制进行描述,高电平用逻辑1来表示,低电平用逻辑0来表示,可得描述电路逻辑关系的真值表如习题表所示。

由真值表写出电路的逻辑表达式:21E E F +=电路的等效图如习题图(b)所示。

习题 分析如习题图所示的逻辑电路,写出输入信号与输出信号之间的逻辑表达式。

解:(a)当C =1时,下面的三态门为与非门正常工作,则F 1=B ;当C =0时,F 1=A ;所以,BC C A F +=1(b)B A F ⊕=习题 TTL 电路如习题图(a )、(b )所示,试写出输出端的表达式。

已知 输入信号A 、B 、C 的波形如习题图(c )所示,画出对应的输出波形。

解: (a) ()C B A C B A F ⊕=+⊕=1,如习题图(d )所示F 1波形。

(b) C B B C A F +⊕=)(2,如习题图(d )所示F 2波形。

习题 电路如习题图(a )~(g )所示,已知输入信号A 、B 的波形如习题图(h )所示,画出各电路的输出波形。

解:本题给出一组TTL 门电路以及CMOS 门电路,要求在给定输入信号波形下,对应画习题图 (a ) A C B F 1(b )A B F 2习题图AB (b )C F 2(a ) A B F 1C (c )BAC (d ) B AC F 2F 1出各输出端的波形。

由于所有门的一个输入端都通过电阻接地,电源通过这一电阻到地形成电流通路,电阻两端将产生电压降, 这一电压必将构成门电路的一个输入信号。

对于TTL 门电路,要求掌握关门电阻R OFF 与开门电阻R ON 的含义及其作用。

对于CMOS 门电路,由于无栅流存在,输入端接电阻到地,相当于低电平输入方式。

TTL 电路若有输入端通过电阻接地,根据TTL 门电路的输入端负载特性可知,当R <?时,U R <U OFF ,构成低电平输入方式,这一电阻通常也称为关门电阻,记为R OFF ;当R >?时,U R >U on ,构成高电平输入方式,这一电阻通常也称为开门电阻,记为R ON 。

对于CMOS 门电路,由于栅极无栅流。

若输入端接一电阻到地,相当于栅极电位为地电位,构成低电平输入方式。

根据以上分析,各电路输出与输入量的关系式为:11=F B A F ⋅=2 13=F 14=F B F =5 B A F +=6 A F =7 对应于输入信号A ,B 的波形可画出相应的波形图,如习题图(i)所示。

习题 在习题图所示的各电路中,给定输入波形,试画出各输出端的波形。

A B (h) AB(i) F 1 F 2 F 3 F 4F 7 F 5 习题图(b)A B F 1 (a) F 5 TTLA B(e)(d) (g) (c) A B2 AB F 3 AB 4 CMOSA 7 (f)A F6B F 6ABF 1F 2 A B F 3A B解:首先根据电路图判断各个电路的输出与输入的逻辑关系。

(1)由习题图(a )可得出描述输入与输出逻辑关系的逻辑表达式为B A F +=1。

当输入有高电平出现时,输出为低电平;当输入全为低电平时,输出为高电平。

(2)由图习题图(b )可看出后级与非门的输入由前级三态门的输出和输入量C 决定,输入量B 为三态门的使能控制端,当B 为低电平时,三态门开启,输出F 2由A 和C 决定;当B 为高电平时,三态门处于高阻状态,输出F 2仅由C 决定。

由此可得描述电路输入与输出逻辑关系的逻辑表达式:时1时0 2==⋅⎩⎨⎧=B C B C A F (3)由习题图(c )可得出描述输入与输出逻辑关系的逻辑表达式为:AB F =3当输入有低电平出现时,输出为高电平;当输入全为高电平时,输出为低电平。

(4)由图习题图(d )可得出描述输入与输出逻辑关系的逻辑表达式为:D C B A F ⊕⊕⊕=4当输入有奇数个高电平出现时,输出为高电平;当输入有偶数个高电平出现时,输出为低电平。

然后根据给定的输入波形及输入与输出之间的逻辑关系画出相应的输出波形图如习题图(f )所示。

习题 习题图为ECL 门电路逻辑图,试写出F 1、F 2和F 3的逻辑表达式。

解:ECL 电路具有或/或非互补输出端且采用射极开路形式,允许多个输出端直接并联,以实现输出变量的“线或”操作。

通过分析电路得到B A F +=1F 2和F 3为三个和两个ECL 门输出直接相并 联后的输出,完成的是线或的逻辑功能。

其输出1A B表达式为:F E D C B A F +++++=2F E D C F +++=3习题 画出用最少数量的扇入为2的ECL 或/或非门实现下列操作的逻辑图。

))(())((21H G F E D C B A F FE D C B AF +++++=+++++=解:本题利用ECL 输出变量的“线或”操作功能 实现要求的或逻辑功能。

欲实现F E D C B A F +++++=1,用扇入为 2的ECL “或/或非”门需门电路3个。

))(())((2H G F E D C B A F +++++=H G F E D C B A +++++++=欲用扇入为2的ECL “或/或非”门需要的门 电路4个,实现电路如习题图所示。