状态机例子-自动售货机

生活中有限状态机

货币有0.5,1.0,机器可找零,每次投入一种硬币,机器可以输出货物,也可找零:

二,从

这仅仅只是投币这一动作的状态图,其实展开来说我觉得单顾客而言还有很多个动作状态,比如选择饮料这一动作,如下图:

选择

人本来就是一个复杂的个体,信息输入人脑后还会有一系列的状态。

二.售货机器来分析

售货机根据顾客的投币来找零和出货,售货机对顾客的输入进行识别后出货并判断顾客投币是否足够是否需要找零:

对于售货机,我觉得售货机也有很多个状态,比如,顾客选择饮料后按键,售货机会根据按键计算该吐出哪种饮料,然后饮料下的挡板收缩,该饮料就掉下来了:

三,从补货售货员来分析

补货员又分为两个部分,查看及取走钱币及查看及补充饮料:

自动售货机类图:

有限状态机是一种具有离散输入输出系统的模型,在任何时刻都处于一个特定的状态。对于事件驱动的程序设计,它是非常有用的设计模型。在某一个状态下有事件发生时,根换到下一个状态。

自动售货机我想从三个方面来分析它的有限状态机(以下是用例图):

一,从顾客来分析

《游戏智能》

实验报告

项目名称生活中的有限状态机

专业班级20121123

姓 名骆晓芳(2012137125)

实验成绩:

批阅教师:

2014年12月19 日

生活中的有限状态机——自(英语:Finite-state machine, FSM),又称有限状态自动机,简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。

离散数学有限自动机模型应用举例

离散数学有限自动机模型应用举例离散数学是数学的一个分支,主要研究离散对象和离散关系。

而有限自动机是离散数学中的重要概念之一,用于描述具有有限数量的状态和状态之间的转换关系。

有限自动机模型在计算机科学和其他领域中有着广泛的应用。

本文将从几个具体的应用案例来探讨离散数学有限自动机模型的应用。

案例一:自动售货机自动售货机是我们日常生活中常见的一种自动化设备。

它通过有限自动机模型来实现对商品的管理和售卖。

假设自动售货机有3个状态,分别为“待机”、“选择商品”和“完成交易”。

当用户投入硬币后,自动售货机会从“待机”状态转换为“选择商品”状态,用户可以通过按下相应按钮来选择商品。

一旦用户选定商品,自动售货机将通过有限自动机模型转换到“完成交易”状态,并同时释放商品和找零。

这个案例清晰地展示了有限自动机模型如何应用于自动售货机的控制。

案例二:电话拨号电话拨号也是离散数学有限自动机模型的一个应用。

在传统电话中,数字键盘上有10个数字按钮和几个特殊按钮(如*和#)。

每次按下一个按钮时,电话系统都会根据当前状态和按下的按钮进行状态转换。

例如,当你拨号时,初始状态为“待命”状态,按下数字按钮后,系统将从“待命”状态转移到“拨号中”状态,并显示所拨的号码。

这个过程中,电话系统一直在根据当前状态和按下的按钮进行状态转换,直到通话结束。

这种电话系统的设计正是基于离散数学有限自动机模型,它能够准确地响应用户的操作。

案例三:词法分析器在计算机科学中,词法分析器是编译器的一个基本组成部分,用于将源代码分解为有意义的元素(如标识符、关键字和运算符)。

离散数学有限自动机模型可以用来构建词法分析器。

通过使用有限自动机,可以将源代码作为输入,并根据代码的语法规则将其分解为不同的词法单元。

例如,当遇到空格时,词法分析器将从初始状态转换到“空格”状态,并且继续分析后续字符。

同样地,当遇到标识符或关键字时,词法分析器将进行相应的状态转换并识别它们。

事件驱动 状态机 实例讲解 -回复

事件驱动状态机实例讲解-回复什么是事件驱动?事件驱动(Event-driven)是一种计算机编程范例,它通过响应事件的方式来控制程序的执行流程。

事件驱动编程是一种反应性编程方法,它基于事件的发生而触发相应的处理流程。

在事件驱动的程序中,程序状态通常是静态的,只有当外部事件发生时,程序才会进入相应的处理流程,执行相关的代码。

事件驱动的编程模型可以适用于多种情况,如图形用户界面(GUI)开发、网络编程、服务器开发等。

在这些场景下,用户的操作、网络请求、外部设备的输入等都可以被视为事件,并通过事件驱动模型进行处理。

不同于传统的顺序编程模型,事件驱动模型具有以下几个特点:1. 程序按照事件顺序响应:程序会等待事件发生,然后根据事件的顺序依次进行处理。

事件驱动编程通常具有异步的特性,即不会一直等待事件的发生,而是可以同时处理多个事件。

2. 事件处理是离散的:每个事件都会有相应的处理流程,事件之间是相互独立的。

这使得程序能够更好地适应外部环境的变化。

3. 事件驱动编程具有高度的灵活性和可扩展性:由于事件驱动模型基于事件的发生来触发相应的处理流程,使得程序可以根据实际需求进行动态调整和扩展。

4. 事件驱动模型对并发和并行编程友好:事件驱动编程天然支持多线程、多任务并发执行。

不同的事件可以由不同的线程或进程处理,从而提高程序的执行效率和响应性。

什么是状态机?状态机(State machine)是一种将系统行为建模的数学模型。

它描述了一个系统的内部状态以及状态之间的转换规则。

状态机由一组状态和状态转移构成,状态表示系统所处的状态,转移表示状态之间的切换。

状态机可以分为两种类型:有限状态机(Finite-state machine,FSM)和无限状态机(Infinite-state machine)。

有限状态机中,状态的数量是有限的,系统的状态会在不同的输入条件下从一个状态转移到另一个状态,形成一个状态转移图。

无限状态机中,状态的数量是无限的,系统的状态可能具有连续性或无规律性。

有限状态机-售货机例子

S0

11 / 1 10 / 0

S1

11 / 0

米勒型状态机 状态转换图

01 / 0 1x/1 01 /1 1x /1 10 / 0

S3

输出与输入有关

01 / 0

S2

00 / 0

00 / 0

下一状态 输入

当前状态

状态译码 (下一状态组合逻组合逻辑)

输出

module vend_moore(Reset , Clk , D_in , D_out); ……

竞争冒险不能消除。

摩尔型状态机输入与输出隔离,输出稳定,能

测试分析

有效消除竞争冒险,是设计首选。

always @(current_state ) …… // 输出译码

always @(current_state ) D_out_moore= (current_state==S4); endmodule

通过测试平台进行功能仿真, 并与米勒型状态机进行对比。

测试分析

仿真结果分析:

米勒型状态机输出与当前状态和输入都有关,

……

S1:begin if (D_in[1] & D_in[0]) next_state<=S4; else if (D_in[1]) next_state<=S3; else if(D_in[0]) next_state<=S2; else next_state<=S1; end S2:begin ……

程序实现

always @(current_state or D_in) begin …… // 状态译码 end

always @(posedge Clk or posedge Reset) begin …… // 状态寄存 end always @(current_state ) …… // 输出译码 endmodule

SOC设计实验报告

#2 five_cents=0; //5 两个五分,一个十分 #20 five_cents=1; #2 five_cents=0; #10 five_cents=1; #2 five_cents=0; #10 ten_cents=1; #2 ten_cents=0; #10 $stop; end AUTOSEL AUTOSEL(five_cents,ten_cents,clk,rst_n,soda_out); Endmodule 测试波形图如下所示:

Wire Load Model Mode: Ie_reg[0]

(rising edge-triggered flip-flop clocked by clk)

Endpoint: out (output port clocked by clk)

Path Group: clk

1 Five

input rst;

output out; wire out;

=1 ten=

Five= 1 St2

reg [1:0]state;

1

parameter st0=2'b00,

st1=2'b01,

st2=2'b10,

st3=2'b11;

always@(posedge clk or negedge rst)

490.20 490.20

clock network delay (ideal)

20.00 510.20

clock uncertainty

-20.00 490.20

output external delay

-80.00 410.20

data required time

410.20

-----------------------------------------------------------

数字逻辑状态机例子

Digital System Design12011/6/21Computer Faculty of Guangdong University of Technology例:用三进程状态机实现一个简单自动售货机控制电路,电路框图如下。

该电路有两个投币口(1元和5角),商品2元一件,不设找零。

In[0]表示投入5角,In[1]表示投入1元,Out 表示是否提供货品。

Digital System Design22011/6/21Computer Faculty of Guangdong University of Technology根据题意,可分析出状态机的状态包括: S0(00001):初始状态,未投币或已取商品 S1(00010):投币5角 S2(00100):投币1元 S3(01000):投币1.5元 S4(10000):投币2元或以上用独热码表示状态编码,如上所示。

相应状态转换图如下(按Moore 状态机设计)。

Digital System Design32011/6/21Computer Faculty of Guangdong University of Technology自动售货机状态转换图Digital System Design42011/6/21Computer Faculty of Guangdong University of Technology设计代码第一个Always 块:状态转移。

Digital System Design52011/6/21Computer Faculty of Guangdong University of Technology第二个Always 块:状态转移的组合逻辑条件判断Digital System Design62011/6/21Computer Faculty of Guangdong University of Technology第三个Always 块:输出组合逻辑Digital System Design72011/6/21Computer Faculty of Guangdong University of Technology测试平台代码Digital System Design82011/6/21Computer Faculty of Guangdong University of Technology功能仿真结果Digital System Design92011/6/21Computer Faculty of Guangdong University of Technology综合结果。

有限状态机课程设计报告EDASodaMachine自动售货机

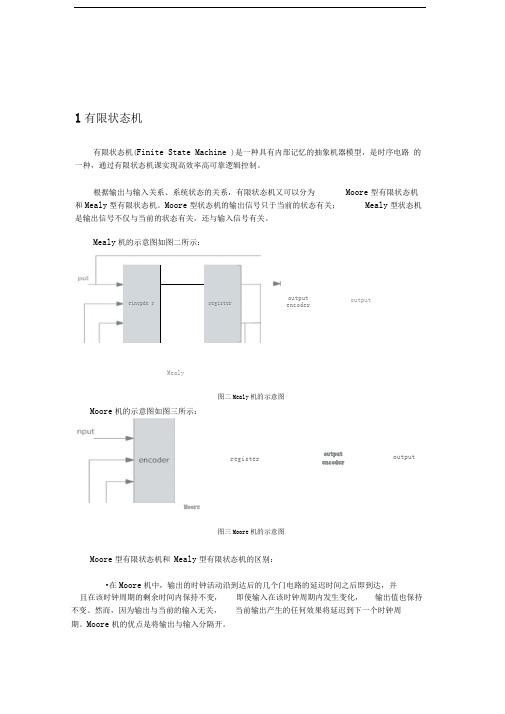

1有限状态机有限状态机(Finite State Machine )是一种具有内部记忆的抽象机器模型,是时序电路的一种,通过有限状态机课实现高效率高可靠逻辑控制。

根据输出与输入关系、系统状态的关系,有限状态机又可以分为Moore型有限状态机和Mealy型有限状态机。

Moore型状态机的输出信号只于当前的状态有关;Mealy型状态机是输出信号不仅与当前的状态有关,还与输入信号有关。

Mealy机的示意图如图二所示:Mealy图二Mealy机的示意图Moore机的示意图如图三所示:Moore图三Moore机的示意图Moore型有限状态机和Mealy型有限状态机的区别:•在Moore机中,输出的时钟活动沿到达后的几个门电路的延迟时间之后即到达,并且在该时钟周期的剩余时间内保持不变,即使输入在该时钟周期内发生变化,输出值也保持不变。

然而,因为输出与当前的输入无关,当前输出产生的任何效果将延迟到下一个时钟周期。

Moore机的优点是将输出与输入分隔开。

einepde r registeroutputencoderoutputregisteroutputencoderoutput• 在Mealy 机中,因为输出是输入的函数,如果输入改变,则输出可以在下一个时钟周期的中间发生改变。

这使得Mealy 机比Moore 机,对输入变化的响应要早一个时钟周期,一旦输入信号或状态发生变化,输出信号随着输入信号变化。

• 实现同样功能,Moore 机要比Mealy 机需要更多的状态。

通过分析本次实验,利用Mealy 机更加容易理解,并且使用Moore 会使用更多的状态,所以本次实验使用Mealy 型有限状态机。

2 Soda Machine机的设计2.1 Soda Machine机的状态转换图Soda Machine 机的状态转换图如图四所示。

Soda Machine图四Soda Machine 机的状态转换图图中共有10个状态,为ST0 — ST9。

工程实训报告-Modelsim实验四-有限状态机之自动售货机-(1)

实验项目名称:有限状态机指导教师:实验日期:实验概述:【实验目的及实验设备】实验目的:(1)掌握有限状态机的应用方法。

(2)掌握有限状态机的静态测试方法,能够进行程序设计。

(3)学习测试模块的编写,综合和不同层次的仿真。

(4)用有限状态机设计一个自动售货机(饮料价格为2.5元)。

实验设备及仪器名称:CPU型号:英特尔*****************************操作系统类型:Windows XP SP3仿真软件:MAX Plus 2软件、Modelsim SE-64 10.0c实验内容及步骤:【实验原理及电路图】系统能够根据用户输入的硬币,判断钱币是否足够,当所投硬币达到或者超过购买者所选面值时,则根据顾客的要求自动售货,并找回剩余的硬币,然后回到初始状态,当所投硬币面值不够时,则给出提示,并通过一个复位键退回所投硬币。

然后回到初始状态。

该实验输入有4个clk,reset,表示投一元币y,表示投五角币w。

输出有2个,表示饮料出现的out和找五角钱的w_out.该实验共5个状态,s0:表示投币为0的状态,s1:表示投入5角的,s2:表示投入1元,s3:表示投入1.5元,s4:表示投入2元。

当投入2.5时out输出1,状态回到s0,当投入3元时out 和w_out都输出1,状态回到s0.【实验方案】(实验步骤,记录)1、打开Modelsim SE-64 10.0c软件。

else beginout=0;w_out=0;s=s4;endendcaseendendmodule测试程序:module shou;wire y;reg w;reg reset;reg clk;paramerer clkperiod=100;shouhuoji shou(y,w,reset,clk)initial beginw=0;clk=0;reset=1;#150 reset=0;#100 reset=1;endalways#(clkperiod/2) clk=~clk;always#(clkperiod+30) $random;initial $monitor(Stime, “y=%b”,y);endmodule3、编译并调试程序,出现错误立即修改直至无错误出现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Digital System Design

1

2011/6/21

Computer Faculty of Guangdong University of Technology

例:用三进程状态机实现一个简单自动售货机控制电路,电路框图如下。

该电路有两个投币口(1元和5角),商品2元一件,不设找零。

In[0]表示投入5角,In[1]表示投入1元,Out 表示是否提供货品。

自动 售货机

In[0] In[1] Clk Reset

Out

自动售货机顶层结构框图

Digital System Design

2

2011/6/21

Computer Faculty of Guangdong University of Technology

根据题意,可分析出状态机的状态包括: S0(00001):初始状态,未投币或已取商品 S1(00010):投币5角 S2(00100):投币1元 S3(01000):投币1.5元 S4(10000):投币2元或以上

用独热码表示状态编码,如上所示。

相应状态转换图如下(按Moore 状态机设计)。

Digital System Design

3

2011/6/21

Computer Faculty of Guangdong University of Technology

xx/1

01/0 10/0

10/0

01/0

01/0

S1

S0

S4

S2

Reset

自动售货机状态转换图

10/0

S3

01/0

x1/0

Digital System Design

4

2011/6/21

Computer Faculty of Guangdong University of Technology

设计代码

第一个Always 块:状态转移。

`timescale 1ns/100ps

module saler_3always(Reset,Clk,In,Out); input Clk,Reset; input [1:0] In; output Out; reg Out;

reg [4:0] state, next_state;

parameter S0=5'b00001, S1=5'b00010, S2=5'b00100, S3=5'b01000,S4=5'b10000; always @(posedge Clk or posedge Reset)

Digital System Design

5

2011/6/21

Computer Faculty of Guangdong University of Technology

begin if (Reset) state<=S0; else

state<=next_state; end

第二个Always 块:状态转移的组合逻辑条件判断

always @(state or In) begin case(state)

S0:begin if (In[1]) next_state<=S2;

Digital System Design

6

2011/6/21

Computer Faculty of Guangdong University of Technology

else if(In[0]) next_state<=S1;

else

next_state<=S0; end S1:begin if (In[1]) next_state<=S3; else if(In[0]) next_state<=S2; else

next_state<=S1;

end S2:begin if (In[1]) next_state<=S4; else if(In[0]) next_state<=S3;

else

next_state<=S2; end S3:begin

if (In[0]|In[1]) next_state<=S4;

Digital System Design

7

2011/6/21

Computer Faculty of Guangdong University of Technology

else

next_state<=S3; end S4:begin

next_state<=S0;

end

default:next_state<=S0; endcase end

第三个Always 块:输出组合逻辑

always @(state ) begin

case(state) S0:begin

Out<=0; end S1:begin Out<=0;

Digital System Design

8

2011/6/21

Computer Faculty of Guangdong University of Technology

end S2:begin

Out<=0;

end S3:begin Out<=0; end

S4:begin

Out<=1;

end

default:Out<=0; endcase end endmodule

测试平台代码

Digital System Design

9

2011/6/21

Computer Faculty of Guangdong University of

Technology

`timescale 1ns/1ns module testbench_saler; reg clk,reset; reg [1:0] in; wire out;

parameter DELY=20; saler_3always

tb(.Clk(clk),.Reset(reset),.In(in),.Out(out)); always #(DELY/2) clk = ~clk; initial begin

clk=0; reset=0;

#20 reset=1;

#20 reset=0;

end

initial begin in=0; repeat(20)

#20 in=$random; end

Digital System Design

10

2011/6/21

Computer Faculty of Guangdong University of

Technology

initial #400 $finish;

endmodule

功能仿真结果

Digital System Design 11

2011/6/21 Computer Faculty of Guangdong University of Technology

综合结果

Digital System Design Array

12

2011/6/21 Computer Faculty of Guangdong University of

Technology。