制作一个正弦信号发生器的设计

正弦信号发生器的设计实验报告(2013070619)

正弦信号发生器的设计

一、实验目的

1、进一步熟悉QuartusII软件的使用,掌握可编程器件的开发设计的过程。

2、掌握QuartusII中国宏模块的使用方法,重点是LMP_ROM与FPGA硬件资源的使用方法。

3、进一步熟悉GW48-PK2 EDA实验系统。

二、实验内容

采用图形输入方法完成以下正弦信号发生器的设计。

其中6为二进制加法计数器采用兆功能库的arithmetic中的lpm_counter来实现。

ROM元件采用storage中的lpm_rom实现。

ROM数据表中的正弦信号为64字节。

操作如下:

1、新建工程文件,取名为SIN。

2、创建初始化文件,为SIN.mif。

3、建立LPM_ROM.

4、建立LPM_COUNTER文件

5、绘制电路图及编译

6、仿真波形的建立与存盘

7、仿真波形前的检查、仿真,检查结果

8、波形仿真前的检查,进行仿真,检查结果。

9、绑定管脚,进行仿真

10、下载程序,在实验箱上验证结果。

11、重复前面的步骤,设计多波形的信号发生器。

(老师对不起,由于我实验的照片找不到了,就借用了同学的多波形的图片。

)。

基于fpga的dds正弦信号发生器的设计和实现

基于FPGA的DDS正弦信号发生器的设计和实现引言在电子领域中,正弦信号是一种重要的基础信号,被广泛应用于通信、音频、视频等各个领域。

而DDS(Direct Digital Synthesis)直接数字合成技术则是一种通过数字方式生成高精度、高稳定性的正弦波信号的方法。

本文将详细介绍基于FPGA的DDS正弦信号发生器的设计和实现。

设计目标本次设计旨在实现一个可配置频率范围广泛且精度高的DDS正弦信号发生器。

具体设计目标如下: 1. 实现频率范围可调节,覆盖从几Hz到数十MHz; 2. 提供高精度的频率控制,满足特定应用场景对频率稳定性和相位精度的要求; 3. 支持模数转换器(DAC)输出,并能够通过外部接口控制输出幅值; 4. 使用FPGA作为主要硬件平台,以满足高速计算和灵活配置需求。

系统架构基于FPGA的DDS正弦信号发生器主要由以下几个部分组成: 1. 数字控制模块(Digital Control Module):负责接收外部输入的频率、相位和幅值等参数,并将其转换为对DDS核心模块的控制信号; 2. DDS核心模块(DDS Core Module):根据接收到的控制信号,通过数学运算生成正弦波形的离散采样值; 3. 数字模拟转换模块(Digital-to-Analog Converter, DAC):将DDS核心模块输出的数字采样值转换为模拟电压信号; 4. 输出放大器(Amplifier):用于放大DAC输出的电压信号,并通过外部接口提供可调节幅值的正弦波输出。

DDS核心模块设计DDS核心模块是整个系统中最关键的部分,它负责根据输入参数生成正弦波的离散采样值。

下面是DDS核心模块设计中需要考虑的几个关键要素:相位累加器相位累加器是DDS核心模块中最基础且重要的组件之一。

它根据输入的频率和时钟信号,在每个时钟周期内累加相位增量,从而实现相位连续变化。

相位累加器可以使用一个定点数或浮点数寄存器来表示,并通过固定步长进行相位递增。

EDA正弦波信号发生器的设计

利用LPM 设计正弦信号发生器一、设计目的:进一步熟悉maxplu sII 及其LPM 设计的运用。

二、设计要求:1、利用原理图输入方式。

2、信号数据点值自行想法实现。

3、得出正确时序仿真文件。

三、设计原理:图1 正弦信号发生器结构框图图1所示的正弦波信号发生器的结构由三部分组成计数器或地址发生器(这里选择8位),正弦信号数据ROM (8位地址线,8位数据线),含有256个8位数据(一个周期)。

四、VHDL 顶层设计。

设计步骤:1、建立.mif 格式文件建立C 语言文件sin.cpp ,运行产生sin.exe 文件。

sin.cpp 程序代码:#include <iostream>#include <cmath>#include <iomanip>using namespace std;int main(){int i;float s;VHDL 顶层设计sin.vhd8位计数器 (地址发生器) 正弦波数据 存储ROM 产生波形数据cout<<"WIDTH=8;\nDEPTH=256;\n\nADDRESS_RADIX=HEX;\nDA TA_R ADIX=HEX;\n\nCONTENT\nBEGIN\n";for(i=0;i<256;i++){s=sin(atan(1)*8*i/256);cout<<" "<<i<<" : "<<setbase(16)<<(int)((s+1)*255/2)<<";"<<endl;}cout<<"END"<<endl;return 0;}把上述程序编译后,在DOS命令行下执行命令:sin.exe > sin.mif;将生成的sin.mif 文件。

vhdl语言正弦波信号发生器设计

AS正弦波信号发生器设计一、实验内容1.设计一正弦信号发生器,采用ROM进行一个周期数据存储,并通过地址发生器产生正弦信号。

(ROM:6位地址8位数据;要求使用两种方法:VHDL编程和LPM)2.正弦信号六位地址数据128,140,153,165,177,188,199,209,219,227,235,241,246,250,253,255,255,254,252,248,244,238,231,223,214,204,194,183,171,159,147,134,121,109,96,84,72,61,51,41,32,24,17,11,7, 3,1,0,0,2,5,9,1420,28,36,46,56,67,78,90,102,115,127。

二、实验原理正弦波信号发生器是由地址发生器和正弦波数据存储器ROM两块构成,输入为时钟脉冲,输出为8位二进制。

1.地址发生器的原理地址发生器实质上就是计数器,ROM的地址是6位数据,相当于64位循环计数器。

2.只读存储器ROM的设计(1)、VHDL编程的实现①基本原理:为每一个存储单元编写一个地址,只有地址指定的存储单元才能与公共的I/O相连,然后进行存储数据的读写操作。

②逻辑功能:地址信号的选择下,从指定存储单元中读取相应数据。

(2)、基于LPM宏功能模块的存储器的设计①LPM:Library of Parameterized Modules,可参数化的宏功能模块库。

②Quartus II提供了丰富的LPM库,这些LPM函数均基于Altera器件的结构做了优化处理。

③在实际的工程中,设计者可以根据实际电路的设计需要,选择LPM库中适当的模块,并为其设置参数,以满足设计的要求,从而在设计中十分方便的调用优秀的电子工程技术人员的硬件设计成果。

三、设计方案1.基于VHDL编程的设计在地址信号的选择下,从指定存储单元中读取相应数据系统框图如下:2.基于LPM宏功能模块的设计LPM宏功能具有丰富的由优秀的电子工程技术人员设计的硬件源代码可供调用,我们只需要调用其设计的模块并为其设计必要的参数即可。

EDA实验-正弦波信号发生器设计

实验八正弦信号发生器的设计一、实验目的1、学习用VHDL设计波形发生器和扫频信号发生器。

2、掌握FPGA对D/A的接口和控制技术,学会LPM_ROM在波形发生器设计中的实用方法。

二、实验仪器PC机、EDA实验箱一台Quartus II 6.0软件三、实验原理如实验图所示,完整的波形发生器由4部分组成:• FPGA中的波形发生器控制电路,它通过外来控制信号和高速时钟信号,向波形数据ROM 发出地址信号,输出波形的频率由发出的地址信号的速度决定;当以固定频率扫描输出地址时,模拟输出波形是固定频率,而当以周期性时变方式扫描输出地址时,则模拟输出波形为扫频信号。

•波形数据ROM中存有发生器的波形数据,如正弦波或三角波数据。

当接受来自FPGA的地址信号后,将从数据线输出相应的波形数据,地址变化得越快,则输出数据的速度越快,从而使D/A输出的模拟信号的变化速度越快。

波形数据ROM可以由多种方式实现,如在FPGA外面外接普通ROM;由逻辑方式在FPGA中实现(如例6);或由FPGA中的EAB模块担当,如利用LPM_ROM实现。

相比之下,第1种方式的容量最大,但速度最慢;,第2种方式容量最小,但速度最最快;第3种方式则兼顾了两方面的因素;• D/A转换器负责将ROM输出的数据转换成模拟信号,经滤波电路后输出。

输出波形的频率上限与D/A器件的转换速度有重要关系,本例采用DAC0832器件。

DAC0832是8位D/A转换器,转换周期为1µs,其引脚信号以及与FPGA目标器件典型的接口方式如附图2—7所示。

其参考电压与+5V工作电压相接(实用电路应接精密基准电压).DAC0832的引脚功能简述如下:•ILE(PIN 19):数据锁存允许信号,高电平有效,系统板上已直接连在+5V上。

•WR1、WR2(PIN 2、18):写信号1、2,低电平有效。

•XFER(PIN 17):数据传送控制信号,低电平有效。

•VREF(PIN 8):基准电压,可正可负,-10V~+10V.•RFB(PIN 9):反馈电阻端。

实验九定制LPM_ROM设计简单的正弦信号发生器

定制LPM_ROM设计简单的正弦信号发生器

实验名称:利用定制好的LPM_ROM设计简单的正弦信号发生器。

实验过程:

1:LPM_ROM的定制

图1 调用LPM_ROM

图2 LPM_ROM的参数设置

图3 加入初始化文件配置

2:LPM_ROM的仿真测试

图4 LPM_ROM仿真测试

3:波形分析

由图4可以看出,随着CLK的上升沿的出现,对应地址A的数据输出与初始化文件的数据完全吻合,实验得证。

再利用次模块完成一个简单的正弦信号发生器设计,该模块可以用来作为地址信号发生器(7位输出)和数据存储器(7位地址线,8位数据线),含有128个8位波形数据(一个正弦波形周期)。

4:正弦信号发生器的VHDL顶层设计

包括了对定制LPM_ROM时文件模块ROM78的例化调用。

图5 正弦信号发生器的VHDL描述

图6正弦信号发生器的仿真波形输出

5:波形分析

随着每个时钟上升沿的到来,输出端口将正弦波数据依次输出。

输出的数据与初始化配置文件相符。

6:观察RTL图

图7 正弦信号发生器的RTL电路图

分析:其中左边三个元件:加法器,寄存器构成7位计数器:其输出接右边ROM的地址输入端。

输出可接FPGA外的DAC,完成正弦波形输出。

实验结论:作为数据和程序的存储单位,ROM还有很多其他用处,如数字信号发生器的波形数据存储器,正弦信号发生器等。

简易正弦信号发生器设计

简易正弦信号发生器设计

一、实验目的

1.进一步熟悉QuartusII及LPM-RAM宏模块与FPGA硬件资源的使用方法。

二、实验设备

计算机、和软件QuartusII和EDA/SOPC试验箱

三、试验内容

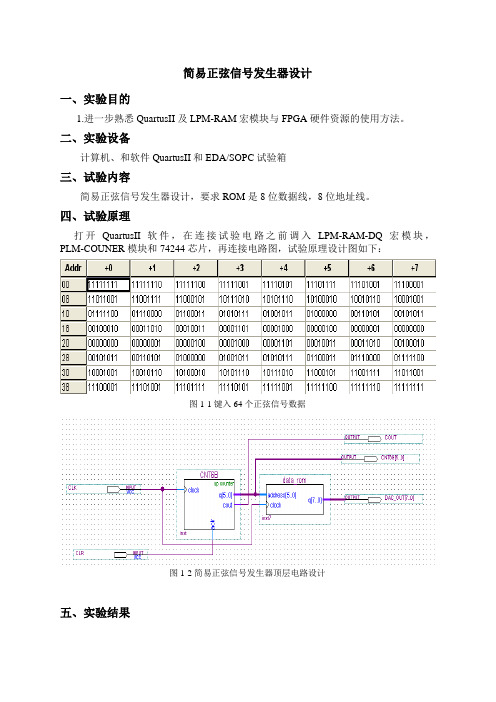

简易正弦信号发生器设计,要求ROM是8位数据线,8位地址线。

四、试验原理

打开QuartusII软件,在连接试验电路之前调入LPM-RAM-DQ宏模块,PLM-COUNER模块和74244芯片,再连接电路图,试验原理设计图如下:

图1-1键入64个正弦信号数据

图1-2简易正弦信号发生器顶层电路设计

五、实验结果

试验结果如下图:

图1-3综合后的RLT图

图1-4仿真波形图3.引脚锁定方案图

图1-5引脚锁定方案图

图1-6编程下载模式图

六、试验小节

一学期匆匆而过,通过大半学期的学习,我们学到了很多处理问题的技巧。

不过我们还要熟记很多单词,大多数的单词我们还不认识,相信通过进一步的学习,我们一定能学好这个软件。

我们也将以浓厚的兴趣和积极的态度去学习。

相信我们一定会有更加长足的进步。

DDS正弦信号发生器的设计

高级数字系统设计实验——DDS正弦信号发生器设计姓名学号专业:通信与信息系统指导老师实验三 DDS 正弦信号发生器一、实验要求:利用LPM_ROM 设计一个DDS 正弦信号发生器,要求ROM 表长度为8位,频率控制字为8位,输出频率分辨率优于1Hz 。

二、设计方案 1、 方案流程图:由频率控制字提供,累加器在系统时钟控制下,来一个上升沿就累加一次频率控制字的值,累加器的位数高于8位,所以用其高8位作为正弦查表的地址,根据地址就能寻址到表内的值,该值通过DAC 转换再通过示波器就能显示波形。

累加器溢出一次就相当于正弦表寻址一圈,正弦信号经历一个周期。

2、参数设定系统时钟fclk :设定为50KHz ,频率控制字M :8位,取值范围:1~28-1, 分辨率:f=nfclk2 n 为累加器的位数,当系统时钟的频率越低,相位累加器的位数越高,所得到的频率分辨率就越高,累加器:为了使输出频率的分辨率能达到1Hz ,选定为16位, 输出频率:fout=n M fclk 2*=16250000M *=6553650000M*, 当M=1时,输出频率最小,fout=0.7629Hz ,当M=255时,输出频率最大,fout=0.7629*255=194.5496Hz 。

3、模块建立 1)累加器LIBRARY IEEE;USE IEEE.std_logic_1164.all;USE IEEE.std_logic_ARITH.ALL;USE IEEE.std_logic_unsigned.ALL;ENTITY add ISPORT(fclk : IN STD_LOGIC; --接入系统时钟rst : IN STD_LOGIC; --复位端fcontrol:IN STD_LOGIC_VECTOR(7 DOWNTO 0);--频率控制字8位asum:OUT STD_LOGIC_VECTOR(15 DOWNTO 0));--输出累加和END ENTITY;ARCHITECTURE behav OF add ISSIGNAL a:STD_LOGIC_VECTOR(15 DOWNTO 0);--累加器的暂存值SIGNAL fc:STD_LOGIC_VECTOR(7 DOWNTO 0);--频率控制字的寄存器BEGINfc<=fcontrol;PROCESS(fc,a,fclk,rst)BEGINIF(rst = '1' ) THENa <=(others=>'0');--复位端高电平有效ELSIF( fclk'event AND fclk = '1') THENa<=a+fc; --系统时钟来一个上升沿就累加一次频率控制字的值ELSENULL;END IF;asum<=a;--寄存器的值赋值给输出端END PROCESS;END behav;2)ROM表ROM表可以通过LPM宏功能模块来实现,通过MegaWizard管理器可以构建我们所需的存储单元,因为频率控制字为8位,DAC 采用实验箱上的THS5651为10位并行高速DAC,所以需要256个存储单元,每个单元为10bits。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

★项目2:数字信号源项目简述:设计制作一个正弦信号发生器。

(1)正弦波输出频率范围:1kHz~10MHz;(2)具有频率设置功能,频率步进:100Hz;(3)输出信号频率稳定度:优于10-2;(4)输出电压幅度:1V到5V这间;(5)失真度:用示波器观察时无明显失真。

(6)输出电压幅度:在频率范围内50负载电阻上正弦信号输出电压的峰-峰值V opp=6V±1V;(7)产生模拟幅度调制(AM)信号:在1MHz~10MHz范围内调制度m a可在30%~100%之间程控调节,步进量50%,正弦调制信号频率为1kHz,调制信号自行产生;(8)产生模拟频率调制(FM)信号:在100kHz~10MHz频率范围内产生20kHz最大频偏,正弦调制信号频率为1kHz,调制信号自行产生;(9)产生二进制PSK、ASK信号:在100kHz固定频率载波进行二进制键控,二进制基带序列码速率固定为10kbps,二进制基带序列信号自行产生;开发时间:2007 开发人数:1运行环境:windows xp、Quartus II相关内容:(还未整体综合)下面是调幅原理图:下面是调频原理图:Location P IN_28Option Value VCCclkINPUT Location P IN_2Location P IN_4Location P IN_6Location P IN_8Location P IN_12Location P IN_14Location P IN_16LocationP IN_18Option Value VCCp0[7..0]INPUT LocationP IN_44Option...V alue...VCC CSKF[2..0]INPUT Location P IN_20Location P IN_23LocationP IN_42Option Value VCCCSKC[2..0]INPUT Location P IN_180Option Value daclkOUTPUTLocation P IN_175Location P IN_176Location P IN_173Location P IN_174Location P IN_169Location P IN_170Location P IN_167Location P IN_168Location P IN_165LocationP IN_166Option Value qout[9..0]OUTPUT NOT inst23GNDaddress[11..0]clockq[9..0]sin_rom0inst2data[7..0]cskc[2..0]cskf[2..0]oenkc[23..0]kf[23..0]xsj1instABA+Bdataa[23..0]datab[23..0]result[23..0]lpm_add_sub0inst15ABA+Bdataa[23..0]datab[23..0]result[23..0]lpm_add_sub0inst16DFFdata[23..0]clockq[23..0]lpm_dff0inst10ABA+Bdataa[23..0]datab[23..0]result[23..0]lpm_add_sub0inst17GNDDFFdata[23..0]clockq[23..0]lpm_dff0inst9address[11..0]clockq[9..0]sin_rom0inst3GNDQQ[23..0]qa[23..0]QQ[23..12]qd[23..0]qb[23..0]qa[14..5]q a [23..15]q a [4..0]qu[23..12]qd[23..0]qb[23..0]qu[23..0]下面是正弦信号发生器设计原理图:L o c a t i o n P I N _28O p t i o n V a l u e V C Cc l kI N P U T L o c a t i o n P I N _2L o c a t i o n P I N _4L o c a t i o n P I N _6L o c a t i o n P I N _12L o c a t i o n P I N _14L o c a t i o n P I N _16L o c a t i o n P I N _18L o c a t i o nP I N _8O p t i o n V a l u e V C Cp 0[7..0]I N P U T C CP U T V C CI N P U T V C CI N P U T L o c a t i o n P I N _180O p t i o n V a l u e d a c l kO U T P U T L o c a t i o n P I N _166L o c a t i o n P I N _165L o c a t i o n P I N _168L o c a t i o n P I N _167L o c a t i o n P I N _170L o c a t i o n P I N _169L o c a t i o n P I N _174L o c a t i o n P I N _173L o c a t i o n P I N _176L o c a t i o nP I N _175O p t i o n V a l u e q o u t [9..0]O U T P U TG N DN O Ti n s t 24a d d r e s s [11..0]c l o c k q [9..0]s i n _r o m 0i n s t 2O C T A L L A T C H E SD [8..1]GO E N Q [8..1]74373bn s t 6G N DA BA +B d a t a a [47..0]d a t a b [47..0]re s u l t [47..0]l p m _a d d _s u b 1i n s t 3D F Fd a t a [47..0]c l o c k q [47..0]l p m _d f f 0i n s t 8d a t a [7..0]c s k c [5..0]oe nk c [47..0]x s j 1i n s t3:8 D E C O D E RA B G 1C G 2A N G 2B N Y 0N Y 1N Y 2N Y 3N Y 4N Y 5N Y 6N Y 7N 74138n s t 5O C T A L L A T C H E SD [8..1]GO E N Q [8..1]74373bi n s t 10U n s i g n e d m u l t i p l i c a t i o nd a t a a [9..0]d a t a b [15..0]r e s u l t [25..0]l p m _m u l t 0i n s t 16N O Ti n s t 17N O T i n s t 18N O T i n s t 19N O T i n s t 20N O T i n s t 22N O T i n s t 23N O T i n s t 25N O T i n s t 26c s [5..0]q q [47..0]q a [7..0]c s 7q a [15..8]c s 6c s 0c s 1c s 2c s 3c s 6c s 7c s 5c s 4q q [31..20]q a [15..0]q o u t [9..0]q o u [9..0]路漫漫其修远兮,吾将上下而求索 - 百度文库下面是PSK 设计原理图:Location P IN_28Option Value VCCclkINPUT Location P IN_2Location P IN_4Location P IN_6Location P IN_12Location P IN_14Location P IN_16Location P IN_18LocationP IN_8Option Value VCCp0[7..0]INPUT Location P IN_23Option Value VCCdz0INPUT Location P IN_42Option Value VCC dz1INPUT Location P IN_44Option Value VCCdz2INPUT VCCdz3_pskINPUT Location P IN_180Option Value daclkOUTPUTLocation P IN_166Location P IN_165Location P IN_168Location P IN_167Location P IN_170Location P IN_169Location P IN_174Location P IN_173Location P IN_176Location P IN_175Option Value qout[9..0]OUTPUT NOTinst24address[11..0]clockq[9..0]sin_rom0inst2OCTAL LATCHE S D[8..1]GOE N Q[8..1]74373binst6GNDABA+Bdataa[47..0]datab[47..0]result[47..0]lpm_add_sub1inst3DFFdata[47..0]clockq[47..0]lpm_dff0inst8data[7..0]cskc[5..0]oenkc[47..0]xsj1inst3:8 DE CODE RA B G1C G2AN G2BN Y0NY1N Y2N Y3N Y4N Y5N Y6NY7N74138inst5GNDVCCOCTAL LATCHE SD[8..1]GOE N Q[8..1]74373binst10Unsigned multiplicationdataa[9..0]datab[15..0]result[25..0]lpm_mult0inst16NOTinst17NOTinst18NOTinst19NOT inst20NOTinst22NOTinst23NOTinst25NOTinst26VCCddio bidirpower up highdatain_h[11..0]datain_l[11..0]outclockpadio[11..0]altddio_bidir0inst4A BA-B dataa[11..0]datab[11..0]result[11..0]lpm_add_sub2inst1cs[5..0]qq[31..20]qa[15..0]qou[9..0]p s kqa[7..0]cs7qa[15..8]cs6cs5cs6cs1cs0cs2cs3cs4cs7pskqou[9..0]qq[47..0]GND。