时钟参数shew和jitter介绍

时间抖动(jitter)的概念及其分析方法

时间抖动(jitter)的概念及其分析方法随着通信系统中的时钟速率迈入GH z级,抖动这个在模拟设计中十分关键的因素,也开始在数字设计领域中日益得到人们的重视。

在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。

不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

有资料表明在3GH z以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。

在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。

本文向数字设计师们介绍了抖动的基本概念,分析了它对系统性能的影响,并给出了能够将相位抖动降至最低的常用电路技术。

本文介绍了时间抖动(jitter)的概念及其分析方法。

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通信质量的关键因素。

关键字:时间抖动、jitter、相位噪声、测量时间抖动的概念在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns 有一个跳变沿。

但不幸的是,这种信号并不存在。

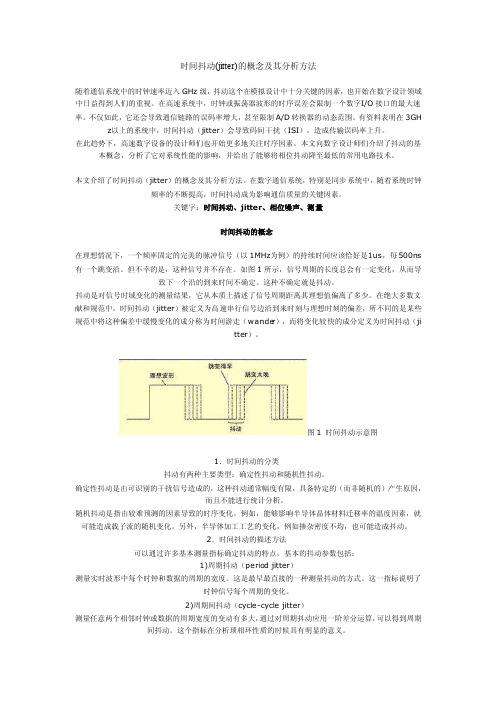

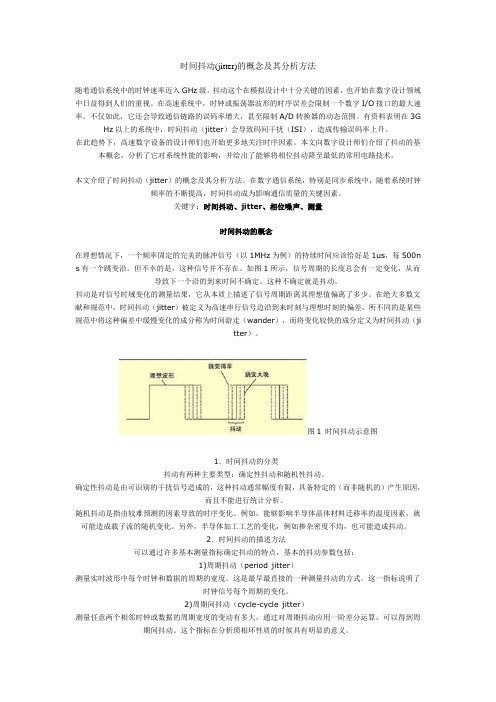

如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。

这种不确定就是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。

在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter)。

图1 时间抖动示意图1.时间抖动的分类抖动有两种主要类型:确定性抖动和随机性抖动。

jitter指标

jitter指标摘要:一、什么是Jitter指标二、Jitter指标的重要性三、Jitter指标的测量方法四、降低Jitter指标的策略五、Jitter指标在实际应用中的作用正文:Jitter指标是衡量数据传输过程中时延变化的一个参数,它反映了网络传输的稳定性和质量。

在计算机网络、通信领域以及实时应用系统中,Jitter指标具有重要的意义。

本文将详细介绍Jitter指标的概念、重要性、测量方法以及降低Jitter的策略。

一、什么是Jitter指标Jitter(抖动)是指数据包在传输过程中到达时间的不稳定性。

当数据包的传输时延发生变化时,会引起Jitter。

Jitter指标通常用数据包的传输延迟波动程度来表示,单位为毫秒(ms)。

二、Jitter指标的重要性1.实时性应用:在实时性要求较高的应用场景中,如语音通信、视频流传输等,Jitter会影响数据的正确传输和接收,进而导致通话中断、视频卡顿等问题。

2.网络性能:Jitter指标直接影响着网络的性能和稳定性。

高Jitter会导致网络吞吐量下降、服务质量降低,甚至可能引发网络拥塞。

3.系统可靠性:Jitter指标对系统的可靠性也有很大影响。

长时间处于高Jitter状态的网络,容易出现数据包丢失、传输失败等问题,从而导致系统不可靠。

三、Jitter指标的测量方法1.基于历史数据:通过收集和分析历史数据,计算数据包到达时间的波动程度。

2.实时监测:利用网络监测工具,实时收集数据包的传输延迟,并计算Jitter指标。

3.仿真实验:通过构建网络仿真环境,模拟实际数据传输过程,评估Jitter 指标。

四、降低Jitter指标的策略1.优化网络拓扑:合理规划网络结构,减少数据包传输过程中的路由跳数,降低时延。

2.提高带宽:增加网络带宽,提高数据传输速度,降低Jitter。

3.优化传输协议:改进传输协议的设计,提高传输效率,减少数据包在网络中的等待时间。

4.引入缓存机制:在数据传输过程中,引入缓存机制,对数据包进行缓存和调度,降低Jitter。

时钟电路设计过程中常见问题分析

时钟电路设计过程中常见问题分析在电路中,时钟的不良设计可能导致整个设计的失败。

尽管最简单的时钟分布是最好的,但是在很多应用中,电路板上某些位置的芯片需要同步时钟信号,而在另外一些位置又需要非同步(即不同频率)时钟信号,时钟的分布形成了一个多分支时钟树,给设计带来了巨大的挑战。

满足设计规范中抖动(jitter)的要求是时钟设计中最关键的。

抖动是时钟周期实际值与理想值之间的差异,并且通常随着时钟树而变得更复杂,操作频率越高,jitter越大。

更糟糕的是,它的容差通常非常小,在超高速应用中甚至只允许有几个飞秒(10-15s)的容差。

偏斜(Skew)是指同步时钟信号从一个芯片到另一个芯片之间的时间差异,在采用网络级同步通信的应用中,它是一个很大的问题。

相对而言,Jitter是一个普遍存在的问题,因为它直接影响自由振荡电路和同步电路,本文将重点讨论如何降低他对电路时钟的影响。

设计约束要求工程师不仅选择高精度时钟芯片、设计优秀的电路布局,还要确保时钟信号在传输到目标IC的过程中不受电磁干扰(EMI)或其他信号线的串扰。

但是在很多时候,即使选择了高精度的芯片和优秀的时钟树设计,也不能保证抖动是最小的。

制造工艺、供应电压、温度和频率的变化都会影响到时钟特性。

测试和故障排除是必要的,而在测试和排除故障的过程中,通常又会导致器件的更改,甚至是添加诸如抖动衰减器等来清理时钟信号,以满足产品规范。

(注:在描述时钟树精度时,工程师有时会提到相位噪声。

抖动是时钟在时域上不确定性的度量;而相位噪声是抖动在频域的表现,尽管本文仅限于时域技术,但所提到的解决方案,也适用于频域。

)时钟树芯片不同产品对时钟的要求像人类的指纹一样各不相同,所以没有典型的时钟树结构。

图1给出了一个时钟树的例子,图中的芯片来源于Silicon Labs。

图1:专用芯片可以从单晶体和时钟发生器中生成多个时钟,结果就是一个时钟树。

(来源:Silicon Labs)虽然时钟电路具有多样性,但通常每个电路具有以下一个或多个器件:。

时间抖动(jitter)的概念及其分析方法

时间抖动(jitter)的概念及其分析方法随着通信系统中的时钟速率迈入GHz级,抖动这个在模拟设计中十分关键的因素,也开始在数字设计领域中日益得到人们的重视。

在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。

不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

有资料表明在3G Hz以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。

在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。

本文向数字设计师们介绍了抖动的基本概念,分析了它对系统性能的影响,并给出了能够将相位抖动降至最低的常用电路技术。

本文介绍了时间抖动(jitter)的概念及其分析方法。

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通信质量的关键因素。

关键字:时间抖动、jitter、相位噪声、测量时间抖动的概念在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500n s有一个跳变沿。

但不幸的是,这种信号并不存在。

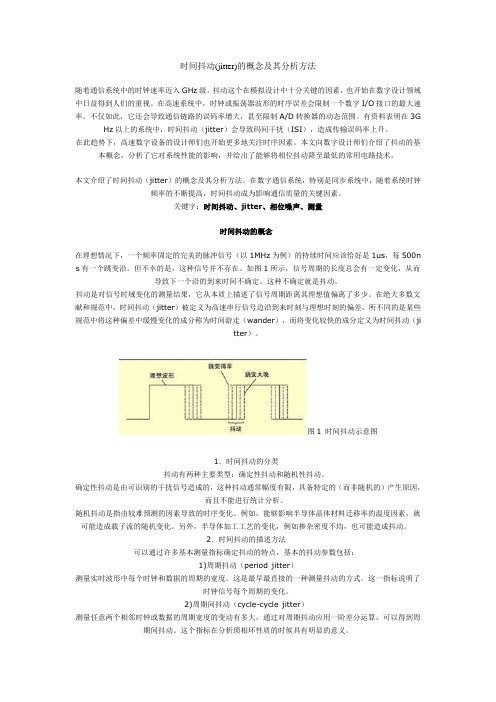

如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。

这种不确定就是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。

在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter)。

图1 时间抖动示意图1.时间抖动的分类抖动有两种主要类型:确定性抖动和随机性抖动。

确定性抖动是由可识别的干扰信号造成的,这种抖动通常幅度有限,具备特定的(而非随机的)产生原因,而且不能进行统计分析。

随机抖动是指由较难预测的因素导致的时序变化。

例如,能够影响半导体晶体材料迁移率的温度因素,就可能造成载子流的随机变化。

简述时钟skew和jitter的理解

简述时钟skew和jitter的理解时钟skew和jitter是两个不同的概念,具体解释如下:1. skew:是指同样的时钟产生的多个子时钟信号之间的延时差异。

这种延时差异可能是由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,导致时钟边沿的位置有所差异。

在布局布线完成后,物理路径延时是固定的,所以在设计中考虑到时钟偏斜,就可以避免偏斜带来的影响。

2. jitter:由于晶振本身稳定性、电源以及温度变化等原因造成了时钟频率的变化,指的是时钟周期的变化。

它指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。

时钟抖动可能会导致时钟信号的误差,从而影响到时钟同步的精度。

在数字系统中,时钟信号起着非常重要的作用。

它同步了各个模块的操作,确保了数据的正确传输。

然而,时钟信号在传输过程中会受到各种因素的影响,导致其信号的稳定性和正确性降低。

其中,时钟偏斜(skew)和时钟抖动(jitter)是两个重要的概念。

时钟偏斜是指同一时钟源产生的多个子时钟信号之间的延时差异。

这种延时差异可能源于时钟源到达不同寄存器所经历路径的驱动和负载的不同,导致时钟边沿的位置有所差异。

在布局布线完成后,物理路径延时是固定的,所以在设计中考虑到时钟偏斜,就可以避免偏斜带来的影响。

而时钟抖动是由于晶振本身稳定性、电源以及温度变化等原因造成了时钟频率的变化,指的是时钟周期的变化。

它指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。

时钟抖动可能会导致时钟信号的误差,从而影响到时钟同步的精度。

在数字系统中,为了确保时钟信号的正确性和稳定性,我们需要考虑如何减小时钟偏斜和时钟抖动的影响。

首先,在布局布线时,我们需要考虑到时钟信号的传输路径,尽量让所有路径的延时一致。

其次,我们需要注意晶振的选择和电源的管理,尽量减少外部因素对时钟信号的影响。

时间抖动(jitter)的概念及其分析方法

时间抖动(jitter)的概念及其分析方法随着通信系统中的时钟速率迈入GHz级,抖动这个在模拟设计中十分关键的因素,也开始在数字设计领域中日益得到人们的重视。

在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。

不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

有资料表明在3G Hz以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。

在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。

本文向数字设计师们介绍了抖动的基本概念,分析了它对系统性能的影响,并给出了能够将相位抖动降至最低的常用电路技术。

本文介绍了时间抖动(jitter)的概念及其分析方法。

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通信质量的关键因素。

关键字:时间抖动、jitter、相位噪声、测量时间抖动的概念在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500n s有一个跳变沿。

但不幸的是,这种信号并不存在。

如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。

这种不确定就是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。

在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter)。

图1 时间抖动示意图1.时间抖动的分类抖动有两种主要类型:确定性抖动和随机性抖动。

确定性抖动是由可识别的干扰信号造成的,这种抖动通常幅度有限,具备特定的(而非随机的)产生原因,而且不能进行统计分析。

随机抖动是指由较难预测的因素导致的时序变化。

例如,能够影响半导体晶体材料迁移率的温度因素,就可能造成载子流的随机变化。

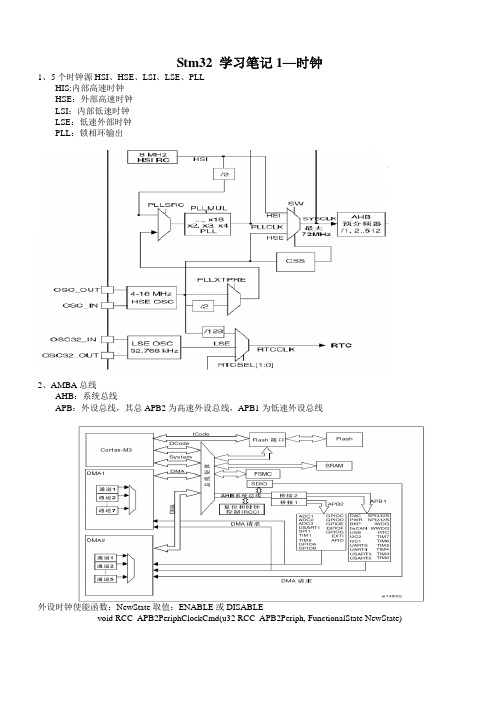

Stm32 学习笔记1--时钟

Stm32 学习笔记1—时钟1、5个时钟源HSI、HSE、LSI、LSE、PLLHIS:内部高速时钟HSE:外部高速时钟LSI:内部低速时钟LSE:低速外部时钟PLL:锁相环输出2、AMBA总线AHB:系统总线APB:外设总线,其总APB2为高速外设总线,APB1为低速外设总线外设时钟使能函数:NewState取值:ENABLE或DISABLEvoid RCC_APB2PeriphClockCmd(u32 RCC_APB2Periph, FunctionalState NewState)void RCC_APB1PeriphClockCmd(u32 RCC_APB1Periph, FunctionalState NewState)系统时钟使能函数:NewState取值:ENABLE或DISABLE需要使用某一或多个外设时需打开相对应的时钟,多个时钟用“|”分隔3、RCC相关寄存器3.1寄存器名称和功能描述①一个32位的时钟控制寄存器(RCC_CR)②一个32位的时钟配置寄存器(RCC_CFGR)③一个32位的时钟中断寄存器(RCC_CIR)④一个32位的APB2外设复位寄存器(RCC_APB2RSTR)⑤一个32位的APB1外设复位寄存器(RCC_APB1RSTR)⑥一个32位的AHB外设时钟使能寄存器(RCC_AHBENR)⑦一个32位的APB2外设时钟使能寄存器(RCC_APB2ENR)⑧一个32位的APB1外设时钟使能寄存器(RCC_APB1ENR)⑨一个32位的备份域控制寄存器(RCC_BDCR)⑩一个32位的控制/状态寄存器(RCC_CSR)3.2结构定义和访问方法typedef struct{vu32 CR;vu32 CFGR;vu32 CIR;vu32 APB2RSTR;vu32 APB1RSTR;vu32 AHBENR;vu32 APB2ENR;vu32 APB1ENR;vu32 BDCR;vu32 CSR;} RCC_TypeDef;#define RCC_BASE (AHBPERIPH_BASE + 0x1000)#ifdef _RCC#define RCC ((RCC_TypeDef *) RCC_BASE)#endif /*_RCC */其中AHBPERIPH_BASE=(u32)0x40020000,那么RCC指向0x400210003.3RCC配置方法:void RCC_Configuration(void){RCC_DeInit();/*RCC复位*/RCC_HSEConfig(RCC_HSE_ON);/*打开外部高速时钟晶振HSE ,Enable HSE */ HSEStartUpStatus = RCC_WaitForHSEStartUp();/*等待直到晶振准备好*/if(HSEStartUpStatus == SUCCESS)/*晶振准备好*/{FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);/*使能FLASH半周期访问*/FLASH_SetLatency(FLASH_Latency_2);/*设置代码延时值*//*********************************************************************************************************************************************/ RCC_HCLKConfig(RCC_SYSCLK_Div1);/*置AHB时钟(HCLK), AHB时钟= 系统时钟/1*/RCC_PCLK2Config(RCC_HCLK_Div1); /*高速时钟APB2时钟= HCLK */RCC_PCLK1Config(RCC_HCLK_Div2);/*低速时钟APB1时钟= HCLK / 2 */RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);/*设置PLL时钟源及倍频系数,外部时钟8M,倍频数9*//*****************************************************************************原型:void RCC_PLLConfig(u32 RCC_PLLSource, u32 RCC_PLLMul)*********************************************************************************/RCC_PLLCmd(ENABLE);/*PLL使能*//*等待锁相环输出稳定*/while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){}/* 选择系统时钟源*/RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);/****************************************************************************************************************************************************/ /* 返回当前系统时钟源0x00:HSI,0x04:HSE,0x08:PLL */while(RCC_GetSYSCLKSource() != 0x08){}}/* 以后内容设置外部设备时钟使能*/……….}。

jitter指标

jitter指标摘要:1.什么是jitter指标2.jitter指标的作用3.jitter指标的计算方法4.如何利用jitter指标优化网络性能5.jitter指标在实际应用中的案例正文:Jitter指标是一种衡量网络传输延迟和抖动的指标,用于评估网络传输的稳定性。

在现代通信网络中,jitter指标对于保证服务质量(QoS)具有重要意义。

本篇文章将详细介绍jitter指标的定义、作用、计算方法以及在优化网络性能中的应用。

首先,我们需要了解什么是jitter指标。

简单来说,jitter指标反映了数据包在网络中传输的延迟和抖动情况。

延迟是指数据包从发送端到接收端所需的时间,而抖动是指数据包到达时间的不稳定性。

jitter指标的单位通常是毫秒(ms)。

jitter指标的作用主要体现在以下几个方面:1.影响音视频通话质量:在音视频通话中,jitter会导致声音和画面间的同步问题,从而影响通话质量。

2.降低数据传输效率:由于jitter的存在,接收端可能需要额外的处理来补偿延迟和抖动,从而降低数据传输的效率。

3.影响实时应用性能:对于实时应用,如在线游戏、自动驾驶等,jitter可能导致数据包丢失,从而影响应用性能和安全性。

接下来,我们来探讨jitter指标的计算方法。

通常情况下,jitter指标可以通过以下公式进行计算:Jitter = √(Σ(ΔTi))其中,ΔTi表示每个数据包的到达时间与期望到达时间之间的差值,i表示数据包序号。

计算出的jitter指标越高,说明网络传输的延迟和抖动越严重。

那么,如何利用jitter指标优化网络性能呢?以下是一些建议:1.选择合适的传输协议:针对不同的应用场景,选择具有抗jitter能力的传输协议,如QUIC、SRTP等。

2.优化网络拓扑结构:通过调整网络拓扑结构,降低传输路径中的延迟和抖动。

3.采用前向纠错技术:通过前向纠错技术,接收端可以检测并纠正数据包中的错误,从而提高传输质量。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

AB37

09/19/00

Application Brief 37 Clock basics 12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

Application Brief 37

Clock Basics

by Rakesh Bhatia Purpose The purpose of this document is to provide the reader with information on clocks, their related terminology and criteria that need to be considered prior to making a selection of the device. It is meant for the beginner as well as for enhanced users. Besides the definitions, the document highlights clock based devices available from Pericom, parameters that are taken into consideration by users of these devices, and useful references. SiliconClock SiliconClock is a broad-based term used for the family of clocks and clock based devices offered by Pericom Semiconductor Corporation. Some of the IC devices in this family are high-performance 3.3V and 5V clock distribution circuits, PLL-based zero-delay clock buffers, and clock generators that are used in PC, printer, networking, datacom and telecom applications. SuperClock As more and more applications require high frequency signals to be distributed more precisely, the skew parameter of an input clock could cause problems. The delay caused due to the skew can erode the timing margin in a typical system. Pericom provides a solution to this problem by offering the SuperClock. One of the key features of the SuperClock is that it provides adjustable skew and is intended for high-performance computing or networking applications. For a complete description of different SuperClock products, please visit . Clock Drivers For most applications that use clocks or clock generators, a clock buffer or driver is also required. Typically, the function of this driver is to drive one input to several outputs. In the past, a time delay (propagation delay) has usually been associated with such devices. Pericom provides several families of clock drivers, of which some have relatively no time delay (hence referred to as zero-delay) between I/O. For example, the PI6C2308A clock buffer has a very low input to output propagation delay (<150ps) which helps in reducing the overall time taken for a clock signal to be delivered. Most of these devices are available for inputs of either 5V or 3.3V. Some of the other features of the clock buffers are low skew, multiple output banks, and low jitter. Specific information on clock drivers can be found by visiting .

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012 12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

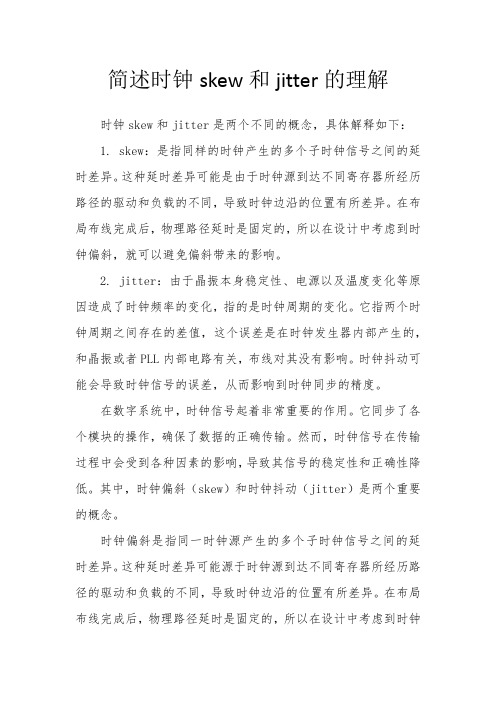

Jitter For most clock devices, jitter is a time based error and can be seen as the deviation of the output from its ideal phase or frequency. In a typical application this will be seen as phase noise and may even get amplified if multiple stages are involved in the design. In order to overcome this situation, PLL based clocks are used. Jitter is typically described as cycle-to-cycle (i.e. it is the difference in the clocks period between two consecutive cycles). Jitter is expressed in units of ±ps. This is because it can be either leading or lagging from the ideal output waveform.

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

Half-Period Jitter Half-Period Jitter is the measure of maximum change in a clocks output transition from its ideal position during onehalf period. This type of jitter is considered in double data rate (DDR) transfer applications. It is measured as: Tjit (hper) = Thalfperiod 1/2Fo, where Fo is the frequency of the input signal. Considering the above example of a 20 MHz clock and a 25.1ns half cycle, the half-period jitter will be measured as: Tjit(hper) = 25.1 25 = 0.1ns (or 100ps)

t1 t2 t3

Clock

Figure 1. Cycle-to-Cycle Jitter = T2-T1, T3-T2

Period Jitter Period Jitter can be defined as the measure of maximum change in a clocks output transition from its ideal position during a single period. This type of jitter is considered in high-speed designs. It is measured as: Tjit (per) = Tcycle 1/Fo, where Fo is the frequency of the input signal. Consider an input clock signal of 20 MHz being applied to a driver. If the output on the driver has a measured period (Tcycle) of 51ns on the oscilloscope then, Tjit = 51 1/20Mhz =1ns