Xilinx FPGA XC5VLX30T 特殊资源分布示意图

FPGA硬件实战设计经验

TR_Con_ZD板卡设计经验总结针对TR板卡的PCB布线一根线未动想到的TR板卡bank分配方法介绍与原来在华为工作的师兄(他做的TR板卡的PCB)聊了一下,他说TR板卡的FPGA线序一根都没改。

Bank分配是我来做的,原则是方便PCB走线。

分配时候是参考下面的资料来分配的。

TR板卡结构图XC6VSX315T-FF1759的bank管脚分布图考虑到板卡上IO资源大户是AD/DA,FPGA的bank分配集中在右侧,而AD/DA在板卡的上方,因此将FPGA逆时针转90°,如下图所示,这样PCB布线就比较方便了。

分配bank的时候没有考虑Bank在FPGA内部的分布图,如下图所示:想到的硬件设计流程的东西师兄说:“动一根线的话,都需要FPGA程序重新跑一遍,这需要浪费很多时间。

”FPGA 程序?TR板卡的程序还没有呢!的确值得思考了,到底这个设计应该是按照怎样的一个流程。

在华为,是按照这样的流程进行的。

1.硬件设计人员将IO需求,板卡供电等情况反馈给逻辑设计人员2.逻辑人员对所需的FPGA资源做评估,最终确定FPGA型号(硬件设计人员也可以参与一起选型)3.逻辑设计人员对FPGA进行bank分配,需要以下资源:a)硬件设计人员提供硬件设计框图b)最好对所用的IO先画一个自己根据原理图框图分配的bank的原理图草图,导入PCB后进行一下预布局,这样信号流程就清晰了。

逻辑人员根据上述资源进行bank的分配,因为他们对FPGA内部的资源最清楚。

逻辑人员要兼顾PCB布局布线的方便,有时候不可能照顾都到布局布线的方便。

这时候,就需要在硬件设计人员和FPGA设计人员之间来回折腾,最终兼顾双方,得到一个bank 分配方案。

4.FPGA人员根据bank分配,写一个测试评估的程序,如果能够跑通,时序满足设计需求,说明现在的bank分配可以使用,如果出现严重的时序错误,那么就需要考虑重新分配bank,通过不断地调整,最终确定板卡的bank分配。

FPGA可编程逻辑器件芯片XC5VLX330-2FFG1760I中文规格书

Table 1-2:DSP48E Port List and Definitions (Cont’d)Name Direction Bit Width DescriptionBCIN(1)In18Cascaded data input from BCOUT of previous DSP48E slice(muxed with B).PCIN(1)In48Cascaded data input from PCOUT of previous DSP48E slice toadder.CARRYCASCIN(1)In1Cascaded carry input from CARRYCASCOUT of previousDSP48E slice.MULTSIGNIN(1)In1Sign of the multiplied result from the previous DSP48E slice forMACC extension.ACOUT(1)Out30Cascaded data output to ACIN of next DSP48E slice.BCOUT(1)Out18Cascaded data output to BCIN of next DSP48E slice. CARRYCASCOUT(1)Out1Cascaded carry output to CARRYCASCIN of next DSP48E slice.This signal is internally fed back into the CARRYINSELmultiplexer input of the same DSP48E slice. MULTSIGNOUT(1)Out1Sign of the multiplied result cascaded to the next DSP48E slicefor MACC extension.P Out48Data output from second stage adder/subtracter or logicfunction.PATTERNBDETECT Out1Output indicating a match between P[47:0] and pattern bar. PATTERNDETECT Out1Output indicating a match between P[47:0] and pattern. OVERFLOW Out1Output indicating overflow when used with appropriatesetting of the pattern detector.UNDERFLOW Out1Output indicating underflow when used with appropriatesetting of the pattern detector.CARRYOUT Out44-bit CARRYOUT from each 12-bit section of logic unit/adder.Useful for SIMD.CARRYOUT[3] is the carryout of the 48-bit adder (invalidduring multiplies).PCOUT(1)Out48Cascaded data output to PCIN of next DSP48E slice.Notes:1.These signals are dedicated routing paths internal to the DSP48E column. They are not accessible via fabric routing resources.2.All signals are active High.Simplified DSP48E Slice OperationThe math portion of the DSP48E slice consists of a 25-bit by 18-bit, two's complementmultiplier followed by three 48-bit datapath multiplexers (with outputs X, Y, and Z). Thisis followed by a three-input adder/subtracter or two-input logic unit (see Figure1-5).When using two-input logic unit, the multiplier cannot be used.The data and control inputs to the DSP48E slice feed the arithmetic and logic stages. The Aand B data inputs can optionally be registered one or two times to assist the construction ofPipeline RegistersNotesAREG, BREG ACASCREG,BCASCREG(Refer to Figure1-7)Current DSP To Cascade DSP00Direct and cascade paths have no registers.11Direct and cascade paths have one register.21, 2When direct path has two registers, cascade path canhave one or two registers.X, Y, and Z MultiplexerThe OPMODE (Operating Mode) control input contains fields for X, Y, and Z multiplexerselects.The OPMODE input provides a way for the user to dynamically change DSP48Efunctionality from clock cycle to clock cycle (e.g., when altering the internal datapathconfiguration of the DSP48E slice relative to a given calculation sequence).The OPMODE bits can be optionally registered using the OPMODEREG attribute (asnoted in Table1-3).Table1-6, Table1-7, and Table1-8 list the possible values of OPMODE and the resultingfunction at the outputs of the three multiplexers (X, Y, and Z multiplexers). Themultiplexer outputs supply three operands to the following adder/subtracter. Not allpossible combinations for the multiplexer select bits are allowed. Some are marked in thetables as “illegal selection” and give undefined results. If the multiplier output is selected,then both the X and Y multiplexers are used to supply the multiplier partial products to theadder/subtracter.If AREG/BREG = 0 and USE_MULT = MULT_S (this requires MREG=1), the A:B pathshould not be selected via the opmode multiplexer. Since the opmode can be dynamic,switching between the registered multiplier with MREG=1 and the combinatorial A:B pathis not supported. If the multiplier is not being used, USE_MULT should be set to NONE. Table 1-6:OPMODE Control Bits Select X Multiplexer OutputsZ OPMODE [6:4]YOPMODE [3:2]XOPMODE [1:0]XMultiplexerOutputNotesxxx xx000Defaultxxx0101M Must select withOPMODE[3:2]=01 xxx xx10Pxxx xx11A:B 48 bits wide Table 1-7:OPMODE Control Bits Select Y Multiplexer OutputsZ OPMODE[6:4]YOPMODE[3:2]XOPMODE[1:0]YMultiplexerOutputNotesxxx00xx0Defaultxxx0101M Must select withOPMODE[1:0]=01xxx10xx48'ffffffffffff Used mainly for logicunit bitwise operations onX and Z multiplexersxxx11xx CChapter 1:DSP48E Description and SpecificsZ OPMODE[6:4]YOPMODE[3:2]XOPMODE[1:0]ZMultiplexerOutputNotes000xx xx0Default001xx xx PCIN010xx xx P011xx xx C1001000P Use for MACC extendonly101xx xx17-bitShift(PCIN)110xx xx17-bitShift(P)111xx xx xx Illegal selectionSimplified DSP48E Slice OperationAdder/Subtracter or Logic UnitThe adder/subtracter or logic unit output is a function of control and data inputs (see Figure1-15). The data inputs to the adder/subtracter are selected by the OPMODE and the CarryInSel signals. The ALUMODE signals choose the function implemented in theadder/subtracter. Thus, the OPMODE, ALUMODE, and CARRYINSEL signals together determine the functionality of the embedded adder/subtracter/logic unit. When using the logic unit, the multiplier must not be used. The values of OPMODEREG andCARRYINSELREG must be identical.As with the input multiplexers, the OPMODE bits specify a portion of this function. The symbol ± in the table means either add or subtract and is specified by the state of theALUMODE control signal (ALUMODE = 0011 is defined as “subtraction,” used forretargeting designs from Virtex-4 devices). The symbol “:” in the table meansconcatenation. The outputs of the X and Y multiplexer and CIN are always added together.Refer to “ALUMODE Inputs,” page 32.。

FPGA可编程逻辑器件芯片XC5VLX30-1FFG324I中文规格书

XTP481 (v3.3) November 18, 2019 FAQ: Implications of XCN18002 SummaryThe purpose of this notification is to communicate FAQs related to substrate material change for Virtex®, Virtex®-II, Virtex®-II Pro, Virtex®-4 and Virtex®-5 FPGA packages.The manufacturer of the current substrate material is discontinuing production of the substrate material. Therefore, Xilinx qualified new substrate material set to continue supply and shipment of Virtex, Virtex-II, Virtex II-Pro, Virtex-4 and Virtex-5 FPGA packages. This enables Xilinx to better support long-term customer demand. There is no change in the fit, form or function with this change. The new substrate core and build up material have been qualified and shipping in many 7 series, ROHS Lead Free and UltraScale™ packages.Xilinx will revise the corresponding material declaration data sheet (MDDS) to reflect the new material change . FAQsQ: What is the change?Substrate material will change.Q: Why is Xilinx making this change?The manufacturer of the current substrate material is discontinuing production of the substrate material. Therefore, Xilinx qualified new substrate material set to continue supply and shipment of Virtex, Virtex-II, Virtex II-Pro, Virtex-4 and Virtex-5 FPGA packages as mentioned in XCN18002. This enables Xilinx to better support long-term customer demand.Q: When will this change take effect?Xilinx will start shipping commercial / industrial “XC” devices 90 days after the PCN release. Estimated cut-over dates for Defense-grade “XQ” devices are listed below. No delay or exceptions will be allowed once the PCN is released.Q: Can customer continue with current core/build up material?No. Substrate material supplier is ending production of current material. There will be no material to continue with current BOM.Q:Is there any change in shelf life?No change.Q: Is there any change in package dimension?No change.FAQ: Substrate Material Change for Virtex, Virtex-II, Virtex-II Pro, Virtex-4 & Virtex-5 FBGA PackagesFAQ: Substrate Material Change for Virtex, Virtex-II, Virtex-II Pro, Virtex-4 & Virtex-5 FBGA Packages Table 1: Virtex-II Pro Devices-PackagesDevice Package-PinEstimatedcrossshippingDevice Package-PinEstimatedcrossshippingXC2VP2 FF(G)672 May 2020 XC2VP50 FF(G)1517 Jul 2018 XC2VP4 FF(G)672 May 2020 XC2VP70 FF(G)1517 Oct 2019 XC2VP7 FF(G)672 Jan 2019 XC2VP100 FF(G)1696 Jul 2018 XC2VP20 FF(G)896 May 2020 XC2VP100 FF(G)1704 Mar 2019 XC2VP30 FF(G)896 Jun 2019 XC2VP70 FF(G)1704 Jun 2019 XC2VP7 FF(G)896 Dec 2019Table 3: Virtex-5 Devices-PackagesDevice Package-PinEstimatedcrossshippingDevice Package-PinEstimatedcrossshippingXC5VTX150T FF(G)1156 Jul 2018 XC5VFX100T FF1738 May 2020 XC5VFX130T FF(G)1738 Jul 2019 XC5VLX110T FF1738 May 2020 XC5VFX200T FF(G)1738 Jan 2019 XC5VLX155T FF1738 Jun 2019 XC5VLX220T FF(G)1738 Nov 2018 XC5VLX110 FF1760 Nov 2019 XC5VLX330T FF(G)1738 Dec 2018 XC5VLX155 FF1760 Jul 2018 XC5VSX240T FF(G)1738 Jun 2019 XC5VLX20T FF323 Jul 2019 XC5VTX150T FF(G)1759 Feb 2019 XC5VLX30T FF323 Feb 2019 XC5VTX240T FF(G)1759 Feb 2019 XC5VLX30 FF324 Jan 2019 XC5VFX100T FF1136 May 2020 XC5VLX50 FF324 Mar 2019 XC5VFX70T FF1136 May 2020 XC5VFX30T FF665 Oct 2019 XC5VLX110T FF1136 Dec 2019 XC5VFX70T FF665 May 2020 XC5VLX155T FF1136 May 2020 XC5VLX30T FF665 Dec 2019 XC5VLX50T FF1136 May 2020 XC5VLX50T FF665 Dec 2019 XC5VLX85T FF1136 Sep 2019 XC5VSX35T FF665 May 2020 XC5VSX50T FF1136 May 2020 XC5VSX50T FF665 Jan 2019 XC5VSX95T FF1136 Apr 2019 XC5VLX110 FF676 Mar 2020 XC5VLX110 FF1153 Jan 2020 XC5VLX30 FF676 Jan 2019 XC5VLX155 FF1153 Feb 2019 XC5VLX50 FF676 Aug 2018 XC5VLX50 FF1153 Aug 2019 XC5VLX85 FF676 Nov 2018 XC5VLX85 FF1153 Feb 2019 XC5VLX220 FF(G)1760 Nov 2019XC5VLX330 FF(G)1760 Nov 2018 Table 4: Virtex-4 EasyPath Devices-PackagesDevice Package-PinEstimatedcrossshippingXCE04L6 FF1148 Nov 2018 XCE04S2 FFG668 Apr 2019 XCE04L10 FF(G)1513 May 2020 XCE04L4 FF(G)1148 Oct 2018 XCE04L8 FFG1148 Oct 2018 XCE04F10 FF(G)1152 Feb 2019Table 8: Virtex-4Q Defense-grade Devices-PackagesDevice Package-PinEstimatedcut-overdate codeDevice Package-PinEstimatedcut-overdate codeXQ4VLX60 EF668 1837 XQL4VFX100 FF1152 1837 XQ4VLX25 FF668 1918 XQL4VFX60 FF1152 2017 XQ4VLX40 FF668 1837 XQ4VFX100 FF(G)1152 2030 XQ4VLX60 FF668 1837 XQ4VFX60 FF(G)1152 1841 XQL4VLX60 FF668 1837 XQL4VLX200 FF(G)1513 1901 XQ4VSX35 FF(G)668 2019 XQ4VFX140 FF1517 2020 XQ4VFX60 EF672 1837 XQL4VFX140 FF(G)1517 1901 XQL4VFX40 FF672 1901 XQ4VLX25 SF363 1837 XQL4VFX60 FF672 1837。

RF_FPGASX50T芯片详细设计(版本号V2.13)

SP5203RF_FPGASX50T芯片详细设计文件编号xxxx修订 2.13版本记录:目录目录....................................................................................................................................... - 3 -1RF_FPGASX50T芯片简介............................................................................................. - 11 -1.1RF_FPGASX50T芯片的一级模块划分. (11)1.2RF_FPGASX50T芯片的内部功能模块结构图 (12)2时钟/复位控制模块..................................................................................................... - 13 -2.1功能描述 . (13)2.2接口说明 (13)2.3实现说明 (13)2.3.1rst_sync模块:..................................................................................................... - 14 -2.4表项/寄存器设置 (15)2.5重要资源使用情况说明 (15)3LBUS控制模块 ............................................................................................................ - 16 -3.1功能描述 . (16)3.2接口说明 (16)3.3实现说明 (16)3.3.1LBUS译码模块:.................................................................................................. - 17 -3.3.2小数分频模块................................................................................................... - 19 -3.3.3温度监控模块................................................................................................... - 22 -3.3.4ADC检波控制模块 ............................................................................................... - 23 -3.3.5FLASH接口模块.................................................................................................... - 25 -3.3.6SP5162时钟板I2C控制模块 ............................................................................... - 27 -3.3.7SP5162时钟板本振控制模块 .............................................................................. - 28 -3.3.8AD9779A控制模块............................................................................................... - 33 -3.3.9ADS62C15控制模块 ............................................................................................. - 34 -3.3.10SP5161通路板控制接口模块.......................................................................... - 34 -3.3.11发射功率自动校准模块................................................................................... - 35 -3.3.12发射本振自动控制模块................................................................................... - 38 -3.3.13接收参考电平自动校准模块........................................................................... - 38 -3.3.14发射BRAM数据源控制模块........................................................................... - 41 -3.3.15DDR2访问仲裁控制模块................................................................................. - 42 -3.3.16发射链路自动开关模块................................................................................... - 43 -3.4表项/寄存器说明 (44)4GTP收发模块 .............................................................................................................. - 45 -4.1功能描述 . (45)4.2接口说明 (45)4.3实现说明 (46)4.3.1时钟的设计....................................................................................................... - 46 -4.3.2Virtex-5 FPGA Rocket IO复位设计 ....................................................................... - 47 -4.3.3GTP用户接口设计 ............................................................................................... - 47 -4.3.1GTP链路检测 ....................................................................................................... - 50 -4.4重要资源使用情况说明 . (50)5发射链路信号处理模块............................................................................................... - 51 -5.1功能描述 . (51)5.2接口说明 (51)5.3实现说明 (51)5.3.1发射FIR滤波器组:........................................................................................ - 51 -5.3.2数据源选择:................................................................................................... - 60 -5.3.3数字上变频:................................................................................................... - 61 -5.3.4数字域增益调整:........................................................................................... - 62 -5.3.5发射功率补偿:............................................................................................... - 62 -5.3.6IQ平衡补偿: ...................................................................................................... - 64 -5.3.7LO直流补偿:...................................................................................................... - 64 -5.4重要资源使用情况说明 . (65)6接收链路信号处理模块............................................................................................... - 66 -6.2接口说明 (66)6.3实现说明 (66)6.3.1DC OFFSET校准: ................................................................................................ - 67 -6.3.2模拟补偿滤波:............................................................................................... - 67 -6.3.3接收功率补偿:............................................................................................... - 68 -6.3.4数字下变频:................................................................................................... - 68 -6.3.5接收FIR滤波器组:........................................................................................ - 68 -6.3.6接收BRAM缓存:........................................................................................... - 70 -6.3.7192X数据采样:.................................................................................................. - 71 -6.3.8DFT功率计算:.................................................................................................... - 71 -6.4重要资源使用情况说明 . (71)7DDR2接口模块............................................................................................................ - 72 -7.1功能描述 . (72)7.2接口说明 (72)7.3实现说明 (73)7.3.1MIG简要配置....................................................................................................... - 73 -7.3.2ddr2各模块功能介绍 .......................................................................................... - 74 -7.3.3用户接口时序说明........................................................................................... - 75 -7.4重要资源使用情况说明 . (76)8参考资料 ..................................................................................................................... - 77 -9附录一:FLASH表项介绍 ........................................................................................... - 78 -9.1发射功率校准表 . (80)9.2发射LO直流补偿表 (82)9.3发射IQ平衡补偿表 (82)9.4接收功率补偿表 (82)9.5板卡信息表 (83)10附录二:内部寄存器地址分配说明........................................................................ - 85 -10.1.1版本寄存器....................................................................................................... - 92 -10.1.2版本补充寄存器............................................................................................... - 92 -10.2板卡控制寄存器 . (92)10.2.1板卡控制寄存器............................................................................................... - 92 -10.3SP5161通路板控制寄存器 .. (92)10.3.1SP5161通路板控制寄存器.............................................................................. - 92 -10.3.2SP5161控制接口读数据寄存器 ...................................................................... - 93 -10.4发射功率补偿寄存器 .. (93)10.4.1功率模式寄存器............................................................................................... - 93 -10.4.2输出功率寄存器............................................................................................... - 93 -10.4.3功率补偿状态寄存器....................................................................................... - 94 -10.4.4反馈补偿校准控制寄存器............................................................................... - 94 -10.4.5发射功率补偿控制寄存器............................................................................... - 94 -10.4.6发射功率补偿寄存器值I/Q ............................................................................. - 94 -10.4.7发射功率自动控制基准功率........................................................................... - 95 -10.4.8发射功率补偿反馈值....................................................................................... - 95 -10.4.9发射功率自动设置补偿值d ............................................................................ - 95 -10.4.10发射功率自动设置补偿值0 ........................................................................... - 95 -10.4.11发射功率自动设置补偿值1 ........................................................................... - 95 -10.4.12发射功率自动设置补偿值2 ........................................................................... - 96 -10.4.13发射功率自动设置补偿值3 ........................................................................... - 96 -10.4.14发射功率自动设置补偿值4 ........................................................................... - 96 -10.4.15OUT口和IO口的固定差损值 ......................................................................... - 96 -10.4.16发射功率自动设置ATT1初始值 .................................................................... - 96 -10.4.17发射功率自动设置多级ATT补偿值 .............................................................. - 96 -10.4.18发射功率自动设置DDS默认值...................................................................... - 97 -10.4.19发射功率50M带内补偿值............................................................................. - 97 -10.5接收功率补偿寄存器 .. (97)10.5.1输入功率寄存器............................................................................................... - 97 -10.5.3接收功率0dbfs基准值.................................................................................... - 98 -10.5.4接收功率补偿寄存器值I/Q ............................................................................. - 98 -10.5.5接收参考电平自动设置ATT参考值............................................................... - 98 -10.5.6接收功率补偿反馈值....................................................................................... - 98 -10.5.7接收功率自动设置补偿值d ............................................................................ - 99 -10.5.8接收功率自动设置补偿值............................................................................... - 99 -10.5.9接收功率自动设置补偿值0 ............................................................................ - 99 -10.5.10接收功率自动设置补偿值1 ........................................................................... - 99 -10.5.11接收功率自动设置补偿值2 ........................................................................... - 99 -10.5.12接收功率计算值 ............................................................................................ - 100 -10.5.13接收功率自动设置DDS默认值.................................................................... - 100 -10.5.14接收功率自动设置DDC默认值 ................................................................... - 100 -10.5.15接收功率50M带内补偿值........................................................................... - 100 -10.6射频本振控制寄存器 (101)10.6.1射频频率控制寄存器..................................................................................... - 101 -10.6.2射频发射频率寄存器..................................................................................... - 101 -10.6.3射频接收频率寄存器..................................................................................... - 101 -10.6.4射频VCO寄存器............................................................................................ - 101 -10.6.5锁定计数器..................................................................................................... - 102 -10.7FLASH控制寄存器 .. (102)10.7.1FLASH地址寄存器.......................................................................................... - 102 -10.7.2FLASH写数据寄存器...................................................................................... - 103 -10.7.3FLASH读数据寄存器...................................................................................... - 103 -10.7.4FLASH操作控制寄存器.................................................................................. - 103 -10.8温度控制模块寄存器 (104)10.8.1温度控制寄存器............................................................................................. - 104 -10.8.2温度门限寄存器............................................................................................. - 104 -10.8.3温度状态寄存器............................................................................................. - 104 -10.9IIC数字电位计控制 (104)10.9.2IIC使能启动寄存器........................................................................................ - 105 -10.9.3IIC状态寄存器................................................................................................ - 105 -10.10D/A转换模块寄存器 (105)10.10.1AD9779A SPI数据寄存器............................................................................... - 105 -10.10.2AD9779A SPI使能启动寄存器 ....................................................................... - 105 -10.10.3AD9779A SPI状态寄存器............................................................................... - 105 -10.11直流补偿寄存器. (106)10.11.1LO直流补偿控制寄存器................................................................................ - 106 -10.11.2LO直流补偿寄存器值.................................................................................... - 106 -10.11.3LO直流补偿固化值 ....................................................................................... - 106 -10.12数字域增益控制寄存器 . (106)10.12.1发射增益调整控制寄存器 ............................................................................ - 106 -10.12.2发射增益调整寄存器值 ................................................................................ - 107 -10.12.3LO直流补偿固化值 ....................................................................................... - 107 -10.13IQ平衡控制寄存器 .. (107)10.13.1IQ平衡控制寄存器 ........................................................................................ - 107 -10.13.2IQ平衡寄存器值 ............................................................................................ - 107 -10.13.3IQ平衡固化值 ................................................................................................ - 108 -10.14VCO小数分频寄存器.. (108)10.14.1VCO小数分频控制寄存器............................................................................. - 108 -10.14.2VCO小数分频参数N ..................................................................................... - 108 -10.14.3VCO小数分频参数P ...................................................................................... - 108 -10.14.4VCO小数分频参数Q ..................................................................................... - 108 -10.15AD7680控制模块寄存器 .. (109)10.15.1AD7680控制寄存器....................................................................................... - 109 -10.15.2AD7680数据寄存器....................................................................................... - 109 -10.16A/D转换模块寄存器 (109)10.16.1ADS62C15 SPI数据寄存器 ............................................................................. - 109 -10.16.2ADS62C15 SPI使能启动寄存器 ..................................................................... - 109 -10.17SP5162时钟板控制寄存器 (110)10.17.1SP5162时钟板控制寄存器............................................................................ - 110 -10.18发射链路BRAM控制.. (110)10.18.1发射Bram控制寄存器 ................................................................................. - 110 -10.18.2发射Bram数据 ............................................................................................. - 110 -10.18.3发射Bram截止地址 ..................................................................................... - 111 -10.19接收链路BRAM控制.. (111)10.19.1接收Bram控制寄存器 ................................................................................. - 111 -10.19.2接收Bram数据 ............................................................................................. - 111 -10.20内部DDS控制寄存器 . (112)10.20.1发射内部DDS控制寄存器 ........................................................................... - 112 -10.20.2发射内部DDS控制数据 ............................................................................... - 112 -10.21DUC DDS控制寄存器 .. (112)10.21.1DUC DDS控制寄存器 ..................................................................................... - 112 -10.21.2DUC DDS控制数据 ......................................................................................... - 112 -10.22DDC DDS控制寄存器 .. (113)10.22.1DDC DDS控制寄存器 ..................................................................................... - 113 -10.22.2DDC DDS控制数据 ......................................................................................... - 113 -10.23功率自动控制模块 (113)10.23.1功率自动控制开关 ........................................................................................ - 113 -10.24芯片状态寄存器. (113)10.24.1芯片状态寄存器 ............................................................................................ - 113 -10.25模拟补偿滤波器模块 .. (114)10.25.1模拟补偿滤波器控制寄存器 ........................................................................ - 114 -10.25.2模拟补偿滤波器系数 .................................................................................... - 114 -10.26DDR2控制模块寄存器 (114)10.26.1DDR2控制寄存器........................................................................................... - 114 -10.26.2DDR2接收地址寄存器................................................................................... - 115 -10.26.3DDR2发射地址寄存器................................................................................... - 115 -10.27.1ADF4001状态寄存器 ..................................................................................... - 116 -10.28滤波器模式控制寄存器 . (116)10.28.1滤波器模式控制寄存器 ................................................................................ - 116 -10.29GTP链路检测寄存器表 . (116)10.29.1GTP链路检测寄存器表 ................................................................................. - 116 -1 RF_FPGASX50T芯片简介RF_FPGASX50T芯片是北京星河亮点通信软件有限责任公司研发的芯片,使用美国XILINX公司的XC5VSX50T-1FFG665C实现,应用于自主研发的射频模块。

FPGA可编程逻辑器件芯片XC5VFX130T-1FF1738C中文规格书

Application Note: Virtex-5 FPGAsSummary Virtex®-5 FPGAs and ISE® software support configuration from and programming of industry-standard, parallel NOR flash memory (BPI PROMs). Industry standard BPI PROMs are analternate solution for Virtex-5 FPGA designs whose requirements are not met by the PlatformFlash XL configuration and storage device (see [Ref1] for more information on Platform FlashXL). The iMPACT software, included in the ISE® development software tools, provides indirectprogramming for select BPI PROMs during prototyping. This application note demonstrateshow to program a Numonyx StrataFlash P30 BPI PROM indirectly using iMPACT 11.4 and aXilinx cable. In this solution, the Virtex-5 FPGA serves as a bridge between the IEEE Std1149.1 (JTAG) bus interface and the BPI bus interface. The required hardware setup, BPI-UPPROM file generation flow, and BPI indirect programming flow are shown. The Virtex-5 FPGABPI-UP configuration sequence is also described.Note:Parallel NOR flash memory is referred to by the term BPI PROM throughout this document.PROM (connected to the FPGA's BPI bus interface). This extra logic must be downloaded into the FPGA by iMPACT before indirect programming is possible.This application note is divided into three main sections. The first section discusses the hardware connections required for the indirect in-system programming of BPI PROMs for prototype designs. The second section shows the Xilinx software tool flows for generating a PROM file formatted for 16-bit BPI-UP mode and then for programming the select BPI PROMs. The third section provides a basic configuration flow overview for the FPGA after the BPI PROM is programmed and describes expectations when using this indirect setup.iMPACT Indirect In-System Programming with aVirtex-5 FPGA The basic hardware setup required for the iMPACT indirect BPI PROM programming method is shown in Figure1.Minimum Requirements•Virtex-5FPGA•BPI PROM (refer to Table1)•Xilinx Cable and Connector (refer to T able4, page7)•ISE iMPACT Software 11.4Note:Indirect BPI PROM programming was introduced with limited device support in iMP ACT 9.2i.This application note demonstrates the software flow and lists the device support in iMP ACT 11.4.Figure 1:iMPACT Indirect BPI PROM Programming with a Virtex-5 FPGASelecting BPI PROMsSeveral factors are considered when selecting a BPI PROM (including BPI PROM family, density, package, and the data bus width). When using iMPACT for programming, the BPI PROM family must be selected from the supported list in T able 1. After the BPI PROM family is selected, consider the BPI PROM density. All of the Virtex-5 FPGAs can be configured from a single BPI PROM (typical configuration density requirements for Virtex-5 FPGAs are provided in Table 2). A larger BPI PROM can be used for daisy-chained applications, storing multiple FPGA configuration bitstreams, or for applications storingadditional user data, such as code for embedded MicroBlaze™ core or embedded PowerPC™ processors.Table 1: BPI PROM Programming Capability with iMPACTBPI PROM Vendor (1)Family (2)Density NumonyxStrataFlash Embedded P30 (28FxxxP30)(3)64Mb–1Gb Embedded J3 v. D or F (28FxxxJ3)32Mb–256MbNotes:1.Refer to Software Flows for BPI File Preparation and Programming, page 9 for more information.2.Numonyx StrataFlash Embedded P30 monolithic die and top-boot options are supported by the iMP ACT indirect BPI programming solution. Numonyx stacked die, bottom, or uniform boot options are not supported.Table 2: Typical Virtex-5 FPGA Configuration Bit RequirementsXilinx FPGA Configuration Bits (Per Device)Smallest BPI PROMRequiredXC5VLX308,374,0168Mb XC5VLX5012,556,67216Mb XC5VLX8521,845,632 32Mb XC5VLX11029,124,60832Mb XC5VLX15541,048,06464Mb XC5VLX22053,139,45664Mb XC5VLX33079,704,832128Mb XC5VLX20T 6,251,2008Mb XC5VLX30T 9,371,13616Mb XC5VLX50T 14,052,35216Mb XC5VLX85T 23,341,31232Mb XC5VLX110T 31,118,84832Mb XC5VLX155T 43,042,30464Mb XC5VLX220T 55,133,69664Mb XC5VLX330T 82,696,192128Mb XC5VSX35T 13,349,12016Mb XC5VSX50T 20,019,32832Mb XC5VSX95T 35,716,09664Mb XC5VSX240T 79,610,368128Mb XC5VTX150T 43,278,46464 Mb XC5VTX240T65,755,64864MbXC5VFX30T13,517,05616Mb XC5VFX70T 27,025,40832Mb XC5VFX100T 39,389,696 64Mb XC5VFX130T 49,234,94464Mb XC5VFX200T70,856,704128MbTable 2: Typical Virtex-5 FPGA Configuration Bit Requirements (Cont’d)Notes:1.VCC_CONFIG (VCCO_0) is the configuration output supply voltage and supplies the dedicated configuration pins: TMS, TCK, TDO, TDI,M[2:0], HSWAPEN, PROGRAM_B, DONE, INIT_B, CCLK, D_IN.2.VCCO_1 supplies A[19:0].3.VCCO_2 supplies FCS_B, FOE_B, FWE_B, A[25:20], and D[0:7].4.VCCO_4 supplies D[8:15].5.It is recommended to have the option for both JT AG (M[2:0]=101) and BPI_UP (M[2:0]=010) configuration modes.6.HSWAPEN can be driven Low to enable pull-ups on I/O.7.RS[1:0] and CSO_B signals are used for advanced daisy-chain and revisioned applications. These signals are not connected for this setup.Refer to [Ref4] for detailed information.8.With iMP ACT versions 11.3 and later, pin IO_L9P_CC_GC_4 is pulled High when the P30 flash family is targeted. Before iMP ACT 11.3, it wasrecommended that the IO_L9P_CC_GC_4 pin be reserved and not connected in a design using the iMP ACT indirect programming core. If this signal is used, the target application must consider that the iMP ACT indirect programming core will drive this signal Low.Caution!The iMP ACT indirect programming solution drives all FPGA address lines (A[25:0]) during ISP operations on the BPI PROM.Figure 2:BPI Configuration Mode Setup (Master Virtex-5 FPGA and Slave BPI PROM)。

FPGA可编程逻辑器件芯片XQ5VFX100T中文规格书

TDO_0

PROGRAM_B

CCLK_0

TCK_0

TMS

The RocketIO™ GTP transceiver I/O channels for the devices listed in Table 1-3 or the GTX transceiver I/O channels for the devices listed in Table 1-4.

Table 1-1: Flip-Chip Packages

Package

Packages

Specifications FF323 FF324 FF665 FF676 FF1136 FF1153 FF1156

Pitch (mm) 1.00 1.00 1.00 1.00 1.00 1.00

1.00

Size (mm) 19 x 19 19 x 19 27 x 27 27 x 27 35 x 35 35 x 35 35 x 35

H13

24 IO_L7P_24

H10

24 IO_L7N_24

J10

24 IO_L8P_CC_24

H14

24 IO_L8N_CC_24(2 )

H15

24 IO_L9P_CC_24

K10

Virtex-5 FPGA Packaging and Pinout Specification

Maximum I/Os

172

220

360

440

640

800

360

FF1738 1.00 42.5 x 42.5

960

FF1759 1.00 42.5 x 42.5

680

FF1760 1.00 42.5 x 42.5

FPGA可编程逻辑器件芯片XQ5VFX130T-1F1738C中文规格书

48

96 48 1,728 6 不适用 不适用 不适用 不适用 不适用 17 560

XC5VLX85

120 x 54 12,960

840

48

192 96 3,456 6 不适用 不适用 不适用 不适用 不适用 17 560

XC5VLX110 XC5VLX155

160 x 54 17,280 160 x 76 24,320

XC5VLX330 240 x 108 51,840 3,420

192 576 288 10,368 6 不适用 不适用 不适用 不适用 不适用 33 1,200

XC5VLX20T 60 x 26 3,120

210

24

52 26 936 1 不适用

1

2

4 不适用 7 172

XC5VLX30T 80 x 30 4,800

DS100 (v5.0) 2009 年 2 月 6 日 产品规范

Virtex-5 系列概述

数控阻抗 (DCI) 有源 I/O 终端 • 可选串行或并行终端 • 温度和电压补偿 • 显著简化电路板布局

- 减少电阻器 - 在理想的位置设置终端,比如信号源或信号终点

65nm 铜 CMOS 工艺

• 1.0V 内核电压 • 12 层金属提供最强的布线功能,并可容纳硬 IP 植入 • 三栅极氧化层技术,确实可降低静态功耗

1,120 1,640

64

256 128 4,608 6 不适用 不适用 不适用 不适用 不适用 23 800

128 384 192 6,912 6 不适用 不适用 不适用 不适用 不适用 23 800

XC5VLX220 160 x 108 34,560 2,280

FPGA可编程逻辑器件芯片XQ5VFX130T-1F1738I中文规格书

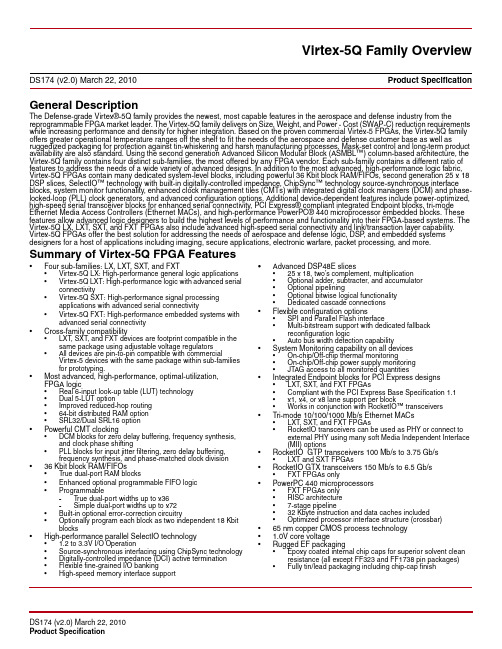

General DescriptionThe Defense-grade Virtex®-5Q family provides the newest, most capable features in the aerospace and defense industry from the reprogrammable FPGA market leader. The Virtex-5Q family delivers on Size, Weight, and Power - Cost (SWAP-C) reduction requirements while increasing performance and density for higher integration. Based on the proven commercial Virtex-5 FPGAs, the Virtex-5Q family offers greater operational temperature ranges off the shelf to fit the needs of the aerospace and defense customer base as well as ruggedized packaging for protection against tin-whiskering and harsh manufacturing processes. Mask-set control and long-term product availability are also standard. Using the second generation Advanced Silicon Modular Block (ASMBL™) column-based architecture, the Virtex-5Q family contains four distinct sub-families, the most offered by any FPGA vendor. Each sub-family contains a different ratio of features to address the needs of a wide variety of advanced designs. In addition to the most advanced, high-performance logic fabric, Virtex-5Q FPGAs contain many dedicated system-level blocks, including powerful 36Kbit block RAM/FIFOs, second generation 25x18 DSP slices, SelectIO™ technology with built-in digitally-controlled impedance, ChipSync™ technology source-synchronous interface blocks, system monitor functionality, enhanced clock management tiles (CMTs) with integrated digital clock managers (DCM) and phase-locked-loop (PLL) clock generators, and advanced configuration options. Additional device-dependent features include power-optimized, high-speed serial transceiver blocks for enhanced serial connectivity, PCI Express® compliant integrated Endpoint blocks, tri-mode Ethernet Media Access Controllers (Ethernet MACs), and high-performance PowerPC®440 microprocessor embedded blocks. These features allow advanced logic designers to build the highest levels of performance and functionality into their FPGA-based systems. The Virtex-5Q LX, LXT, SXT, and FXT FPGAs also include advanced high-speed serial connectivity and link/transaction layer capability. Virtex-5Q FPGAs offer the best solution for addressing the needs of aerospace and defense logic, DSP, and embedded systems designers for a host of applications including imaging, secure applications, electronic warfare, packet processing, and more. Summary of Virtex-5Q FPGA Features•Four sub-families: LX, LXT, SXT, and FXT•Virtex-5Q LX: High-performance general logic applications •Virtex-5Q LXT: High-performance logic with advanced serial connectivity•Virtex-5Q SXT: High-performance signal processing applications with advanced serial connectivity•Virtex-5Q FXT: High-performance embedded systems with advanced serial connectivity•Cross-family compatibility•LXT, SXT, and FXT devices are footprint compatible in the same package using adjustable voltage regulators •All devices are pin-to-pin compatible with commercial Virtex-5 devices with the same package within sub-familiesfor prototyping.•Most advanced, high-performance, optimal-utilization, FPGA logic•Real 6-input look-up table (LUT) technology•Dual 5-LUT option•Improved reduced-hop routing•64-bit distributed RAM option•SRL32/Dual SRL16 option•Powerful CMT clocking•DCM blocks for zero delay buffering, frequency synthesis, and clock phase shifting•PLL blocks for input jitter filtering, zero delay buffering, frequency synthesis, and phase-matched clock division •36Kbit block RAM/FIFOs•T rue dual-port RAM blocks•Enhanced optional programmable FIFO logic•Programmable-T rue dual-port widths up to x36-Simple dual-port widths up to x72•Built-in optional error-correction circuitry•Optionally program each block as two independent 18Kbit blocks•High-performance parallel SelectIO technology• 1.2 to 3.3V I/O Operation•Source-synchronous interfacing using ChipSync technology •Digitally-controlled impedance (DCI) active termination•Flexible fine-grained I/O banking•High-speed memory interface support •Advanced DSP48E slices•25x18, two’s complement, multiplication•Optional adder, subtracter, and accumulator•Optional pipelining•Optional bitwise logical functionality•Dedicated cascade connections•Flexible configuration options•SPI and Parallel Flash interface•Multi-bitstream support with dedicated fallbackreconfiguration logic•Auto bus width detection capability•System Monitoring capability on all devices•On-chip/Off-chip thermal monitoring•On-chip/Off-chip power supply monitoring•JT AG access to all monitored quantities•Integrated Endpoint blocks for PCI Express designs •LXT, SXT, and FXT FPGAs•Compliant with the PCI Express Base Specification 1.1•x1, x4, or x8 lane support per block•Works in conjunction with RocketIO™ transceivers•Tri-mode 10/100/1000 Mb/s Ethernet MACs•LXT, SXT, and FXT FPGAs•RocketIO transceivers can be used as PHY or connect to external PHY using many soft Media Independent Interface(MII)options•RocketIO GTP transceivers 100Mb/s to 3.75Gb/s •LXT and SXT FPGAs•RocketIO GTX transceivers 150Mb/s to 6.5Gb/s•FXT FPGAs only•PowerPC 440 microprocessors•FXT FPGAs only•RISC architecture•7-stage pipeline•32Kbyte instruction and data caches included•Optimized processor interface structure (crossbar)•65nm copper CMOS process technology• 1.0V core voltage•Rugged EF packaging•Epoxy coated internal chip caps for superior solvent clean resistance (all except FF323 and FF1738 pin packages)•Fully tin/lead packaging including chip-cap finishVirtex-5Q Family OverviewDS174 (v2.0) March 22, 2010Product SpecificationInput/Output Blocks (SelectIO)IOBs are programmable and can be categorized as follows:•Programmable single-ended or differential (LVDS) operation•Input block with an optional single data rate (SDR) or double data rate (DDR) register•Output block with an optional SDR or DDR register •Bidirectional block•Per-bit deskew circuitry•Dedicated I/O and regional clocking resources•Built-in data serializer/deserializerThe IOB registers are either edge-triggered D-type flip-flops or level-sensitive latches.special hardware connections for I/O in the same locality. These regional clock inputs are distributed within a limited region to minimize clock skew between IOBs. Regional I/O clocking supplements the global clocking resources.Data serializer/deserializer capability is added to every I/O to support source-synchronous interfaces. A serial-to-parallel converter with associated clock divider is included in the input path, and a parallel-to-serial converter in the output path.An in-depth guide to the Virtex-5Q FPGA IOB is found in UG194, Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC User Guide.Package FF323FF1738EF676EF665EF1136EF1153EF1738 Size(mm)19x1927x2727x2735x3535x3542.5x42.5 Device GTs I/O GTs I/O GTs I/O GTs I/O GTs I/O GTs I/O XQ5VLX85N/A440XQ5VLX110N/A440N/A800XQ5VLX30T 4 GTPs172XQ5VLX110T16 GTPs640XQ5VLX155T16 GTPs640XQ5VLX220T16 GTPs680 XQ5VLX330T24 GTPs960 XQ5VSX50T8 GTPs360XQ5VSX95T16 GTPs640XQ5VSX240T24 GTPs960XQ5VFX70T8 GTXs36016 GTXs640XQ5VFX100T16 GTXs64016 GTXs680 XQ5VFX130T20 GTXs840 XQ5VFX200T24 GTXs960Virtex-5Q FPGA DocumentationComplete and up-to-date documentation of the Virtex-5Q family of FPGAs is available on the Xilinx website. In addition to the most recent Virtex-5Q Family Overview, the following files are also available for download:Virtex-5Q FPGA Data Sheet: DC and Switching Characteristics (DS714)This data sheet contains the DC and Switching Characteristic specifications for the Virtex-5Q family. Virtex-5 FPGA User Guide (UG190)This guide includes chapters on:•Clocking Resources•Clock Management T echnology (CMT)•Phase-Locked Loops (PLL)•Block RAM•Configurable Logic Blocks (CLBs)•SelectIO Resources•SelectIO Logic Resources•Advanced SelectIO Logic ResourcesVirtex-5 FPGA XtremeDSP Design Considerations (UG193)This guide describes the DSP48E slice and includes reference designs for using DSP48E math functions and various filters.Virtex-5 FPGA Configuration Guide (UG191)This all-encompassing configuration guide includes chapters on configuration interfaces (serial and parallel), multi-bitstream management, bitstream encryption, Boundary-Scan and JT AG configuration, and reconfiguration techniques.Virtex-5 FPGA Packaging and Pinout Specification (UG195)This specification includes the tables for device/package combinations and maximum I/Os, pin definitions, pinout tables, pinout diagrams, mechanical drawings, and thermal specifications.Virtex-5 FPGA PCB Designer’s Guide (UG203)This guide provides information on PCB design forVirtex-5Q devices, with a focus on strategies for making design decisions at the PCB and interface level.Virtex-5 FPGA System Monitor User Guide (UG192) The System Monitor functionality is outlined in this guide.Virtex-5 FPGA RocketIO GTP Transceiver User Guide (UG196)This guide describes the RocketIO GTP transceivers available in the Virtex-5Q LXT and SXT FPGAs.Virtex-5 FPGA RocketIO GTX Transceiver User Guide (UG198)This guide describes the RocketIO GTX transceivers available in the Virtex-5Q FXT FPGAs.Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC User Guide (UG194)This guide describes the dedicated Tri-Mode Ethernet Media Access Controller available in the Virtex-5Q LXT, SXT, and FXT FPGAs.Virtex-5 FPGA Integrated Endpoint Block for PCI Express Designs User Guide (UG197)This guide describes the integrated Endpoint blocks in the Virtex-5Q LXT, SXT, and FXT FPGAs that are PCI Express compliant.Embedded Processor Block in Virtex-5 FPGAs Reference Guide (UG200)This reference guide is a description of the embedded processor block available in the Virtex-5Q FXT FPGAs.。