串口通信Verilog代码

rs串口verilog代码

UART是通用异步收发器的简称,其中有一种电平规范较RS232规范,它用-3~-15V表示正逻辑,3~15V表示负逻辑,通过FPGA芯片实现RS232通信首先要解决的就是FPGA电平和RS232电平之间的矛盾,通常采用MAX3232作为物理层的电平接口,根据MAX3232提供的标准配制方式把物理电路设计好后,接下来的通信就是要实现逻辑的接收和发送……设计最简单的RS232通信逻辑,FPGA实现将接收到的数据会发出去,总共两个数据传输引脚,一收一发。

将此通信模块分为三个部分:接收模块,波特率控制模块,发送模块。

工作原理:此模块接收MAX3232传过来的串行数据,对齐进行判断采样,校验,最后将数据流中的串行数据转换为八位并行数据,将此八位数据储存,或送给发送模块发送出去。

根据RS232通信标准器串行数据分为起始位、数据位、校验位、停止位,空闲时为高电平,起始位通常为低电平,数据位通常为8位,校验位分为奇校验、偶校验等,停止位一位或两位且为高电平。

FPGA接收模块对此数据进行异步接收,首先就要检测其数据传输开始标识,当然就是检测开始位,于是要有下降沿检测电路,检测到下降沿是输出一高脉冲,此电路可以用两个D触发器加上基本门电路实现,脉冲触发开始进入接收状态,输出接收状态标志位,使其为1,此标志位使能波特率控制模块输出采样脉冲,此计数脉冲触发接收模块中的计数器计数,加到相应的位就把当前的串行总线上的值赋给缓冲器,或对其判断,当计数完成11次计数后,已将8位串行数据转成并行数据到缓冲器中,且进行了校验的判断和停止位的判别,这是接收状态结束,接收状态位置0,计数器清零。

对于波特率产生模块用于控制采样数据脉冲的周期,其周期就为串行数据传送一个bit所用的时间,根据此时间和时钟周期设置计数值。

当接收模块完成工作时,接收状态位为0时可以触发发送模块,发送模块检测接收状态的下降沿,由此产生一高脉冲,与发送模块类似,根据波特率控制模块产生的计数脉冲将并行数据转成串行数据,并加上开始位、校验位、停止位。

verilog 逻辑函数 串口发送

verilog 逻辑函数串口发送摘要:1.Verilog 逻辑函数概述2.串口发送原理3.Verilog 实现串口发送的逻辑函数4.应用实例正文:【1.Verilog 逻辑函数概述】Verilog 是一种硬件描述语言,主要用于数字电路和模拟混合信号电路的描述。

它的语法简洁,易于理解和使用。

在数字电路设计中,逻辑函数是基本的构建模块,通过组合这些模块可以实现复杂的数字电路。

【2.串口发送原理】串口(Serial Port)是一种计算机硬件接口,可以通过串行通信传输数据。

发送数据时,数据被逐个比特按顺序传送,这样可以减少线路的传输次数,提高通信效率。

在电子设备中,如单片机、FPGA 等,通常会使用串口进行数据通信。

【3.Verilog 实现串口发送的逻辑函数】要实现串口发送功能,首先需要设计一个状态机,控制数据的发送过程。

下面是一个简单的Verilog 代码示例,实现一个8 位串口发送器:```verilogmodule serial_port_sender(input wire clk, // 时钟信号input wire rst_n, // 低电平复位信号input wire start, // 开始发送信号input wire [7:0] data, // 发送数据output wire busy // 忙碌信号);// 定义状态机typedef enum logic [1:0] {IDLE, SENDING} state_t; state_t current_state, next_state;always_ff @(posedge clk or negedge rst_n) begin if (!rst_n) begincurrent_state <= IDLE;end else begincurrent_state <= next_state;endendalways_comb begincase (current_state)IDLE: beginif (start &&!busy) beginnext_state = SENDING;endendSENDING: beginif (data == 8"b0000_0001) begin // 发送结束标志next_state = IDLE;end else begin// 发送数据busy = 1;next_state = SENDING;endendendcaseendendmodule```【4.应用实例】上述代码实现了一个简单的8 位串口发送器。

verilog 串口时钟相位控制字-概述说明以及解释

verilog 串口时钟相位控制字-概述说明以及解释1.引言1.1 概述概述部分的内容可以包括对verilog 串口时钟相位控制字的简要介绍和重要性的提及。

可以参考以下内容进行编写:在现代通信领域中,串口通信起到了至关重要的作用。

而在串口通信中,时钟相位控制字是一个非常关键的概念。

verilog 串口时钟相位控制字是指通过调节时钟信号的相位来进行数据传输的一种技术。

时钟相位控制字的作用在于确保在数据传输过程中,接收方能够正确地识别发送方发送的数据。

通过调整时钟信号的相位,可以使得接收方在正确的时间点对数据进行采样,从而减少数据传输过程中可能会出现的误差。

时钟相位控制字的设计和调整对于串口通信的稳定性和可靠性具有非常重要的意义。

合理地设置时钟相位控制字可以提高数据传输的成功率,并减少传输过程中可能出现的错误。

因此,了解verilog 串口时钟相位控制字的原理和作用对于串口通信的设计和实现是至关重要的。

在本篇文章中,将详细介绍verilog 串口时钟相位控制字的原理和作用,希望能够为读者提供一个全面的了解,并为未来的研究和应用提供有益的参考。

1.2文章结构1.2 文章结构本文将围绕Verilog串口时钟相位控制字展开讨论,主要分为以下几个部分:第一部分是引言,包括概述、文章结构和目的。

在概述部分,将介绍串口通信的基本原理和应用领域。

文章结构部分将简要介绍本文的章节安排和内容要点。

目的部分将说明本文的研究目的和意义。

第二部分是正文,主要包括串口通信原理和时钟相位控制字的作用。

在串口通信原理部分,将介绍串口通信的基本原理,包括数据传输的方式、波特率的定义和选择。

时钟相位控制字的作用部分将详细探讨时钟相位控制字在串口通信中的作用及其实现原理。

第三部分是结论,主要总结本文的主要内容和研究成果。

在总结部分,将回顾本文的研究目的和主要内容,并对所得出的结论进行归纳和概括。

对未来研究的展望部分将提出一些关于Verilog串口时钟相位控制字相关研究的展望和建议,以促进相关领域的进一步研究和发展。

基于Verilog HDL设计的UART模块

1 UART原理串行通信是指外部设备和计算机间使用一根数据线(另外需要地线,可能还需要控制线)进行数据传输的方式。

数据在一根数据线上一位一位传输,每一位数据都占据一个固定的时间长度。

与并行通信方式相比,串行通信方式的传输速度较慢,但这种通信方式使用的数据线少,在远距离通信中可以节约通信成本,因此得到了广泛的应用。

基本的UART只需要发送和接收两条数据线就可以完成数据的全双工通信,其基本功能是在发送端将控制器通过总线传过来的并行数据,以设定的格式,设定的频率串行地传输出去,并同时在接收端将串行接收到的数据,转换成相应的并行数据发送出去。

UART的基本帧格式如图1所示。

其中,起始位总是逻辑O状态,停止位总是逻辑l状态,其持续时间可选为1位、1.5位或2位,其数据位可为5、6、7、8位,校验位可根据需要选择奇校验位,偶校验位或无校验位。

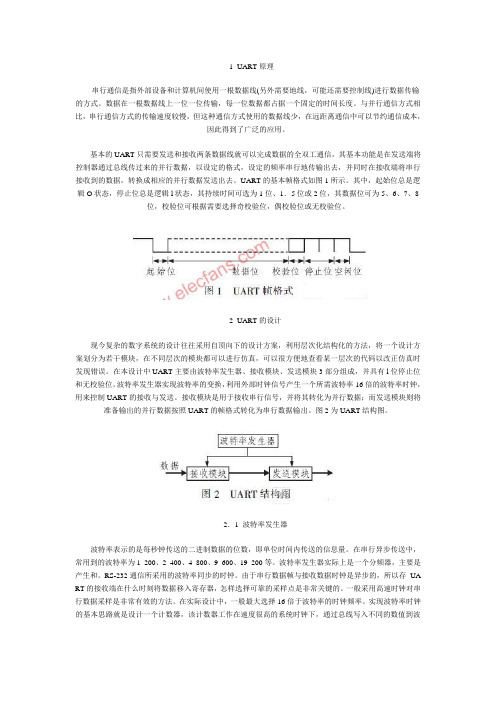

2 UART的设计现今复杂的数字系统的设计往往采用自顶向下的设计方案,利用层次化结构化的方法,将一个设计方案划分为若干模块,在不同层次的模块都可以进行仿真,可以很方便地查看某一层次的代码以改正仿真时发现错误。

在本设计中UART主要由波特率发生器、接收模块、发送模块3部分组成,并具有l位停止位和无校验位。

波特率发生器实现波特率的变换,利用外部时钟信号产生一个所需波特率16倍的波特率时钟,用来控制UART的接收与发送。

接收模块是用于接收串行信号,并将其转化为并行数据;而发送模块则将准备输出的并行数据按照UART的帧格式转化为串行数据输出。

图2为UART结构图。

2.1 波特率发生器波特率表示的是每秒钟传送的二进制数据的位数,即单位时间内传送的信息量。

在串行异步传送中,常用到的波特率为1 200、2 400、4 800、9 600、19 200等。

波特率发生器实际上是一个分频器,主要是产生和。

RS-232通信所采用的波特率同步的时钟。

由于串行数据帧与接收数据时钟是异步的,所以存UA RT的接收端在什么时刻将数据移入寄存器,怎样选择可靠的采样点是非常关键的。

电子教材-基于VerilogHDL的UART设计

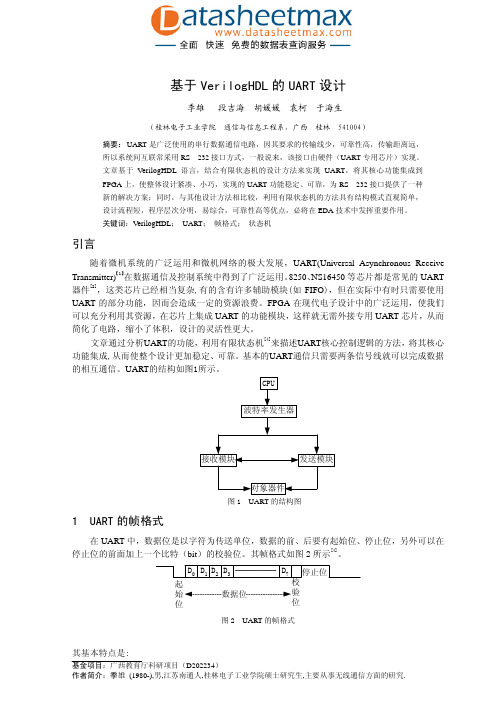

基于VerilogHDL的UART设计季雄段吉海胡媛媛袁柯于海生(桂林电子工业学院 通信与信息工程系,广西 桂林 541004)摘要:UART是广泛使用的串行数据通信电路,因其要求的传输线少,可靠性高,传输距离远,所以系统间互联常采用RS—232接口方式,一般说来,该接口由硬件(UART专用芯片)实现。

文章基于VerilogHDL语言,结合有限状态机的设计方法来实现UART,将其核心功能集成到FPGA上,使整体设计紧凑、小巧,实现的UART功能稳定、可靠,为RS—232接口提供了一种新的解决方案;同时,与其他设计方法相比较,利用有限状态机的方法具有结构模式直观简单,设计流程短,程序层次分明,易综合,可靠性高等优点,必将在EDA技术中发挥重要作用。

关键词:VerilogHDL; UART;帧格式;状态机引言随着微机系统的广泛运用和微机网络的极大发展,UART(Universal Asynchronous Receive Transmitter)【1】在数据通信及控制系统中得到了广泛运用。

8250、NS16450等芯片都是常见的UART 器件[2],这类芯片已经相当复杂,有的含有许多辅助模块(如FIFO),但在实际中有时只需要使用UART的部分功能,因而会造成一定的资源浪费。

FPGA在现代电子设计中的广泛运用,使我们可以充分利用其资源,在芯片上集成UART的功能模块,这样就无需外接专用UART芯片,从而简化了电路,缩小了体积,设计的灵活性更大。

文章通过分析UART的功能,利用有限状态机[4]来描述UART核心控制逻辑的方法,将其核心功能集成,从而使整个设计更加稳定、可靠。

基本的UART通信只需要两条信号线就可以完成数据的相互通信。

UART的结构如图1所示。

图1 UART的结构图1 UART的帧格式在UART中,数据位是以字符为传送单位,数据的前、后要有起始位、停止位,另外可以在停止位的前面加上一个比特(bit)的校验位。

verilog RS232 串口通信 verilog

module uart_top(clk,rs232_rx,rs232_tx);

input clk; //时钟信号50M

input rs232_rx; //数据输入信号

bps_start,

clk_bps,

rs232_rx,

rx_data,

rx_int

);

input clk; //50MHz时钟

input rst_n; //低电平复位信号

input rs232_rx; //接收数据信号

);

uart_rx uart_rx(//数据接收模块

.clk(clk),

.rst_n(rst_n),

.bps_start(bps_start1),

.clk_bps(clk_bps1),

.rs232_rx(rs232_rx),

.rx_data(rx_data),

else

begin

if(int_cnt<250) int_cnt<=int_cnt+1'b1;

end

end

assign data_flg=(int_cnt==10)?1'b1:1'b0;

always @(posedge data_flg or negedge rst_n)

output rs232_tx; //数据输出信号

wire clk_bps1,clk_bps2;

wire bps_start1,bps_start2;

wire [7:0] rx_data;

i2s的verilog代码

i2s的verilog代码i2s的Verilog代码是指用Verilog语言编写的用于实现i2s (Inter-IC Sound)接口功能的代码。

i2s接口是一种常用的音频数据传输接口,广泛应用于音频芯片、音频设备和数字信号处理器等领域。

i2s接口由三根线组成,分别是时钟线(SCLK)、数据线(SD)和帧同步线(WS)。

时钟线用于同步数据的传输,数据线用于传输音频数据,帧同步线用于标志数据的起始和结束。

在Verilog代码中,首先需要定义i2s接口的输入输出端口,并根据接口规范进行信号的定义和赋值。

接下来可以根据具体的应用需求,编写相应的模块和逻辑来实现i2s接口的功能。

一个简单的i2s接口的Verilog代码示例如下:```verilogmodule i2s_interface (input wire SCLK, // 时钟线input wire SD, // 数据线input wire WS, // 帧同步线output wire audio // 音频数据输出);reg [15:0] audio_data; // 音频数据寄存器always @(posedge SCLK) beginif (WS) beginaudio_data <= SD; // 读取音频数据endendassign audio = audio_data; // 输出音频数据endmodule```上述代码中,定义了一个名为i2s_interface的模块,该模块包含了一个i2s接口,输入端口为SCLK、SD和WS,输出端口为audio。

在always块中,通过检测时钟线的上升沿,判断帧同步线的状态,如果帧同步线为高电平,则将数据线的数据存入音频数据寄存器中。

最后,通过assign语句将音频数据输出到audio端口。

需要注意的是,上述代码仅为示例,实际的i2s接口实现可能需要根据具体的应用需求进行修改和优化。

此外,在实际应用中,还需要考虑时序约束、数据格式、时钟频率等因素,以确保i2s接口的正常工作。

verilog串口通信程序【精选文档】

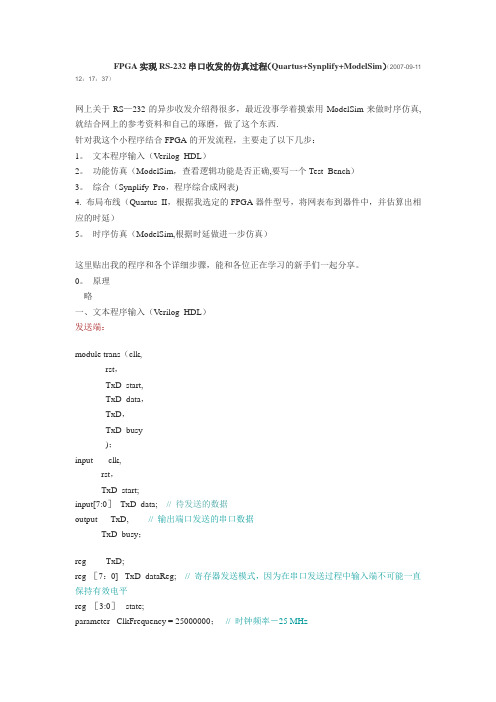

FPGA实现RS-232串口收发的仿真过程(Quartus+Synplify+ModelSim)(2007-09-11 12:17:37)网上关于RS—232的异步收发介绍得很多,最近没事学着摸索用ModelSim来做时序仿真,就结合网上的参考资料和自己的琢磨,做了这个东西.针对我这个小程序结合FPGA的开发流程,主要走了以下几步:1。

文本程序输入(Verilog HDL)2。

功能仿真(ModelSim,查看逻辑功能是否正确,要写一个Test Bench)3。

综合(Synplify Pro,程序综合成网表)4. 布局布线(Quartus II,根据我选定的FPGA器件型号,将网表布到器件中,并估算出相应的时延)5。

时序仿真(ModelSim,根据时延做进一步仿真)这里贴出我的程序和各个详细步骤,能和各位正在学习的新手们一起分享。

0。

原理略一、文本程序输入(Verilog HDL)发送端:module trans(clk,rst,TxD_start,TxD_data,TxD,TxD_busy);input clk,rst,TxD_start;input[7:0]TxD_data; // 待发送的数据output TxD, // 输出端口发送的串口数据TxD_busy;reg TxD;reg [7:0] TxD_dataReg; // 寄存器发送模式,因为在串口发送过程中输入端不可能一直保持有效电平reg [3:0]state;parameter ClkFrequency = 25000000;// 时钟频率-25 MHzparameter Baud = 115200;// 串口波特率-115200// 波特率产生parameter BaudGeneratorAccWidth = 16;reg [BaudGeneratorAccWidth:0]BaudGeneratorAcc;wire [BaudGeneratorAccWidth:0] BaudGeneratorInc = ((Baud〈<(BaudGeneratorAccWidth—4))+(ClkFrequency>>5))/(ClkFrequency>〉4);wire BaudTick = BaudGeneratorAcc[BaudGeneratorAccWidth];wire TxD_busy;always @(posedge clk or negedge rst)if(~rst)BaudGeneratorAcc <= 0;else if(TxD_busy)BaudGeneratorAcc <= BaudGeneratorAcc[BaudGeneratorAccWidth-1:0]+ BaudGeneratorInc;// 发送端状态wire TxD_ready = (state==0);// 当state = 0时,处于准备空闲状态,TxD_ready = 1 assign TxD_busy = ~TxD_ready; // 空闲状态时TxD_busy = 0// 把待发送数据放入缓存寄存器TxD_dataRegalways @(posedge clk or negedge rst)if(~rst)TxD_dataReg <= 8’b00000000;else if(TxD_ready &TxD_start)TxD_dataReg <= TxD_data;// 发送状态机always @(posedge clk or negedge rst)if(~rst)beginstate 〈= 4’b0000;// 复位时,状态为0000,发送端一直发1电平TxD <= 1'b1;endelsecase(state)4’b0000: if(TxD_start) beginstate <= 4’b0100;// 接受到发送信号,进入发送状态end4’b0100: if(BaudTick) beginstate <= 4’b1000;// 发送开始位—0电平TxD <= 1'b0;end4'b1000: if(BaudTick)beginstate <= 4'b1001;// bit 0TxD <= TxD_dataReg[0];end4'b1001:if(BaudTick) beginstate <= 4’b1010; // bit 1TxD 〈= TxD_dataReg[1];end4’b1010:if(BaudTick) beginstate <= 4'b1011; // bit 2TxD <= TxD_dataReg[2];end4'b1011:if(BaudTick)beginstate <= 4'b1100; // bit 3TxD 〈= TxD_dataReg[3];end4'b1100: if(BaudTick) beginstate 〈= 4’b1101;// bit 4TxD <= TxD_dataReg[4];end4'b1101:if(BaudTick) beginstate 〈= 4’b1110;// bit 5TxD 〈= TxD_dataReg[5];end4'b1110:if(BaudTick) beginstate <= 4’b1111; // bit 6TxD <= TxD_dataReg[6];end4’b1111:if(BaudTick) beginstate 〈= 4’b0010;// bit 7TxD <= TxD_dataReg[7];end4'b0010: if(BaudTick) beginstate 〈= 4'b0011;// stop1TxD 〈= 1’b1;end4’b0011:if(BaudTick)beginstate 〈= 4’b0000;// stop2TxD 〈= 1'b1;enddefault: if(BaudTick)beginstate 〈= 4’b0000;TxD 〈= 1’b1;endendcaseendmodule接收端:module rcv(clk,rst,RxD,RxD_data,RxD_data_ready,);input clk,rst,RxD;output[7:0] RxD_data; // 接收数据寄存器output RxD_data_ready;// 接收完8位数据,RxD_data 值有效时,RxD_data_ready 输出读信号parameter ClkFrequency = 25000000;// 时钟频率-25MHzparameter Baud = 115200; // 波特率-115200reg[2:0]bit_spacing;reg RxD_delay;reg RxD_start;reg[3:0] state;reg[7:0]RxD_data;reg RxD_data_ready;// 波特率产生,使用8倍过采样parameter Baud8 = Baud*8;parameter Baud8GeneratorAccWidth = 16;wire [Baud8GeneratorAccWidth:0]Baud8GeneratorInc = ((Baud8〈<(Baud8GeneratorAccWidth—7))+(ClkFrequency>〉8))/(ClkFrequency>>7);reg [Baud8GeneratorAccWidth:0]Baud8GeneratorAcc;always @(posedge clk or negedge rst)if(~rst)Baud8GeneratorAcc 〈= 0;elseBaud8GeneratorAcc <= Baud8GeneratorAcc[Baud8GeneratorAccWidth—1:0] + Baud8GeneratorInc;// Baud8Tick 为波特率的8倍-115200*8 = 921600wire Baud8Tick = Baud8GeneratorAcc[Baud8GeneratorAccWidth];// next_bit 为波特率-115200always @(posedge clk or negedge rst)if(~rst||(state==0))bit_spacing 〈= 0;else if(Baud8Tick)bit_spacing <= bit_spacing + 1;wire next_bit = (bit_spacing==7);// 检测到RxD 有下跳沿时,RxD_start 置1,准备接收数据always@(posedge clk)if(Baud8Tick)beginRxD_delay 〈= RxD;RxD_start <= (Baud8Tick & RxD_delay & (~RxD));end// 状态机接收数据always@(posedge clk or negedge rst)if(~rst)state 〈= 4’b0000;else if(Baud8Tick)case(state)4'b0000:if(RxD_start)state <= 4’b1000;// 检测到下跳沿4’b1000: if(next_bit)state 〈= 4'b1001;// bit 04'b1001: if(next_bit) state <= 4'b1010;// bit 14’b1010:if(next_bit) state 〈= 4’b1011; // bit 24’b1011: if(next_bit) state <= 4'b1100;// bit 34’b1100: if(next_bit)state 〈= 4'b1101;// bit 44'b1101:if(next_bit)state <= 4’b1110; // bit 54'b1110: if(next_bit) state <= 4'b1111; // bit 64'b1111: if(next_bit) state 〈= 4'b0001; // bit 74'b0001: if(next_bit) state 〈= 4’b0000;// 停止位default: state <= 4'b0000;endcase// 保存接收数据到RxD_data 中always @(posedge clk or negedge rst)if(~rst)RxD_data 〈= 8’b00000000;else if(Baud8Tick &&next_bit && state[3])RxD_data <= {RxD,RxD_data[7:1]};// RxD_data_ready 置位信号always @(posedge clk or negedge rst)if(~rst)RxD_data_ready <= 0;elseRxD_data_ready <= (Baud8Tick && next_bit &&state==4'b0001); endmodule为了测试收发是否正常,写的Test Bench`timescale 1ns / 1nsmodule rs232_test;reg clk,rst,TxD_start;reg [7:0]TxD_data;wire[7:0] RxD_data;wire //RxD,TxD,TxD_busy,RxD_data_ready;trans trans(.clk(clk),。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Verilog串口通信代码module ck(clk,rst_n,rs232_rx,rs232_tx);input clk; // 50MHz主时钟input rst_n; //低电平复位信号input rs232_rx; // RS232接收数据信号output rs232_tx; // RS232发送数据信号wire bps_start; //接收到数据后,波特率时钟启动信号置位wire clk_bps; // clk_bps的高电平为接收或者发送数据位的中间采样点wire[7:0] rx_data; //接收数据寄存器,保存直至下一个数据来到wire rx_int; //接收数据中断信号,接收到数据期间始终为高电平//----------------------------------------------------speed_select speed_select( .clk(clk), //波特率选择模块,接收和发送模块复用,不支持全双工通信.rst_n(rst_n),.bps_start(bps_start),.clk_bps(clk_bps));my_uart_rx my_uart_rx( .clk(clk), //接收数据模块.rst_n(rst_n),.rs232_rx(rs232_rx),.clk_bps(clk_bps),.bps_start(bps_start),.rx_data(rx_data),.rx_int(rx_int));my_uart_tx my_uart_tx( .clk(clk), //发送数据模块.rst_n(rst_n),.clk_bps(clk_bps),.rx_data(rx_data),.rx_int(rx_int),.rs232_tx(rs232_tx),.bps_start(bps_start));endmodulemodule speed_select(clk,rst_n,bps_start,clk_bps);input clk; // 50MHz主时钟input rst_n; //低电平复位信号input bps_start; //接收到数据后,波特率时钟启动信号置位output clk_bps; // clk_bps的高电平为接收或者发送数据位的中间采样点parameter bps9600 = 5207, //波特率为9600bpsbps19200 = 2603, //波特率为19200bpsbps38400 = 1301, //波特率为38400bpsbps57600 = 867, //波特率为57600bpsbps115200 = 433; //波特率为115200bpsparameter bps9600_2 = 2603,bps19200_2 = 1301,bps38400_2 = 650,bps57600_2 = 433,bps115200_2 = 216;reg[12:0] bps_para; //分频计数最大值reg[12:0] bps_para_2; //分频计数的一半reg[12:0] cnt; //分频计数reg clk_bps_r; //波特率时钟寄存器//----------------------------------------------------------reg[2:0] uart_ctrl; // uart波特率选择寄存器,怎样配置uart_ctr??//----------------------------------------------------------always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginuart_ctrl <= 3'd0; //默认波特率为9600bpsendelse begincase (uart_ctrl) //波特率设置3'd0: beginbps_para <= bps9600;bps_para_2 <= bps9600_2;end3'd1: beginbps_para <= bps19200;bps_para_2 <= bps19200_2;end3'd2: beginbps_para <= bps38400;bps_para_2 <= bps38400_2;end3'd3: beginbps_para <= bps57600;bps_para_2 <= bps57600_2;end3'd4: beginbps_para <= bps115200;bps_para_2 <= bps115200_2;enddefault: ;endcaseendendalways @ (posedge clk or negedge rst_n)if(!rst_n) cnt <= 13'd0;else if(cnt<bps_para && bps_start) cnt <= cnt+1'b1; //波特率时钟计数启动else cnt <= 13'd0;always @ (posedge clk or negedge rst_n)if(!rst_n) clk_bps_r <= 1'b0;else if(cnt==bps_para_2 && bps_start) clk_bps_r <= 1'b1; // clk_bps_r高电平为接收或者发送数据位的!中间!采样点else clk_bps_r <= 1'b0;assign clk_bps = clk_bps_r;endmodulemodule my_uart_rx(clk,rst_n,rs232_rx,clk_bps,bps_start,rx_data,rx_int);input clk; // 50MHz主时钟input rst_n; //低电平复位信号input rs232_rx; // RS232接收数据信号!!input clk_bps; // clk_bps的高电平为接收或者发送数据位的中间采样点output bps_start; //接收到数据后,波特率时钟启动信号置位output[7:0] rx_data; //接收数据寄存器,保存直至下一个数据来到output rx_int; //接收数据中断信号,接收到数据期间始终为高电平//----------------------------------------------------------------reg rs232_rx0,rs232_rx1,rs232_rx2; //接收数据寄存器,滤波用wire neg_rs232_rx; //表示数据线接收到下降沿always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginrs232_rx0 <= 1'b1;rs232_rx1 <= 1'b1;rs232_rx2 <= 1'b1;endelse beginrs232_rx0 <= rs232_rx;rs232_rx1 <= rs232_rx0;rs232_rx2 <= rs232_rx1;endendassign neg_rs232_rx = rs232_rx2 & ~rs232_rx1; //接收到下降沿后neg_rs232_rx置高一个时钟周期 ??//----------------------------------------------------------------reg bps_start_r;reg[3:0] num; //移位次数reg rx_int; //接收数据中断信号,接收到数据期间始终为高电平always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginbps_start_r <= 1'bz;rx_int <= 1'b0;endelse if(neg_rs232_rx) beginbps_start_r <= 1'b1; //启动接收数据rx_int <= 1'b1; //接收数据中断信号使能endelse if(num==4'd12) begin //??bps_start_r <= 1'bz; //数据接收完毕rx_int <= 1'b0; //接收数据中断信号关闭endendassign bps_start = bps_start_r;//----------------------------------------------------------------reg[7:0] rx_data_r; //接收数据寄存器,保存直至下一个数据来到//----------------------------------------------------------------reg[7:0] rx_temp_data; //当前接收数据寄存器reg rx_data_shift; //数据移位标志always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginrx_data_shift <= 1'b0;rx_temp_data <= 8'd0;num <= 4'd0;rx_data_r <= 8'd0;endelse if(rx_int) begin //接收数据处理if(clk_bps) begin //读取并保存数据,接收数据为一个起始位,8bit数据,一个结束位 rx_data_shift <= 1'b1;num <= num+1'b1;if(num<=4'd8) rx_temp_data[7] <= rs232_rx; //锁存9bit(1bit起始位,8bit 数据)??如何配置rs232_rxendelse if(rx_data_shift) begin //数据移位处理rx_data_shift <= 1'b0;if(num<=4'd8) rx_temp_data <= rx_temp_data >> 1'b1; //移位8次,第1bit起始位移除,剩下8bit正好是接收数据else if(num==4'd12) beginnum <= 4'd0; //接收到STOP位后结束,num清零rx_data_r <= rx_temp_data; //把数据锁存到数据寄存器rx_data中endendendendassign rx_data = rx_data_r;endmodulemodule my_uart_tx(clk,rst_n,clk_bps,rx_data,rx_int,rs232_tx,bps_start);input clk; // 50MHz主时钟input rst_n; //低电平复位信号input clk_bps; // clk_bps的高电平为接收或者发送数据位的中间采样点input[7:0] rx_data; //接收数据寄存器input rx_int; //接收数据中断信号,接收到数据期间始终为高电平,在次利用它的下降沿来启动发送数据output rs232_tx; // RS232发送数据信号output bps_start; //接收或者要发送数据,波特率时钟启动信号置位//---------------------------------------------------------reg rx_int0,rx_int1,rx_int2; //rx_int信号寄存器,捕捉下降沿滤波用wire neg_rx_int; // rx_int下降沿标志位always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginrx_int0 <= 1'b0;rx_int1 <= 1'b0;rx_int2 <= 1'b0;endelse beginrx_int0 <= rx_int;rx_int1 <= rx_int0;rx_int2 <= rx_int1;endendassign neg_rx_int = ~rx_int1 & rx_int2; //捕捉到下降沿后,neg_rx_int拉地保持一个主时钟周期??//---------------------------------------------------------reg[7:0] tx_data; //待发送数据的寄存器//---------------------------------------------------------reg bps_start_r;reg tx_en; //发送数据使能信号,高有效reg[3:0] num;always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginbps_start_r <= 1'bz;tx_en <= 1'b0;tx_data <= 8'd0;endelse if(neg_rx_int) begin //接收数据完毕,准备把接收到的数据发回去bps_start_r <= 1'b1;tx_data <= rx_data; //把接收到的数据存入发送数据寄存器tx_en <= 1'b1; //进入发送数据状态中endelse if(num==4'd11) begin //数据发送完成,复位bps_start_r <= 1'bz;tx_en <= 1'b0;endendassign bps_start = bps_start_r;//---------------------------------------------------------reg rs232_tx_r;always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginnum <= 4'd0;rs232_tx_r <= 1'b1;endelse if(tx_en) beginif(clk_bps) beginnum <= num+1'b1;case (num)4'd0: rs232_tx_r <= 1'b0; //发送起始位4'd1: rs232_tx_r <= tx_data[0]; //发送bit04'd2: rs232_tx_r <= tx_data[1]; //发送bit14'd3: rs232_tx_r <= tx_data[2]; //发送bit24'd4: rs232_tx_r <= tx_data[3]; //发送bit34'd5: rs232_tx_r <= tx_data[4]; //发送bit44'd6: rs232_tx_r <= tx_data[5]; //发送bit54'd7: rs232_tx_r <= tx_data[6]; //发送bit64'd8: rs232_tx_r <= tx_data[7]; //发送bit74'd9: rs232_tx_r <= 1'b0; //发送结束位default: rs232_tx_r <= 1'b1;endcaseendelse if(num==4'd11) num <= 4'd0; //复位endendassign rs232_tx = rs232_tx_r; //如何配置rs232_tx endmodule。