七段码显示汇编语言程序设计

6位7段数码管时钟显示汇编程序

MOV P0,A

RET

TAB:

DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH

DELAY1MS:MOV R7,#04H;延时程序

D1: MOV R6,#7DH

DJNZ R6,$

DJNZ R7,D1

RET

END

CJNE A,#60H,RETURN

MOV 41H,#00H

MOV A,#01H

ADD A,40H

DA A

MOV 40H,A

CJNE A,#24H,RETURN

\

MOV 40H,#00H

RETURN:

SETB TR0

POP Acc

POP PSW

RETI

SEG:MOV DPTR,#TAB;查表程序

MOVC A,@A+DPTR

6位7段数码管时钟显示汇编程序6位程序汇编显示程序汇编程序七段数码管7段数码管数码管6位7段数码管显示

ORG 0000H

AJMPMAIN

ORG 000BH

AJMP IT0P

ORG 0040H

MAIN:;主程序

MOV P0,#0FFH;数码管初始状态都是8

<

MOV P1,#0FFH;选中所有的数码管

MOV SP,#60H

ACALL SEG

ACALL DELAY1MS

CLR

MINUTEGE: SETB

MOV A,41H

ANL A,#0FH

ACALL SEG

{

ACALL DELAY1MS

CLR

MINUTESHI:SETB

MOV A,41H

SWAP A

ANL A,#0FH

七段数码管显示程序

附录A 八位七段数码管显示程序library ieee;use led isport( clk : in std_logic; --Clock Signaldata_in : in std_logic_vector(7 downto 0); --data busledag : out std_logic_vector(6 downto 0); --定义七位输出信号sel : out std_logic_vector(2 downto 0) --ledag Select);end led;--------------------------------------------------------------------architecture behave of led issignal dcount : std_logic_vector(2 downto 0);signal adh,adl : std_logic_vector(6 downto 0);signal adcount : std_logic_vector(7 downto 0);signal din_h,din_l : std_logic_vector(3 downto 0);signal coclk : std_logic;beginprocess(clk) --out enable signalbeginif(clk'event and clk='1') thenif adcount="" thencoclk<='1';adcount<="00000000";elseadcount<=adcount+1;coclk<='0';end if;end if;end process;process(clk) --rd the adc databeginif(clk'event and clk='1') thendin_h<=data_in(7 downto 4);din_l<=data_in(3 downto 0);end if;end process;process(clk)begincase din_h iswhen "0000"=>adh<="0111111"; --display 0when "0001"=>adh<="0000110"; --display 1when "0010"=>adh<="1011011"; --display 2when "0011"=>adh<="1001111"; --display 3when "0100"=>adh<="1100110"; --display 4when "0101"=>adh<="1101101"; --display 5when "0110"=>adh<="1111101"; --display 6when "0111"=>adh<="0000111"; --display 7when "1001"=>adh<="1101111"; --display 9 when "1010"=>adh<="1110111"; --display a when "1011"=>adh<="1111100"; --display b when "1100"=>adh<="0111001"; --display c when "1101"=>adh<="1011110"; --display d when "1110"=>adh<="1111001"; --display e when "1111"=>adh<="1110001"; --display f when others=>adh<=adh; --no change end case;case din_l iswhen "0000"=>adl<="0111111"; --display 0 when "0001"=>adl<="0000110"; --display 1 when "0010"=>adl<="1011011"; --display 2 when "0011"=>adl<="1001111"; --display 3 when "0100"=>adl<="1100110"; --display 4 when "0101"=>adl<="1101101"; --display 5 when "0110"=>adl<="1111101"; --display 6 when "0111"=>adl<="0000111"; --display 7 when "1000"=>adl<="1111111"; --display 8 when "1001"=>adl<="1101111"; --display 9 when "1010"=>adl<="1110111"; --display a when "1011"=>adl<="1111100"; --display b when "1100"=>adl<="0111001"; --display c when "1101"=>adl<="1011110"; --display dwhen "1111"=>adl<="1110001"; --display fwhen others=>adl<=adl; --no changeend case;end process;process(coclk) --display processbeginif(coclk'event and coclk='1') thendcount<=dcount+1;sel<=dcount;case dcount iswhen "000"=>ledag<="1000000";when "001"=>ledag<="1000000";when "010"=>ledag<="1000000";when "011"=>ledag<=adh;when "100"=>ledag<=adl;when "101"=>ledag<="1000000";when "110"=>ledag<="1000000";when "111"=>ledag<="1000000";when others=>ledag<="0000000";end case;end if;end process;end behave;。

实验13实现七段码显示

显示数字

通过控制不同LED的亮灭, 可以组合显示出0-9的数 字。

显示字母

部分七段数码管还可以显 示一些英文字母,但显示 能力有限。

七段码编码方式

BCD编码

编码表

使用四位二进制数(BCD码)来表示 0-9的数字,每位二进制数对应七段 数码管中的一个LED。

为了方便使用,通常会提供一个七段 数码管的编码表,列出不同数字和字 母对应的编码值。

显示亮度可调

我们还实现了显示亮度的调整功能。通过改变输入信号的电压或电流,可以调 整七段码显示器的亮度,使其在不同的环境下都能保持良好的可读性。

实验结果分析

功能性分析

从实验结果来看,七段码显示器能够准确地显示数字和字符,且显示亮度可调, 满足了实验的基本要求。

性能评估

在实验过程中,我们对七段码显示器的性能进行了评估。结果显示,该显示器具 有较高的亮度和对比度,以及较快的响应速度,能够满足大多数应用场景的需求 。

02 七段码显示原理

七段码定义

七段数码管

一种电子显示器件,由七个发光二 极管(LED)组成,可以显示数字 和部分英文字母。

共阳极和共阴极

七段数码管有共阳极和共阴极两 种类型,共阳极数码管的阳极连 接在一起,共阴极数码管的阴极 连接在一起。

七段码显示原理

01

02

03

发光原理

当七段数码管的某个LED 两端加上合适的电压时, 该LED就会发光。

七段数码管原理

七段数码管是一种电子显示器件,由七个发光二极管组成, 可以显示数字和部分英文字母。通过控制不同发光二极管 的亮灭,可以组合成不同的字形。

七段码编码方式

七段数码管的编码方式有多种,如共阳极和共阴极等。不 同编码方式的七段数码管需要不同的驱动电路和控制程序。

七段码电子表显示程序(2021整理)

目录1.题目及要求``````````````````````````````````````````22.功能设计`````````````````````````````````````````````23.详细设计`````````````````````````````````````````````23.1设计方法``````````````````````````````````````````````````````````23.2流程图`````````````````````````````````````````````````````````````23. 3重点,难点``````````````````````````````````````````````````````6 4.总结心得体会```````````````````````````````````````````7 5.参考文献````````````````````````````````````````````````7 6.附:源程序```````````````````````````````````````````````71.题目及要求1.1题目:七段码电子表显示程序1.2要求1.七段码电子表显示程序2.菜单项选择择:设置时,分,秒,开始,退出等3.模拟七段码管显示时,分,秒4.要求界面美2.功能设计说明:esc键退出s键设置时间数据段〔1〕Disptime , showtime 显示时钟〔2〕定义定义0-9十个图形数字,以便模拟七段码显示时钟宏定义〔1〕Clear定义清屏宏〔2〕rowcol 定义光标定位宏〔3〕crlf 回车换行宏〔4〕display显示字符串宏〔5〕change 计算时间宏函数(1)main 主函数(2)play 主要完成显示七段码电子表显示(3)prog0 到prog10完成七段码到一般显示的转换〔4〕moveshape 显示七段码电子表(4)delay 延迟函数(5)exit 返回DOS函数3.设计详细3.1设计方法〔1〕Clears清屏宏用到了BIOS中断06H。

十六进制7段数码显示译码器设计

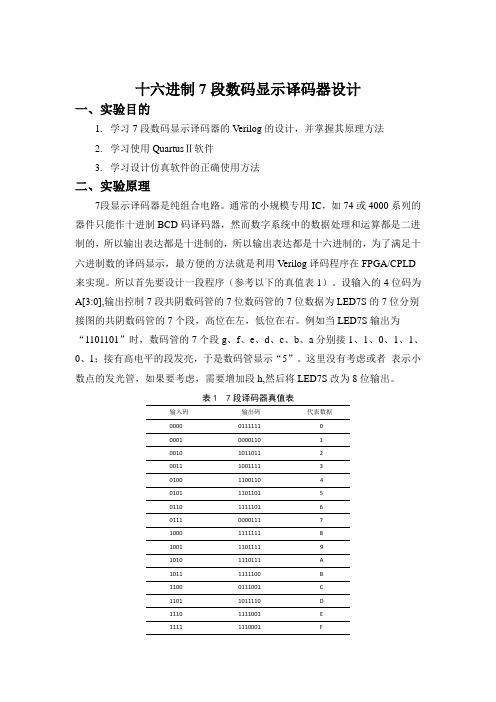

十六进制7段数码显示译码器设计一、实验目的1.学习7段数码显示译码器的Verilog的设计,并掌握其原理方法2.学习使用QuartusⅡ软件3.学习设计仿真软件的正确使用方法二、实验原理7段显示译码器是纯组合电路。

通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码器,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用Verilog译码程序在FPGA/CPLD 来实现。

所以首先要设计一段程序(参考以下的真值表1)。

设输入的4位码为A[3:0],输出控制7段共阴数码管的7位数码管的7位数据为LED7S的7位分别接图的共阴数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。

这里没有考虑或者表示小数点的发光管,如果要考虑,需要增加段h,然后将LED7S改为8位输出。

表1 7段译码器真值表输入码输出码代表数据0000 0111111 00001 0000110 10010 1011011 20011 1001111 30100 1100110 40101 1101101 50110 1111101 60111 0000111 71000 1111111 81001 1101111 91010 1110111 A1011 1111100 B1100 0111001 C1101 1011110 D1110 1111001 E1111 1110001 F三、实验任务将设计好的Verilog译码器程序在QuartusⅡ上进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

四、实验步骤1.新建一个文件夹DECL_DEMO,然后选择File,点击new,再打开Verilog HDL File文件类型。

七段码电子表显示程序

攀枝花学院学生课程设计(论文)题目:七段码电子表显示程序学生姓名:文理学号: 201010801068 所在院(系):计算机学院专业:计算机科学与技术班级: 2010级计本2班第二组指导教师:李艳华职称:讲师2011 年12 月31 日攀枝花学院本科学生课程设计任务书题目七段码电子表显示程序1、课程设计的目的通过本课程设计教学所要达到的目的是:1、培养学生理论联系实际的设计思想,提高学生综合运用汇编语言课程的理论知分析问题、解决问题的能力。

2、通过查找、运用设计资料,完成工程设计所必备的基本训练。

3、使同学们更深入的了解计算机系统内部的有关知识,为以后的学习和系统开发奠定良好的基础。

2、课程设计的内容和要求(包括原始数据、技术要求、工作要求等)设计内容:用电子表的形式显示系统时间。

以“时:分:秒”的形式显示时间。

设计思路:数字0~9中的每一个数字用“|”和“—”字符组成的“七段”码图形表示,时与分、分与秒之间的两点用“▼”字符表示。

这些字符预先定义在数据段的字符图形里,利用BIOS INT 1AH的2号系统功能调用,读出计算机系统的时间(为BCD码),置换成字符图形标中的图形字符显示。

本程序设计的关键是随着系统时间的变化,用字符组成的图形数字如何进行相应的变化。

方法是:不停地读取系统时间并保存在寄存器中,将每次取出的时间显示并与前一次比较,先比较“秒”值,在不同的情况下(系统时间发生了增1的变化),则调用相应的图形字符显示,在不超过60秒的情况下,重复比较秒,然后再比较和显示“分”值与“小时”值。

3、主要参考文献[1]《汇编语言程序设计》,吴向军等,高等教育出版社,2002[2]《IBM-PC汇编语言及程序设计》(第2版), 沈美明等,清华大学出版社,2001[3]《IBM-PC汇编语言及程序设计实验教程》,沈美明等,清华大学出版社,2001[4]《汇编语言程序设计》, 钱晓捷等,电子工业出版社,2000[5]《汇编语言程序设计》, 张志明等,重庆大学出版社,19974、课程设计工作进度计划时间(天)内容安排1 分析设计准备3 编程调试阶段1 编写课程设计报告指导教师(签字)日期年月日教研室意见:年月日学生(签字):接受任务时间:年月日课程设计(论文)指导教师成绩评定表题目名称七段码电子表显示程序评分项目分值得分评价内涵工作表现20% 01 学习态度 6 遵守各项纪律,工作刻苦努力,具有良好的科学工作态度。

十六进制七段数码显示译码器

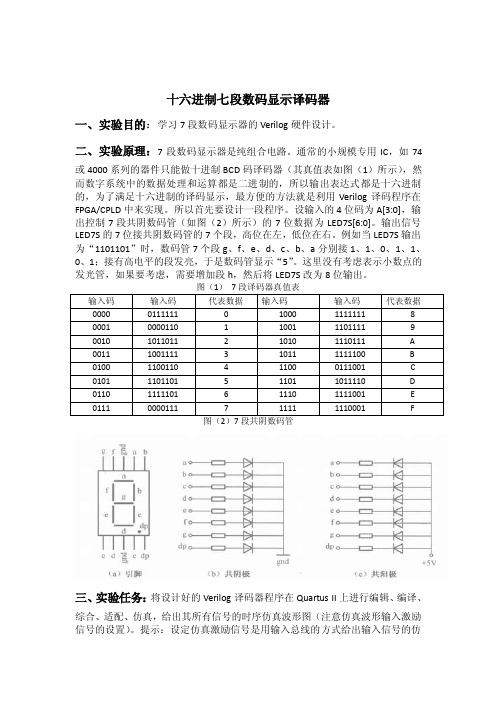

十六进制七段数码显示译码器一、实验目的:学习7段数码显示器的Verilog硬件设计。

二、实验原理:7段数码显示器是纯组合电路。

通常的小规模专用IC,如74或4000系列的器件只能做十进制BCD码译码器(其真值表如图(1)所示),然而数字系统中的数据处理和运算都是二进制的,所以输出表达式都是十六进制的,为了满足十六进制的译码显示,最方便的方法就是利用Verilog译码程序在FPGA/CPLD中来实现。

所以首先要设计一段程序。

设输入的4位码为A[3:0],输出控制7段共阴数码管(如图(2)所示)的7位数据为LED7S[6:0]。

输出信号LED7S的7位接共阴数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管7个段g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。

这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,然后将LED7S改为8位输出。

图(1)7段译码器真值表图(2)7段共阴数码管三、实验任务:将设计好的Verilog译码器程序在Quartus II上进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形图(注意仿真波形输入激励信号的设置)。

提示:设定仿真激励信号是用输入总线的方式给出输入信号的仿真数据。

四、实验步骤:(一)、建立工作库文件和编辑设计文文件任何一项设计都是一项Project(工程),而把一个工程下的所有文件放在一个文件夹内是一个非常好的习惯,以便于我们整理,利用和提取不同工程下的文件,而此文件夹将被EDA软件默认为Work Library(工作库),所以第一步先根据自己的习惯,建立个新的文件夹。

(1)新建文件夹:我的习惯在D盘建立并保存工程,我将文件夹取名Test,(2)输入源程序:打开Quartus II,选择菜单File-->New-->Design Files-->VerilogHDL File-->OK(如图1所示)代码如下:module DECL7S(A,LED7S);input[3:0] A;output[6:0] LED7S;reg[6:0] LED7S;always@(A )case(A)4'b0000 :LED7S<=7'b0111111;4'b0001 :LED7S<=7'b0000110;4'b0010 :LED7S<=7'b1011011;4'b0011 :LED7S<=7'b1001111;4'b0100 :LED7S<=7'b1100110;4'b0101 :LED7S<=7'b1101101;4'b0110 :LED7S<=7'b1111101;4'b0111 :LED7S<=7'b0000111;4'b1000 :LED7S<=7'b1111111;4'b1001 :LED7S<=7'b1101111;4'b1010 :LED7S<=7'b1110111;4'b1011 :LED7S<=7'b1111100;4'b1100 :LED7S<=7'b0111001;4'b1101 :LED7S<=7'b1011110;4'b1110 :LED7S<=7'b1111001;4'b1111 :LED7S<=7'b1110001;default :LED7S<=7'b0111111;endcaseendmodule(3)保存文件:完成一步就保存一步是一个好习惯,这样即使出现意外情况,也不至于以前的努力付诸东流。

十六进制7段数码显示译码器设计实验报告

实验名称:十六进制7段数码显示译码器设计实验目的:1.设计七段显示译码器2.学习Verilog HDL文本文件进行逻辑设计输入;3.学习设计仿真工具的使用方法;工作原理:7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

例如6-18作为7段译码器,输出信号LED7S 的7位分别接图6-17数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段g,f,e,d,c,b,a分别接1,1,0,1,1,0,1;接有高电平的段发亮,于是数码管显示“5”。

注意,这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,例6-18中的LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)应改为…(7 DOWNTO 0)。

实验内容1:将设计好的VHDL译码器程序在Quartus II上进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

实验步骤:步骤1:新建一个文件夹击打开vhdl文件;步骤2:编写源程序并保存步骤3:新建一个工程及进行工程设置步骤4:调试程序至无误;步骤5:接着新建一个VECTOR WAVEFOM文件及展出仿真波形设置步骤6:输入数据并输出结果(时序仿真图)步骤7:设置好这个模式步骤8:生成RTL原理图步骤9:引脚锁定及源代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DECL7S ISPORT(A :IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END;ARCHITECTURE one OF DECL7S ISBEGINPROCESS(A)BEGINCASE A ISWHEN"0000"=> LED7S<="0111111";WHEN"0001"=> LED7S<="0000110";WHEN"0010"=> LED7S<="1011011";WHEN"0011"=> LED7S<="1001111";WHEN"0100"=> LED7S<="1100110";WHEN"0101"=> LED7S<="1101101";WHEN"0110"=> LED7S<="1111101";WHEN"0111"=> LED7S<="0000111";WHEN"1000"=> LED7S<="1111111";WHEN"1001"=> LED7S<="1101111";WHEN"1010"=> LED7S<="1110111";WHEN"1011"=> LED7S<="1111100";WHEN"1100"=> LED7S<="0111001";WHEN"1101"=> LED7S<="1011110";WHEN"1110"=> LED7S<="1111001";WHEN"1111"=> LED7S<="1110001";WHEN OTHERS =>NULL;END CASE;END PROCESS;END;实验内容二:1、硬件测试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计任务书学生姓名专业班级指导教师黄珍工作单位自动化学院课程设计题目七段码显示汇编语言程序设计初始条件:采用16位微处理器8086 CPU以及86系列微型计算机的指令系统;软件设计平台为多功能微型计算机实验软件MFS中的微机原理实验集成环境MF2KP。

要求完成的主要任务:设计汇编语言程序,实现七段码显示效果,具体功能要求如下:(1)数字0~9或A~F中的每个数字、字母用“¦”和“—”字符组成的“七段”码图形表示;(2)运行程序后,要求数字0~9或字母A~F依次循环显示;(3)单击“Q”或“q”键退出程序。

根据功能要求绘制程序流程图、编写完整的汇编语言程序并上机调试:撰写课程设计说明书。

课程设计说明书的撰写格式如下:(1)设计说明书包括封面、任务书(指导老师提供)、正文、参考文献(3~5篇)、附录(程序清单,要求有注释)、成绩评定表(指导老师提供)。

(2)说明书正文包含总体方案论证(算法说明);程序流程图设计及其说明;软件设计关键问题或程序段落的说明;程序调试说明、结果记录及分析;课程设计收获及心得体会。

(3)同一选题若为合作完成,设计说明书中需注明本人承担的设计部分。

(本次课程设计时间:2011年1月10日-21日,历时两周)指导教师签名:年月日系主任(或责任教师)签名:年月日目录1 总体方案论证 (1)1.1 七段数码管显示功能分析 (1)1.2 算法说明 (1)2 程序流程图设计及其说明 (3)2.1 程序流程图 (3)2.2 程序流程图说明 (4)3程序段落的说明 (5)3.1 数据段定义 (5)3.2 程序初始化 (5)3.3 清空显示屏 (5)3.4 重置光标 (6)3.5 数码显示处理工作 (6)3.6 取得计数并为下次循环准备 (6)3.7 一个数字的数码管显示 (6)3.8 显示程序 (7)3.9 程序延时部分 (7)3.10 判断键盘输入部分 (7)3.11 结束DOS以及跳出语句 (8)4 程序调试说明、结果记录及分析 (9)5 课程设计收获及心得体会 (13)参考文献 (14)附录 (15)七段码显示汇编语言程序设计1 总体方案论证1.1 七段数码管显示功能分析双击进入程序,运行显示DOS 界面。

屏幕上出现提示“if you want to quit,please press 'q' or 'Q'!”字样。

同时模拟七段数码管循环显示数字从F 依次到0。

若在键盘输入'q' or 'Q'则退出该程序,如果输入的为其他符号或者没有输入则程序继续运行。

1.2 算法说明由于程序需要在DOS 界面上显示七段数码管,所以要模拟七段数码管。

在数据定义的时候要给予定义。

七段码显示器字形与代码的对应关系如下:本程序采用的是向左循环,根据标识符CF 是1或者是0来判断是否开启相对应的模拟数码管,故表1-1中代码(B )代码为高七位有效。

由于本程序需要循环显示数字F-0,所以数据段定义的七段码的数字为0fch,60h,0dah,0f2h,66h,0b6h,0Beh,0e0h,0feh,0f6h,0EEH,3EH,9CH,7AH,9EH,8EH (0-F )。

然后程序循环显示每一位数字,从所赋初值开始,以此减1循环显示,循环的同时检测键盘是否有输入,如果有输入则与'q'和'Q'相比较,如果输入的是这两个则结束循环,否则循环继续。

每次循环中调用延时子程序来达到调节数码管刷新的频率。

12 34567表1-1七段码显示字形与代码的对应关系2 程序流程图设计及其说明2.1 程序流程图A图2-1 程序流程图2.2 程序流程图说明从程序流程图可以看出,程序一旦开始运行就不会自动停止,需要人工输入“Q”或者“q”来终止程序。

程序分为如下部分:七段码数据定义部分;循环显示数字部分;显示每一个数字部分;延时部分;判断键盘输入部分。

七段码数据定义部分:由于程序需要在DOS界面上显示七段数码管,所以要模拟七段数码管。

故刚开始定义模拟数码管,并规定好每段数码管的偏移量。

循环显示数字部分:初始赋予起始循环数字,并清屏,定义光标,根据循环数字逐一显示。

当循环数字小于0时返回至初始值,继续循环。

显示每一个数字部分:根据定义的代码,采用做循环左移指令,根据CF位来选择对应数码管段,开启则继续保留,关闭则用空格填充。

延时部分:利用LOOP循环指令,延时为总循环次数*系统执行一条指令时间。

判断键盘输入部分:根据键盘是否有输入以及输入的是否为“Q”或者“q”来终止程序,否则继续循环。

3程序段落的说明3.1 数据段定义DATA SEGMENTBUFF DB ' -- ',0AH,0DH,35DUP( )DB '| |',0AH,0DH,35DUP( )DB ' -- ',0AH,0DH,35DUP( )DB '| |',0AH,0DH,35DUP( )DB ' -- ',0AH,0DH,35DUP( ),24HMEM DB207DUP(?)VAL DB1,43,125,165,123,41,83TAB DB0fch, 60h, 0dah, 0f2h, 66h, 0b6h, 0Beh, 0e0h, 0feh, 0f6h, 0EEH, 3EH, 9CH, 7AH, 9EH, 8EHMESSAGE DB 'If you want to quit,please press ''q'' or ' 'Q''!' ,0AH,0DH,0AH,0DH, 35DUP( ),24HNUMBER DB ?DATA ENDS在数据定义段,BUFF定义了模拟七段数码管的显示,其中35 dup ( )是将七段数码管显示在了屏幕中间。

同时给为BUFF开辟空间MEM,开辟此空间让每次显示不至于破坏BUFF数据。

同时定义VAL为每段数码管在BUFF里面的偏移量,TAB为0-F的每一位数字的七段数码管显示编码,以及循环显示的数字个数即起始显示数字NUMBER。

MESSAGE为定义系统提示退出的信息。

3.2 程序初始化CODE SEGMENTASSUME DS:DATA ,CS:CODE ,ES:DATASTART:MOV AX,DATAMOV DS,AXMOV ES,AXDS和ES对应于数据段DATA,CS对应于代码段CODE,并将DATA的地址赋予DS和ES。

3.3 清空显示屏A1:MOV AH,06HMOV AL,0MOV BH,7MOV CX,0MOV DX,986FHINT10H采用BIOS中断INT 10H的06H功能,AH=06H是向上滚屏,AL是滚动行数,当AL=0时是清屏,BH是空白区域的缺省属性,(CH、CL)是窗口的左上角位置(Y 坐标,X坐标),(DH、DL)是窗口的右下角位置(Y坐标,X坐标)3.4 重置光标MOV AH,02HMOV BH,0MOV DX,610HINT10H采用BIOS中断INT 10H的02H功能,用文本坐标下设置光标位置。

BH为显示页码数,DH是行(Y坐标),DL是列(X坐标)。

3.5 数码显示处理工作LEA SI,BUFFLEA DI,MEMCLDMOV CX,207REP MOVSB将BUFF的内容传至MEM中,开辟此空间让每次显示不至于破坏BUFF数据。

用CLD使DF=0,当DF=0时地址往增加方向移动。

3.6 取得计数并为下次循环准备MOV BL,NUMBERMOV AL,TAB[BX]CMP BL,0JL ROUNDDEC BLMOV NUMBER,BL取得初始计数NUMBER以及其在定义的数据段TAB中的数码编码。

判断NUMBER 数值是否小于0,如果小于0则跳转到程序的开头ROUND重新为NUMBER赋值,如果NUMBER不小于0则将NUMBER减1后的数值赋给NUMBER作为下次循环的初值。

3.7 一个数字的数码管显示LEA DI,VALMOV CX,7B1:ROL AL,1JC B2MOV BL,[DI]MOV SI,BXMOV MEM[SI],20HMOV MEM[SI+1],20HB2:INC DILOOP B1为CX赋值7,因为每个七段数码管有7个部分要显示,将数字的数码编码每一位循环左移到CF中,然后判断CF,如果是1则跳转到B2(该段数码管显示),如果是0则继续执行下面的程序,由于每个数码管占两个字节所以用20h (空格)填充MEM[SI]跟MEM[SI+1]以完成原字符的模拟。

3.8 显示程序MOV AH,09HMOV DX,SEG MESSAGEMOV DS,DXMOV DX,OFFSET MESSAGEINT21HMOV AH,09HMOV DX,OFFSET MEMINT21H调用DOS的09H号功能输出字符,显示所需要输出的字符。

首先输出数据段定义的系统提示信息。

然后由于数字数码管模拟部分已经存储在MEM中,所以显示MEM的内容就是显示的是该数字的数码管模拟。

3.9 程序延时部分PUSH CXPUSH DXMOV DX,10000C1:MOV CX,65500C2:LOOP C2DEC DXJNZ C1POP DXPOP CX利用LOOP循环来延时,延时时间为10000*65500*系统执行一条指令时间3.10 判断键盘输入部分D1:MOV AH,0BHINT21HCMP AL,0JNZ D2JMP A1D2:MOV AH,08HINT21HCMP AL,'Q'JZ EXITCMP AL,'q'JZ EXITJMP A1D1调用DOS的第0BH号功能,判断AL中的数值,如果为00H则有输入跳转D2判断输入的字符,如果为0FFH则直接跳转到AL循环执行下一个数字的显示。

D2调用DOS的第08H号功能,判断AL中的是否为“Q”或者“q”,如果是两者中的一个则调转到EXIT结束DOS以及跳出语句。

如果不是则跳转到A1显示下一个数字。

3.11 结束DOS以及跳出语句EXIT:MOV AX,4C00HINT21HCODE ENDSEND START程序至此结束。

4 程序调试说明、结果记录及分析运行程序结果倒数从F到0如下列截图4-1到4-16所示:F:图4-1显示结果FE:图4-2显示结果ED:图4-3显示结果DC:图4-4显示结果CB:图4-5显示结果B A:图4-6显示结果A 9:图4-7显示结果9 8:图4-8显示结果8 7:图4-9显示结果76:图4-10显示结果6 5:图4-11显示结果5 4:图4-12显示结果4 3:图4-13显示结果3 2:图4-14显示结果21:图4-15显示结果10:图4-16显示结果0 在程序运行的任何时候按“Q”或者“q”程序退出。