基于ECP3的视频采集系统硬件设计

基于CPLD+Cortex-M3的视频采集控制系统的设计

i e c n o p we o s mp i f in y a d lw o rc n u t n, n ie h ic s in i ealte s f r n a d r e in a d t e i lme t t n s h me h c o a d gv st e d s u so n d t i h ot ea d h r wa ed s n mp e n ai c e .T e wa g h o

文采用 了比较常用 的 C D传感器 , S A 1 1 C 而 A 7 1A则是一 款功能

强大的模拟前端 和数字视 频译 码器 , 常应 用在嵌 入式视频 应用 的高度集成 的电路 中 。 由各 种 主要部 件连 接 之后 得到 视频 采集控制系统外部结构 图( 如图 1所示 ) 。

万 智 萍

( 山大 学 新 华 学 院 中 广东 广州 502 ) 15 0

摘 要

提 出一种 C L P D和 C r xM3相配合 的视 频采集控制 系统 的设计方 法。以 A My o e- t R 7中的 C r xM o e— 3作 为 C L t P D控制芯 片,

使用 E M 1 8作为主控芯 片, P 72 对视 频解码芯 片 S A 1 1 A 7 1 A进行 视频数据采集 , 有适应性和灵活 性。介绍 一种 高效率 、 功耗 的视 具 低 频采 集控制系统 , 详细论述 了软硬 件 的设计和实现方案 。采用 V L语言编程 的仿 真结果 表明 了该系统在高速下 的顺利运行 。 HD

DE I D o S GN oF VI E DAT QUI I I oN RoL S S E A AC S T oN C T Y T M

BAS ED oN CPLD +Co t x. 3 re M

基于DSP的视频采集及网络传输模块的设计的开题报告

基于DSP的视频采集及网络传输模块的设计的开题报告题目:基于DSP的视频采集及网络传输模块的设计设计背景及意义:随着互联网的不断发展,视频技术越来越受到人们的关注。

在当前工业自动化、医疗影像等领域,视频技术也被广泛应用。

如何设计出高效、稳定的视频采集及网络传输模块,成为了当前研究的主要问题之一。

本文将基于DSP技术,设计出一种高性能的视频采集及网络传输模块,为实现视频技术的高效应用提供技术支持。

研究内容:本文将主要研究基于DSP的视频采集及网络传输模块的设计,包括以下内容:1. 硬件设计:设计视频采集卡和网络传输卡,包括视频输入芯片、视频预处理芯片、DSP芯片、网络传输芯片等,完成视频信号的采集和传输。

2. 软件设计:通过DSP的编程实现视频信号的预处理和压缩,并通过网络传输芯片将经压缩的视频信号传输到远程服务器端。

3. 系统测试:对设计的视频采集及网络传输模块进行测试验证,测试包括视频输入的稳定性、视频信号压缩比、网络传输性能等。

预期成果:本文设计的基于DSP的视频采集及网络传输模块具备以下特点:1. 采用高效的视频压缩算法,实现视频信号的高质量传输。

2. 可以实现多种视频输入接口,具有高度的兼容性。

3. 设计简单、易于实现。

4. 实现了远程控制和管理功能,可应用于各种工业应用中。

论文结构:本文将按照以下结构撰写:1. 绪论:阐述研究背景、意义、国内外研究现状及研究内容和方法。

2. 硬件设计:详细介绍视频采集卡和网络传输卡的设计。

3. 软件设计:分析视频信号预处理和压缩的算法设计,详细介绍系统软件的设计和实现。

4. 系统测试:对设计的视频采集及网络传输模块进行测试验证。

5. 结论:总结本文研究成果,提出未来的研究方向。

基于TMS320DM6467的视频采集系统设计

基于TMS320DM6467的视频采集系统设计文武;吴勇;张杰【期刊名称】《电视技术》【年(卷),期】2011(35)17【摘要】采用TI公司的达芬奇系列数字媒体处理器DM6467为平台,利用TVP5158译码器实现了一种8路实时视频采集系统.完成了接口电路设计,开发了多通道视频端口和基于V4L2的DaVinci视频接口驱动程序,最后通过VPIF接口将采集到的视频帧送入LCD显示设备进行显示.%An 8 channel real-time video capture system with TVP5158 decoder is implemented. Davinci DM6467 digital media processor of TI company is used as platform. The design of the interface circuit is accomplished. The development of multi-channel video port drivers is completed, as well as the DaVinci video interface drivers based on V4L2. Finally, the video frame is sended into LCD display device through the VPIF interface.【总页数】3页(P39-41)【作者】文武;吴勇;张杰【作者单位】重庆邮电大学重庆信科设计有限公司,重庆401121;重庆邮电大学通信新技术应用研究所,重庆400065;重庆邮电大学重庆信科设计有限公司,重庆401121【正文语种】中文【中图分类】TN911;TP319【相关文献】1.基于TMS320DM6467的机车视频监控系统设计 [J], 张伟;贺德强;苗剑;刘德昌;叶碧碧2.基于TMS320DM6467的红外图像超分辨率重构系统设计 [J], 王东阳;3.基于Android的视频采集与传输系统设计与研究 [J], 张建平4.基于FPGA的高清HD-SDI视频采集系统设计与实现 [J], 钱宏文;刘会;付强;王毅5.基于STM32的WI-FI视频采集与传输系统设计 [J], 林开司;张露因版权原因,仅展示原文概要,查看原文内容请购买。

基于TMS320DM368的高清视频采集系统设计与实现

基于TMS320DM368的高清视频采集系统设计与实现王帅;刘峰【期刊名称】《电视技术》【年(卷),期】2013(37)7【摘要】实现了基于TMS320DM368嵌入式处理器的高清视频采集系统,详细介绍了系统的总体架构及主要的软硬件模块.首先,分析了核心处理模块性能及硬件采集模块功能;其次,描述了高清视频采集、处理及传输等模块的软件实现流程,给出了在嵌入式Linux平台下基于Web服务器移植的实现过程;最后,对系统进行测试,结果表明本系统达到了预期的高清视频采集及传输功能,图像清晰度高,实时性好,可以很方便地应用在需要高清视频监视的场合.%Design and implementation of high-definition video capture system based on TMS320DM368 embedded processor are introduced in this paper. The overall architecture of the system, hardware and software modules are described. First of all, the core processing module performance and hardware acquisition module are introduced. Secondly, the high-definition video capture, processing and transmission module of the software implementation process are analyzed, and then the principle of how to port web server with the embedded Linux platform is given. Finally, the results show that the system has good real-time performance and high-definition clarity.【总页数】4页(P43-45,67)【作者】王帅;刘峰【作者单位】南京邮电大学图像处理与图像通信江苏省重点实验室,江苏南京210003;南京邮电大学图像处理与图像通信江苏省重点实验室,江苏南京210003【正文语种】中文【中图分类】TP277【相关文献】1.基于TMS320DM368的高清视频数据采集处理 [J], 刘超;赵敏2.基于TMS320DM368的高清显微镜系统设计 [J], 孙佳哲;王磊3.基于FPGA和DSP的机载高清VGA视频采集系统设计与实现 [J], 贺敬4.基于TMS320DM368的高清视频传输系统设计和实现 [J], 范宇龙;杨鸣;章湖;蒋金涛;吴正管5.基于FPGA的高清HD-SDI视频采集系统设计与实现 [J], 钱宏文;刘会;付强;王毅因版权原因,仅展示原文概要,查看原文内容请购买。

基于TMS320DM643的视频采集与输出系统的设计与实现

( u a al yPoe s n l e h oo yC lg ,h z o 4 0 ,hn ) H n nR i rfs i a T c n lg ol eZ u h u 1 0 1C i wa o e 2 a

p o u e y T o a y n u l e f ie c u s in s se c mb n dwi VP 0 r d c db I mp n . dweb i as t d oa q i t y t m o i e t T 5 ・ C a d ov io h 1 5

所 示 TS 2 D6 3 M 3 0 M 4 X介绍 TS 2D 6 3 M 30M 4 X是 T I公司 是 C 00系 列中 的支持 达芬 奇技 术 60 的 数字 媒体 处 理器 ,具 有视 频优 化 的可编 程 TS 2C 4+D P内 M 306 x' S M 核 以及 视频 、存 储器 和 网络 接 口,可 以为联 网视频 和 视觉 应用 提 供 最为 灵活 且经 济 高效 的解 决方 案 。该芯 片具 有 8 K I 、3 K 0 BLD 2B LP高速 缓存 / RM和 18B L I SA 2K 2高速缓 存 SA R M存储 器 ,2个 3 2 位 、 13H 3M z外部 存储器 接 口 (MF ,1/ 0 E I) 0 10以太 网媒 体接入 控 制 器 ( A ) 个 U R 、主 机接 口 ( P ) 2 、S I P O 多 M C 、2 AT H I ,IC P 、G I 、

、

通 道音 频 串行 端 口 M A P和 3个 P M cS w。 现 已推 出 的 D 6 3 处 理器 包括 T s 2 D 6 3 / 4 5 6 3 / M 4X M 3 0 M 4 7 6 3 / 4 3

采集器硬件设计内容

电量采集终端硬件电路设计1 CPU电路设计1.1 概述CPU电路主要包括供电电路,晶振电路,复位电路及JTAG电路组成。

具体电路见图1-1。

图1-1 CPU电路1.2 系统的供电电路STR711FR0处理器需要两路电源供电,一路3.3V,一路1.8V。

其中3.3V的电源供给V33:外部主电源V33IOPLL:数字I/O电路和PLL电路的3.3V参考电源 VDDAD:A/D转换器的参考电压1.8V的电源则供给V18:处理器内核电源本电路中的外部3.3V电源是通过电源板提供的VCC(5V)电源经过线性稳压器LM1117-3.3(U6)获得,具体的电路见图1-1左下角,其中U6为线性稳压芯片,而C22和E3则是为了确保LM1117输出的稳定性。

由于STR711FR0内部集成了1.8V的电源稳压器,所以并不需要再增加额外的1.8V的线性稳压器,只需要在V18引脚处外接100nF的退藕电容即可。

为了减低电源上的纹波对整个系统的影响,需要在所有电源的引脚处并接100nF的退藕电容。

(具体可以参照图1-1)。

注意:1.在正常操作模式下V18与V18BKP短接,在Standby模式下V18域与V18BKP域断开。

2.V18引脚不能连接到外部1.8V电源。

1.3 时钟电路STR711FR0为选择主时钟和外围时钟提供了灵活的方式,芯片有3个时钟源:1. PRCCU产生供给CPU和芯片外围的内部时钟。

PRCCU可以由外部的脉冲产生器驱动,连接到CK引脚上面。

2. 32KHZ晶振的实时时钟连接到内部的CK_AF信号上,并且当需要低功率操作时可以选择这个时钟源。

3. 如果需要连接USB特性的设备时需要USB时钟源。

1.3.1 时钟控制单元STR71X时钟控制单元必须由连接到CK引脚上的晶体振荡器驱动,此振荡器最高频率为频率16MHZ,它产生的时钟信号供给CPU和芯片外围电路。

倍频和分频因子使得输入频率有更多的选择范围,然而,更加注意的是推荐频率的限制。

基于ECP3的视频采集系统硬件设计

基于ECP3的视频采集系统硬件设计摘要:本文介绍了基于FPGA芯片ECP3-70的视频采集系统硬件设计。

CMOS传感器MT9P031与FPGA芯片ECP3-70的BANK0连接,进行视频采集。

采集到的视频数据通过千兆以太网物理层芯片88E1118R上传至服务器。

关键词:ECP3-70 MT9P031 88E1118R目前视频采集系统种类非常多,各有各的用途[1]。

本文设计一种用较少芯片构成的、体积小型化,用于狭窄空间的高清视频采集传输系统。

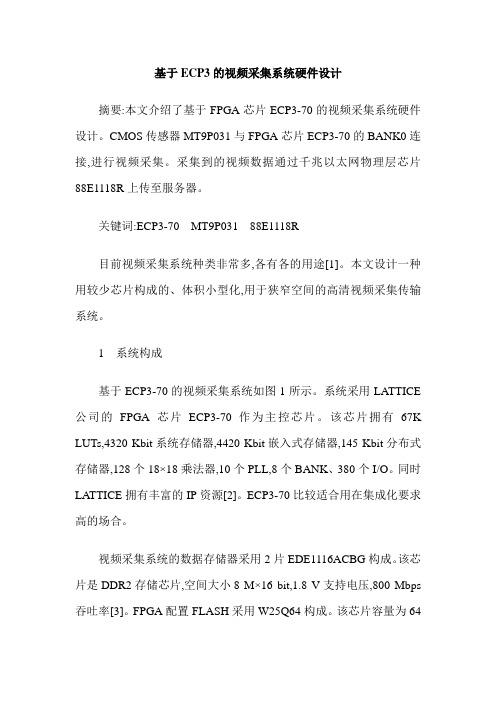

1 系统构成基于ECP3-70的视频采集系统如图1所示。

系统采用LATTICE 公司的FPGA芯片ECP3-70作为主控芯片。

该芯片拥有67K LUTs,4320 Kbit系统存储器,4420 Kbit嵌入式存储器,145 Kbit分布式存储器,128个18×18乘法器,10个PLL,8个BANK、380个I/O。

同时LATTICE拥有丰富的IP资源[2]。

ECP3-70比较适合用在集成化要求高的场合。

视频采集系统的数据存储器采用2片EDE1116ACBG构成。

该芯片是DDR2存储芯片,空间大小8 M×16 bit,1.8 V支持电压,800 Mbps 吞吐率[3]。

FPGA配置FLASH采用W25Q64构成。

该芯片容量为64Mbit,SPI接口,2.7~3.6 V电源电压[4]。

关键数据保存的EEPROM采用AT93C65构成,容量为4 Kbit,三线串行接口,2M时钟速率,2.7~5.5 V电源电压[5]。

系统的工作过程如图1所示。

系统上电,ECP3-70从W25Q64中读取程序数据码流,启动自身按程序工作。

ECP3-70通过I2C接口配置CMOS传感器MT9P031,控制MT9P031获取视频数字信号。

采集到的视频数据通过ECP3-70的I/O口获取,按乒乓存储结构存放在EDE1116ACGB中。

ECP3-70从AT93C56中读取视频配置信息,配置从存储器中读出的原始视频数字信号。

基于CPLDCortex-M3的视频采集控制系统的设计

基于CPLDCortex-M3的视频采集控制系统的设计

万智萍

【期刊名称】《计算机应用与软件》

【年(卷),期】2012(000)010

【摘要】10.3969/j.issn.1000-386x.2012.10.057% 提出一种CPLD和Cortex-M3相配合的视频采集控制系统的设计方法。

以ARMv7中的Cortex-M3作为CPLD控制芯片,使用EPM7128作为主控芯片,对视频解码芯片

SAA7111A进行视频数据采集,具有适应性和灵活性。

介绍一种高效率、低功耗的视频采集控制系统,详细论述了软硬件的设计和实现方案。

采用VHDL语言编程的仿真结果表明了该系统在高速下的顺利运行。

【总页数】4页(P219-221,286)

【作者】万智萍

【作者单位】中山大学新华学院广东广州510520

【正文语种】中文

【中图分类】TP311

【相关文献】

1.基于Linux的嵌入式远程视频采集控制系统设计 [J], 田嵩;熊皓

2.医用电子内镜嵌入式视频采集控制系统设计与实现 [J], 葛俊杰;严壮志;王牧云

3.基于FPGA的高清HD-SDI视频采集系统设计与实现 [J], 钱宏文;刘会;付强;王毅

4.基于Gstreamer的视频采集编码与传输系统的设计 [J], 张雷;崔雪峰

5.基于STM32的WI-FI视频采集与传输系统设计 [J], 林开司;张露

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于ECP3的视频采集系统硬件设计

摘要:本文介绍了基于FPGA芯片ECP3-70的视频采集系统硬件设计。

CMOS传感器MT9P031与FPGA芯片ECP3-70的BANK0连接,进行视频采集。

采集到的视频数据通过千兆以太网物理层芯片88E1118R上传至服务器。

关键词:ECP3-70 MT9P031 88E1118R

目前视频采集系统种类非常多,各有各的用途[1]。

本文设计一种用较少芯片构成的、体积小型化,用于狭窄空间的高清视频采集传输系统。

1 系统构成

基于ECP3-70的视频采集系统如图1所示。

系统采用LATTICE 公司的FPGA芯片ECP3-70作为主控芯片。

该芯片拥有67K LUTs,4320 Kbit系统存储器,4420 Kbit嵌入式存储器,145 Kbit分布式存储器,128个18×18乘法器,10个PLL,8个BANK、380个I/O。

同时LATTICE拥有丰富的IP资源[2]。

ECP3-70比较适合用在集成化要求高的场合。

视频采集系统的数据存储器采用2片EDE1116ACBG构成。

该芯片是DDR2存储芯片,空间大小8 M×16 bit,1.8 V支持电压,800 Mbps 吞吐率[3]。

FPGA配置FLASH采用W25Q64构成。

该芯片容量为64

Mbit,SPI接口,2.7~3.6 V电源电压[4]。

关键数据保存的EEPROM采用AT93C65构成,容量为4 Kbit,三线串行接口,2M时钟速率,2.7~5.5 V电源电压[5]。

系统的工作过程如图1所示。

系统上电,ECP3-70从W25Q64中读取程序数据码流,启动自身按程序工作。

ECP3-70通过I2C接口配置CMOS传感器MT9P031,控制MT9P031获取视频数字信号。

采集到的视频数据通过ECP3-70的I/O口获取,按乒乓存储结构存放在EDE1116ACGB中。

ECP3-70从AT93C56中读取视频配置信息,配置从存储器中读出的原始视频数字信号。

ECP3-70经过内嵌的千兆网MAC-IP核,控制千兆网物理层芯片88E1118R,把配置好的视频数据信号,经千兆RJ45接口发送到指定服务器中。

2 MT9P031与ECP3-70的连接

MT9P031与ECP3-70的连接时,在硬件上需要考虑时序、速率和电平问题。

MT9P031芯片的寄存器配置时序为I2C时序。

MT9P031的视频数据输出为12位并行输出,同步时钟为像素时钟、行同步信号、帧同步信号。

即按照像素时钟的频率输出一个12位数据表示的像素;按照行同步信号时钟的频率输出一行像素;按照帧同步信号时钟频率输出一帧像素[6]。

ECP3-70作为FPGA芯片,可以在内部使用VHLD 语言或VERILOG语言编写程序,使得FPGA和MT9P031的I2C时序、

像素时序完全匹配。

MT9P031的I2C最大时钟频率为400 kHz,像素时钟频率为96 MHz。

ECP3-70的时钟频率可超300 MHz,满足MT9P031任何速率要求。

MT9P031有2种供电电压,分别为1.8 V和2.8 V,本系统选用2.8 V。

MT9P031的I/O和ECP3-70的BANK0连接,ECP3-70的BANK0支持电源电压选择为2.5 V。

MT9P031和ECP3-70的I/O口电平对比如表1所示。

由表1表示中可见MT9P031在电平特性上完全可以和ECP3-70实现无缝连接。

由此可见MT9P031的所有数据接口可以和ECP3-70的BANK0的I/O直接连接在一起(见表1)。

3 88E1118R与ECP3-70的连接

千兆以太网物理层芯片88E1118R与ECP3-70的连接同样要考虑接口的速率、时序和电平特性。

由于ECP3-70已经把BANK0连接到CMOS传感器MT9P031上了,所以把ECP3-70的BANK7和88E1118R 连接。

88E1118R的GMII接口时钟速率为125 MHz,时钟上升沿和下降沿同时锁定4位数据,由此GMII的速率可以达到1Gbps[7]。

显然ECP3-70的I/O是能够满足GMII接口的速率和时序需要的。

同时ECP3-70给BANK7的I/O接口供电为3.3 V,和8831118R的供电电源一致。

ECP3-70在内嵌千兆网MAC-IP核的情况下,完全能控制88E1118R,形成千兆网链路。

4 结论

基于ECP3的视频采集系统设计完成后,PCB面积不大于75 mm×75 mm。

若是把MT9P031和ECP3电路分开制成2块PCB,则每块PCB不大于50 mm×50 mm,完全可以用在对空间要求苛刻、数据传输率要求高的场合。

基于ECP3的视频采集系统设计具有很强的实用性,同时也具有一定的参考意义。

参考文献

[1] 任志健,万智萍,朱俊南,等.ARM嵌入式远程视频监控数据采集系统设计[J].计算技术与自动化[J].2013,2:100-110.

[2] Lattice Semiconductor Corporation. Lattice ECP3 Family Data Sheet[EB/OL]..

[3] Elpida Memory Inc.1G bits DDR2 SDRAM[EB/

OL]..

[4] Winbond Inc.3V 64M-BIT SERIAL FLASH MEMEORY WITH DUAL/QUAD SPI&QPI[EB/OL]..

[5] ATMEL Corporation.3-Wire Serial EEPROs [EB/OL]..

[6] Aptina Imaging Corporation.1/2.5-Inch 5Mp CMOS Digital Image Sensor [EB/OL]..

[7] MARVELL Corporation.Alaska 88e1118r Technical Product Brief[EB/OL].http://www.marvell.。