DSP原理与应第四章.ppt

合集下载

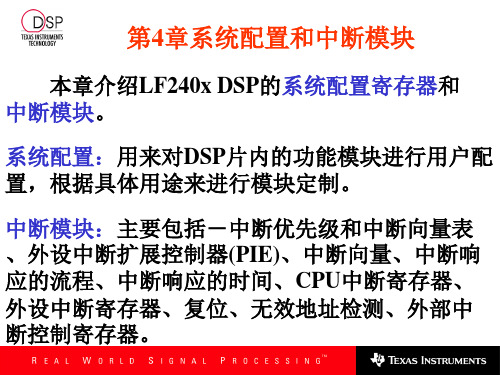

第四章 F2833x系统时钟及中断控制-TMS320F28335 DSP原理、开发及应用-符晓

在CPU崩溃时对其复位

看门狗计数器独立于CPU而运行 看门狗计数器溢出时,产生复位或者中断

CPU正常运行时看门狗计数器被定时复位,即“喂狗” 150MHz的时钟频率相当于6.67ns,看门狗计数器是16

位的,从0开始计数到计满溢出是65536个数,即 6.67ns*65536=4.396ms

第四章 系统时钟及中断控制

4.1 F2833x OSC与PLL (对应: SysCtrl.c)

3.3V时钟脉冲输入

外部晶振

片上振 荡器

PLL工作模式 XRS

表4-1 PLL工作模式

工作模式介绍

PLLSTS[DIVSEL]

PLL关闭

通过将PLLSTS寄存器中的PLLOFF位置1可将PLL模块关闭,从而减少

2-0

HSPCLK

ADC

2-0

LSPCLK

SCI / SPI / I2C / McBSP

4.2 外设时钟信号的寄存器

SysCtrlRegs.PCLKCR0

15

14

13

ECANB ECANA MA ENCLK ENCLK ENCLK

7

6

5

reserved reserved

SCIC ENCLK

12

MB ENCLK

0,1

系统噪声并减少功率损耗。在进入此模式前应首先将PLLCR寄存器设为

0x0000。

2

3

PLL旁路

上电复位或 复位后,PLL进入该模式。在该模式下时钟信号直接绕过

0,1

PLL模块,但PLL模块却未关闭。

2

3

PLL使能

向PLLCR寄存器中写入非零的数可使能PLL模块,一旦写入数据后,PLL

看门狗计数器独立于CPU而运行 看门狗计数器溢出时,产生复位或者中断

CPU正常运行时看门狗计数器被定时复位,即“喂狗” 150MHz的时钟频率相当于6.67ns,看门狗计数器是16

位的,从0开始计数到计满溢出是65536个数,即 6.67ns*65536=4.396ms

第四章 系统时钟及中断控制

4.1 F2833x OSC与PLL (对应: SysCtrl.c)

3.3V时钟脉冲输入

外部晶振

片上振 荡器

PLL工作模式 XRS

表4-1 PLL工作模式

工作模式介绍

PLLSTS[DIVSEL]

PLL关闭

通过将PLLSTS寄存器中的PLLOFF位置1可将PLL模块关闭,从而减少

2-0

HSPCLK

ADC

2-0

LSPCLK

SCI / SPI / I2C / McBSP

4.2 外设时钟信号的寄存器

SysCtrlRegs.PCLKCR0

15

14

13

ECANB ECANA MA ENCLK ENCLK ENCLK

7

6

5

reserved reserved

SCIC ENCLK

12

MB ENCLK

0,1

系统噪声并减少功率损耗。在进入此模式前应首先将PLLCR寄存器设为

0x0000。

2

3

PLL旁路

上电复位或 复位后,PLL进入该模式。在该模式下时钟信号直接绕过

0,1

PLL模块,但PLL模块却未关闭。

2

3

PLL使能

向PLLCR寄存器中写入非零的数可使能PLL模块,一旦写入数据后,PLL

DSP技术原理及应用教程

跨学科融合

加强与数学、物理学、生物学等其他学科的交叉融合,以开拓DSP技 术在更多领域的应用。

注重实际应用

在研究过程中,注重与实际应用的结合,以提高DSP技术的实用性和 市场竞争力。

THANKS

感谢观看

应用前景

通信领域

DSP技术将在通信领域发挥重 要作用,如调制解调、信号编

解码等。

音频处理

DSP技术在音频信号处理方面 具有天然优势,如音频编解码 、音频效果处理等。

图像处理

DSP技术也可应用于图像信号 处理,如图像增强、目标检测 等。

工业控制

DSP技术将应用于工业控制领 域,实现智能化、高精度的信

号处理。

06

结论

主要观点总结

DSP技术原理

数字信号处理(DSP)是一门跨学科的综合性技术,涉及数学、电路、计算机等多个领域。其主要原理是将模拟信号转换 为数字信号,然后通过计算机进行运算处理,以达到改善信号质量或提取有用信息的目的。

应用领域

DSP技术在通信、雷达、声呐、图像处理、语音识别、生物医学工程等领域有着广泛的应用。通过DSP技术,可以实 现信号的滤波、频谱分析、参数估计、模式识别等功能。

FFT算法将DFT的计算复杂度从 $O(N^2)$降低到$O(Nlog N)$,大 大提高了计算效率。

03

DSP技术的应用领域

通信领域

调制解调

频谱分析

信道均衡

语音压缩

在数字通信中,调制解调是 将基带信号转换为频带信号 的过程,反之亦然。DSP技 术可以快速实现各种调制解 调算法,如QPSK、QAM等 ,提高通信速率和抗干扰能 力。

DSP芯片采用先进的制程技术,具有低功耗 的特点,延长了设备的待机时间。

加强与数学、物理学、生物学等其他学科的交叉融合,以开拓DSP技 术在更多领域的应用。

注重实际应用

在研究过程中,注重与实际应用的结合,以提高DSP技术的实用性和 市场竞争力。

THANKS

感谢观看

应用前景

通信领域

DSP技术将在通信领域发挥重 要作用,如调制解调、信号编

解码等。

音频处理

DSP技术在音频信号处理方面 具有天然优势,如音频编解码 、音频效果处理等。

图像处理

DSP技术也可应用于图像信号 处理,如图像增强、目标检测 等。

工业控制

DSP技术将应用于工业控制领 域,实现智能化、高精度的信

号处理。

06

结论

主要观点总结

DSP技术原理

数字信号处理(DSP)是一门跨学科的综合性技术,涉及数学、电路、计算机等多个领域。其主要原理是将模拟信号转换 为数字信号,然后通过计算机进行运算处理,以达到改善信号质量或提取有用信息的目的。

应用领域

DSP技术在通信、雷达、声呐、图像处理、语音识别、生物医学工程等领域有着广泛的应用。通过DSP技术,可以实 现信号的滤波、频谱分析、参数估计、模式识别等功能。

FFT算法将DFT的计算复杂度从 $O(N^2)$降低到$O(Nlog N)$,大 大提高了计算效率。

03

DSP技术的应用领域

通信领域

调制解调

频谱分析

信道均衡

语音压缩

在数字通信中,调制解调是 将基带信号转换为频带信号 的过程,反之亦然。DSP技 术可以快速实现各种调制解 调算法,如QPSK、QAM等 ,提高通信速率和抗干扰能 力。

DSP芯片采用先进的制程技术,具有低功耗 的特点,延长了设备的待机时间。

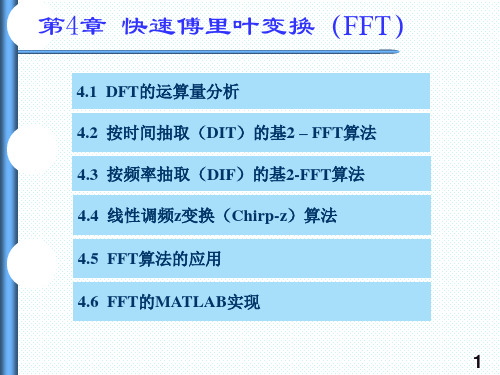

数字信号处理DSP第4章

G[3] 1

k 0,1, , N 1

2

13

4.2 按时间抽取(DIT)的基2–FFT算法

将系数统一为 WNk 2 WN2k ,则可得

x[0]

N 4点

x[4]

DFT

G[0]

X [0]

G[1]

X [1]

x[2]

N 4点

WN0

x[6]

DFT

WN2

G[2]

1 G[3]

1

X [2] X [3]

x[1]

N 4点

X m1[i] WNr X m1[ j] , X m1[i] WNr X m1[ j]

m 1, 2 ,

每一个蝶形需要一次复数乘法和两次复数加法。

17

4.2 按时间抽取(DIT)的基2–FFT算法

N点的DIT-FFT计算量为

复数乘法:

1

N 2

log2

N

N 2

复数加法:

2

N 2

log2

N

N

例: 如果每次复数乘法需要100us,每次复数加法需要20us,来 计算N=1024点DFT,则需要

12

4.2 按时间抽取(DIT)的基2–FFT算法

同理

( N 4)1

( N 4)1

G[k] DFT[g[r]]

g[2l]WN2lk2

g[2l 1]WN(22l1)k

l 0

l 0

( N 4)1

( N 4)1

g[2l]WNlk 4 WNk 2

g[2l 1]WNlk 4 ,

l 0

l 0

k 0,1,

(3) WN0 WN4 WN8 WN12 WN16 WN20 WN24 WN28

或 WN4i i 0,1, 2, 3, 4, 5, 6, 7 (dm 1)

k 0,1, , N 1

2

13

4.2 按时间抽取(DIT)的基2–FFT算法

将系数统一为 WNk 2 WN2k ,则可得

x[0]

N 4点

x[4]

DFT

G[0]

X [0]

G[1]

X [1]

x[2]

N 4点

WN0

x[6]

DFT

WN2

G[2]

1 G[3]

1

X [2] X [3]

x[1]

N 4点

X m1[i] WNr X m1[ j] , X m1[i] WNr X m1[ j]

m 1, 2 ,

每一个蝶形需要一次复数乘法和两次复数加法。

17

4.2 按时间抽取(DIT)的基2–FFT算法

N点的DIT-FFT计算量为

复数乘法:

1

N 2

log2

N

N 2

复数加法:

2

N 2

log2

N

N

例: 如果每次复数乘法需要100us,每次复数加法需要20us,来 计算N=1024点DFT,则需要

12

4.2 按时间抽取(DIT)的基2–FFT算法

同理

( N 4)1

( N 4)1

G[k] DFT[g[r]]

g[2l]WN2lk2

g[2l 1]WN(22l1)k

l 0

l 0

( N 4)1

( N 4)1

g[2l]WNlk 4 WNk 2

g[2l 1]WNlk 4 ,

l 0

l 0

k 0,1,

(3) WN0 WN4 WN8 WN12 WN16 WN20 WN24 WN28

或 WN4i i 0,1, 2, 3, 4, 5, 6, 7 (dm 1)

《DSP原理及应用》电子教案全套课件

第1章 绪论

1.1 数字信号处理概述 1.2 数字信号处理器概述

1.1 数字信号处理概述

1.1.1 数字信号处理系统的构成 1.1.2 数字信号处理的实现 1.1.3 数字信号处理的特点

返回首页

1.1.1 数字信号处理系统的构成

图1-1 典型的数字信号处理系统

返回本节

1.1.2 数字信号处理的实现

返回本节

图2-1 TMS320C54x DSP的内部硬件组成框图2

2.2 TMS320C54x的总线结构

TMS320C54x DSP采用先进的哈佛结构并具有八 组总线,其独立的程序总线和数据总线允许同时 读取指令和操作数,实现高度的并行操作。 采用各自分开的数据总线分别用于读数据和写数 据,允许CPU在同一个机器周期内进行两次读操 作数和一次写操作数。独立的程序总线和数据总 线允许CPU同时访问程序指令和数据。

返回首页

存储器 64 K字程序存储器、64 K字数据存储器以及64 K 字 I/O 空间。在 C548、C549、C5402、C5410 和 C5420中程序存储器可以扩展。

指令系统 单指令重复和块指令重复操作。 块存储器传送指令。 32位长操作数指令。 同时读入两个或3个操作数的指令。 并行存储和并行加载的算术指令。 条件存储指DSP芯片的主要特点

1.哈佛结构 2.多总线结构 3.指令系统的流水线操作 4.专用的硬件乘法器 5.特殊的DSP指令 6.快速的指令周期 7.硬件配置强

时钟 取指 译码 取操作数 执行 N N-1 N-2 N-3 N+1 N N-1 N-2 N+2 N+1 N N-1 N+3 N+2 N+1 N

1.1 数字信号处理概述 1.2 数字信号处理器概述

1.1 数字信号处理概述

1.1.1 数字信号处理系统的构成 1.1.2 数字信号处理的实现 1.1.3 数字信号处理的特点

返回首页

1.1.1 数字信号处理系统的构成

图1-1 典型的数字信号处理系统

返回本节

1.1.2 数字信号处理的实现

返回本节

图2-1 TMS320C54x DSP的内部硬件组成框图2

2.2 TMS320C54x的总线结构

TMS320C54x DSP采用先进的哈佛结构并具有八 组总线,其独立的程序总线和数据总线允许同时 读取指令和操作数,实现高度的并行操作。 采用各自分开的数据总线分别用于读数据和写数 据,允许CPU在同一个机器周期内进行两次读操 作数和一次写操作数。独立的程序总线和数据总 线允许CPU同时访问程序指令和数据。

返回首页

存储器 64 K字程序存储器、64 K字数据存储器以及64 K 字 I/O 空间。在 C548、C549、C5402、C5410 和 C5420中程序存储器可以扩展。

指令系统 单指令重复和块指令重复操作。 块存储器传送指令。 32位长操作数指令。 同时读入两个或3个操作数的指令。 并行存储和并行加载的算术指令。 条件存储指DSP芯片的主要特点

1.哈佛结构 2.多总线结构 3.指令系统的流水线操作 4.专用的硬件乘法器 5.特殊的DSP指令 6.快速的指令周期 7.硬件配置强

时钟 取指 译码 取操作数 执行 N N-1 N-2 N-3 N+1 N N-1 N-2 N+2 N+1 N N-1 N+3 N+2 N+1 N

DSP原理与应用 第三版

运算速度 以上。TMS320C6201执行1024点复数FFT运算时间只有66uS。

高度集成化

集滤波、A/D、D/A、ROM、RAM和DSP内核于一体的

运算精度和动态范围

模拟混合式DSP芯片已有较大的发展和应用。 DSP字长从8位已增到64位,累加器长度也增到40位,

开发工具

提高了运算精度。同时,采用超长字指令字(VLIW)结构和

2. TMS320C55x概况

目前C55x系列芯片主要有:

C5501/2(主频300MHz, McBSP,HPI接口), C5503/6/7/9A (主频200MHz, McBSP, HPI,

优点:成本低廉 缺点:性能差、

速度慢

DSP处理器

优点:速度高、大规模生产成本低; 缺点:开发成本高、通用性差。

针对数字信号处理的要求而设计,是数 字信号处理系统设计中采用的主流芯片。 优点:灵活、高速、便于嵌入式应用

7

1.2 DSP芯片简介

1.2.1 DSP芯片的发展历史、现状和趋势 1.2.2 DSP芯片的特点 1.2.3 DSP芯片的分类 1.2.4 DSP芯片的应用领域 1.2.5 选择DSP芯片考虑的因素

可同时进行取指令和多个数据存取操作,使CPU

在一个机器周期内可多次对程序空间和数据空

采用哈佛结构 间进行访问, 大大地提高了DSP的运行速度。

采用多总线结构

T1

T2

T3

T4

时钟

采用流水线结构

取指令

N

N+1

N+2

N+3

指令译码

N-1

N

N+1

N+2

配有专用的硬件乘法-累加器 取操作数 N-2

DSP第四章

位8:保留 位7:ADC CLKEN,ADC模块时钟使能控制位 0-禁止ADC模块时钟(节能) 1-使能ADC模块时钟,且正常运行 位6:SCICLKEN,SCI模块时钟使能控制位 0-禁止SCI模块时钟(节能) 1-使能SCI模块时钟,且正常运行

位5:SPICLKEN, SPI模块时钟使能控制位 0-禁止SPI模块时钟(节能) 1-使能SPI模块时钟,且正常运行 位4:CANCLKEN, CAN模块时钟使能控制位 0-禁止CAN模块时钟(节能) 1-使能CAN模块时钟,且正常运行 位3:EVBCLKEN, EVB模块时钟使能控制位 0-禁止EVB模块时钟(节能) 1-使能EVB模块时钟,且正常运行

如这些引脚作I/O使用,则不使用输入时钟限定电路

位5:WD保护位,该位可用来禁止WD工作。该位 是-个只能清除的位,复位后=1。通过向该位写 1对其清0。

0-保护WD,防止WD被软件禁止。 1-复位时的默认值,能够通过软件禁止WD工作 位4:XMIF HI-Z。该位控制外部存储器接口信号 (XMIF)。 0-所有XMIF信号为正常驱动模式(非高阻态)。 1-所有XMIF信号处于高阻态。

外设中断请求寄存器和外设中断应答寄存器 都属于外设中断扩展模块用来向CPU产生INT1INT6中断请求的内部寄存器。这些寄存器用于测 试目的,编程时可以忽略。用户只能对其读。 1.外设中断向量寄存器(PIVR) 外设中断向量寄存器(PIVR)映射在数据存储 器空间中的地址为701Eh,该寄存器的16位V15- V0,为最近一次被应答的外设中断的地址向量。

中断请求(PIRQ)标志位一直保持到中断应答自动 清除或用软件将其清除。 在高层次中断,或逻辑运算的多个外设中断请求 INTn产生一个到CPU的中断请求,它是2个CPU时 钟脉冲宽的低电平脉冲。 当多个外设同时发出中断请求时,CPU总是响应 优先级高的中断请求。 注意:外设中断请求标志位是在CPU响应中断时 自动清除,即在高层次中断时清0,而不是在低层 次中断时,清0。

TMS320C55X_dsp原理及应用_第4章NEW

编译结果如下: _foo: MOV #10 , port(#_i) ; 将10存在_i中 MOV #_i , port( #_iop_ptr_to_ioport ) ; 存储_i的地址 MOV port(#_iop_ptr_to_ioport),AR3 ; 载入_i的地址 MOV *AR3 , AR1 ; 载入 _i MOV AR1 , port(# _j) ; 将10存到 _ j中 return

32位数据

AC0、AC1、AC2

( 2 ) 函数调用规则

父函数收集返回值,子函数的返回值也根据返回参数的 类型 使用不同的寄存器。

表4-5 C语言函数调用中返回参数所使用的寄存器表 子函数返回类型 Void char、unsigned char、 short int 、int long int 、float 、 double struct T0 AC0 所使用的寄存器 说明 无返回参数 返回16位数据 返回32位数据

挂起状态

被中断状态

任务状态转换

信号量

两种类型

二进制型—看做一个只有一位的计数器型信号量 计数器型 单向同步

两个任务之间利用信号量来取得同步

任务用一个信号量触发另一个任务

双向同步

通信

通信途径:全局变量或消息 消息邮箱:初始化邮箱内的消息;将消息 放入邮箱;等待消息进入邮箱;从邮箱中 取得消息。 消息队列:消息队列初始化,即将消息队 列清空;将一个消息放到消息队列之中; 等待消息到来;得到消息。

采用直接嵌套的方法要十分小心,这是因为C 语言编译器并不检查的分析所嵌入的汇编语言。如 果采用嵌套汇编语句,在编译时不应采用优化功能。 如果采用该方法实现较复杂的功能,会造成 程序的可读性较差,并影响程序的可移植性,因此 更可行的方法数独立编写C语言程序和汇编程序, C语言通过函数调用汇编子程序,这样既提高了程 序的运行效率,有保证了程序的可移植性,这样做 的优点还有程序的结构性较好,并不影响C语言编 译器的优化功能。

32位数据

AC0、AC1、AC2

( 2 ) 函数调用规则

父函数收集返回值,子函数的返回值也根据返回参数的 类型 使用不同的寄存器。

表4-5 C语言函数调用中返回参数所使用的寄存器表 子函数返回类型 Void char、unsigned char、 short int 、int long int 、float 、 double struct T0 AC0 所使用的寄存器 说明 无返回参数 返回16位数据 返回32位数据

挂起状态

被中断状态

任务状态转换

信号量

两种类型

二进制型—看做一个只有一位的计数器型信号量 计数器型 单向同步

两个任务之间利用信号量来取得同步

任务用一个信号量触发另一个任务

双向同步

通信

通信途径:全局变量或消息 消息邮箱:初始化邮箱内的消息;将消息 放入邮箱;等待消息进入邮箱;从邮箱中 取得消息。 消息队列:消息队列初始化,即将消息队 列清空;将一个消息放到消息队列之中; 等待消息到来;得到消息。

采用直接嵌套的方法要十分小心,这是因为C 语言编译器并不检查的分析所嵌入的汇编语言。如 果采用嵌套汇编语句,在编译时不应采用优化功能。 如果采用该方法实现较复杂的功能,会造成 程序的可读性较差,并影响程序的可移植性,因此 更可行的方法数独立编写C语言程序和汇编程序, C语言通过函数调用汇编子程序,这样既提高了程 序的运行效率,有保证了程序的可移植性,这样做 的优点还有程序的结构性较好,并不影响C语言编 译器的优化功能。

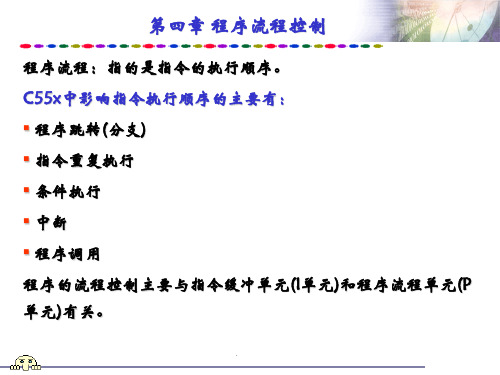

DSP第四章 DSP程序流程控制

第四章 程序流程控制

程序流程:指的是指令的执行顺序。 C55x中影响指令执行顺序的主要有: 程序跳转(分支) 指令重复执行 条件执行 中断

程序调用

程序的流程控制主要与指令缓冲单元(I单元)和程序流程单元(P 单元)有关。

第四章 程序流程控制

P单元产生24位的程序地址,并放到PAB总线上。

1=255

举例: RPTCC #7, AC1 > #0 ADD #1,AC0 ;AC0=AC0+1

第四章 程序流程控制

以下指令不能用做单指令循环体: B ;跳转 IDLE ;空闲指令 RPTBLOCAL ;块重复 RESET;软件复位 MOV RPTC, TAx ;RPTC单指令重复计数器

TRAP ;软件陷阱 MOV dbl(Lmem), RETA

RPTBLOCAL和RPTB区别

RPTBLOCAL被定义为指令缓冲队列(IBQ)的本地循环,即直接 从IBQ中获取循环体指令,这样可以减少功率消耗,但是循环 体指令的字数不能超过56个字节。 当循环体指令超过56个字节时,使用RPTB块循环。

第四章 程序流程控制 支持两层块循环 一层循环(外循环):BRC0, RSA0, REA0; 二层循环(内循环): BRC1, RSA1, REA1,BRS1;

第四章 程序流程控制

vector: (4) 执行中断服务程序 rs b _c_int00 nop ISR包含中断返回指令,当中断返回时,自动恢复以前保存 nop nmi b __ret 在寄存器中的内容。 nop nop 3、中断矢量及其优先级 int0 b __ret CPU接受和响应中断请求后,产生一个中断矢量地址,地址 nop nop 指向相关中断服务程序的中断矢量。书中表4-2。 . 多个中断同时发生时,CPU按照事先定义的优先级进行处理。 . . 优先级为0的优先权最高,随着优先级数的逐步增加,优先 dmac5 b __ret 权逐步减小。 nop nop

程序流程:指的是指令的执行顺序。 C55x中影响指令执行顺序的主要有: 程序跳转(分支) 指令重复执行 条件执行 中断

程序调用

程序的流程控制主要与指令缓冲单元(I单元)和程序流程单元(P 单元)有关。

第四章 程序流程控制

P单元产生24位的程序地址,并放到PAB总线上。

1=255

举例: RPTCC #7, AC1 > #0 ADD #1,AC0 ;AC0=AC0+1

第四章 程序流程控制

以下指令不能用做单指令循环体: B ;跳转 IDLE ;空闲指令 RPTBLOCAL ;块重复 RESET;软件复位 MOV RPTC, TAx ;RPTC单指令重复计数器

TRAP ;软件陷阱 MOV dbl(Lmem), RETA

RPTBLOCAL和RPTB区别

RPTBLOCAL被定义为指令缓冲队列(IBQ)的本地循环,即直接 从IBQ中获取循环体指令,这样可以减少功率消耗,但是循环 体指令的字数不能超过56个字节。 当循环体指令超过56个字节时,使用RPTB块循环。

第四章 程序流程控制 支持两层块循环 一层循环(外循环):BRC0, RSA0, REA0; 二层循环(内循环): BRC1, RSA1, REA1,BRS1;

第四章 程序流程控制

vector: (4) 执行中断服务程序 rs b _c_int00 nop ISR包含中断返回指令,当中断返回时,自动恢复以前保存 nop nmi b __ret 在寄存器中的内容。 nop nop 3、中断矢量及其优先级 int0 b __ret CPU接受和响应中断请求后,产生一个中断矢量地址,地址 nop nop 指向相关中断服务程序的中断矢量。书中表4-2。 . 多个中断同时发生时,CPU按照事先定义的优先级进行处理。 . . 优先级为0的优先权最高,随着优先级数的逐步增加,优先 dmac5 b __ret 权逐步减小。 nop nop

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.HPI与主机的连接

HCNTL0、

主机控制信号,与主机地址线

HCN或TL控1:制线连接,用来选择主机所要寻址的寄

存器。

HCNTL0 HCNTL1

功能说明

0

0

主机可以读/写HPIC寄存器。

主机可以读/写HPID寄存器。

0

1

每读1次,HPIA事后增1;

每写1次,HPIA事先增1。

1

0

主机可以读/写HPIA寄存器。 这个寄存器指向HPI存储器。

可以访问HPI RAM,而’C54x则配置为最小功耗

。 2021年2月25日

DSP原理及应用

4

第4章 TMS320C54x的片内外设、接口及应用

4.1 ’C54x的主机接口

HPI口可以支持主设备与’C54x之间的高速 数据传送。

在SAM工作方式时,若HPI每5个CLKOUT周 期传送一个字节,则主机的运行频率可达(fd×n)/5 。 f在d—H—OM’方C5式4x时的,C主LK机O可UT以频获率得;更高的速度。 即每5n—0n—s寻主址机一每个进字行节一(次即外16部0寻M址bp的s)周,期且数与,通 常 ’nC是543x(的或时4)钟。速度无关。

1.HPI与主机的连接

HPI与主机连接的信号名称和功能:

HD0~HD 双向并行三态数据总线,与主机数据总

7:

线相连。

当不传送数据(HDSx或HCS=1)或EMU1/OFF=0(切 断所有输出)时,HD7~HD0均处于高阻状态。

HCS: 片选信号,与主机地址线或控制线相连。

作为HPI的使能输入端,在每次寻址期间必须 为低电平,而两次寻址之间也可以停留在低电平。

第4章 TMS320C54x片内外设、接口及应用

内容提要

本章详细介绍了TMS320C54x中主机接口HPI、定

时器、串行接口和中断系统。

主机接口HPI是TMS320C54x系列定点芯片内部具

有的一种接口部件,主要用于DSP与其他总线或CPU进

行通信。HPI接口通过HPI控制寄存器(HPIC)、地址

寄存器(HPIA)、数据锁存器(HPID)和HPI内存块实现

数据总线以及数据控线 制信号8 线外,不H需D0~H要D7 附加其他的逻

辑电路。主机 地址

HCNTL0 HCNTL0

读/写

HBIL TMS320C54x

HR/W

HDS1

数据口

HDS2

HCS

地址锁存使能

HAS

准备

HRDY

中断

HINT

2021年2月25日

DSP原理及应用

6

第4章 TMS320C54x的片内外设、接口及应用

DSP54x片内外设、接口及应用

4.1 ’C54x的主机接口 4.2 ’C54x的定时器 4.3 ’C54x的串行接口 4.4 ’C54x的中断系统

2021年2月25日

DSP原理及应用

2

第4章 TMS320C54x的片内外设、接口及应用

4.1 ’C54x的主机接口

2021年2月25日

DSP原理及应用

7

第4章 TMS320C54x的片内外设、接口及应用

1.HPI与主机的连接

HPI与主机连接的信号名称和功能:

HAS 地址选通信号,与主机地址锁存使能(ALE)或 : 地址选通引脚相连,也可以不使用。

若主机的地址和数据是一条多路总线,HAS则 与主机的ALE引脚相连。在HAS的下降沿,锁存HBIL 、HCNTIL0/1和HR/W信号;

’C54x的主机接口(HPI)是一个8位并行口,用

来实现与主设备或主处理器的通信。

主机与HPI的通信,可通过专用地址和数据寄

存器、HPI控制寄存器以及使用外部数据与接口控制

信号来实现。

HPI口作为主机的外围设备,提供8根外部数据线

HD(0~7)与主机(或主设备)交换信息。当’C54x与

主机传送数据时,HPI能自动地将外部接口连续传来

的8位数组成16位数,并传送至’C54x。当主机使

用HPI寄存器执行数据传输时,HPI控制逻辑自动执

行对’C54x内部的双寻址RAM的访问,以完成数据

处理。 2021年2月25日

DSP原理及应用

3

第4章 TMS320C54x的片内外设、接口及应用

4.1 ’C54x的主机接口

HPI接口有两种工作方式:

例如:’C54x的CLKOUT频率为40MHz,那么主

机的时钟频率可达32(或24)MHz,且不插入等待周

期。 2021年2月25日

DSP原理及应用

5

第4章 TMS320C54x的片内外设、接口及应用

4.1 ’C54x的主机接口

1.HPI与主机的连接

’C54x通过HPI与主机设备连接,除了8位HPI

共用寻址模式(SAM方式)

在这种方式下,主机和’C54x都能寻址HPI存 储器。如果是异步工作的主机寻址,可在HPI内部 重新得到同步。当’C54x与主机的周期发生冲突时

,则主机具有寻址优先权,’C54x将等待一个周期 。 主机寻址模式(HOM方式)

在HOM方式下,HPI存储器只能让主机寻址,

而’C54x则处于复位状态或IDLE2空转状态。主机

当HBIL=0时,为第1字节;当HBIL=1时,为第2 字节。第1个字节是高字节还是低字节,由HPIC寄 存器中的BOB位决定。

HRDY:HPI准备好端,与主机异步准备好线相连。

高电平表示HPI已准备好,可执行一次数据传

送;低电平表示HPI正忙于完成当前事务。

2021年2月25日

DSP原理及应用

9

第4章 TMS320C54x的片内外设、接口及应用

若主机的地址和数据线是分开的,则HAS接高

电平,此时由HDS1、HDS2或HCS中最迟的下降沿锁

存HBIL、HCNTL0/1和HR/W信号。

2021年2月25日

DSP原理及应用

8

第4章 TMS320C54x的片内外设、接口及应用

1.HPI与主机的连接

HPI与主机连接的信号名称和功能:

HBIL: 字节识别信号,与主机地址线或控制线连 接,用于识别主机传送来的是第几字节。

1

1

主机可以读/写HPID寄存器。 HPIA寄存器不受影响

2021年2月25日

与主机通信。

片内定时器包括定时寄存器TIM、定时周期寄存

器PRD和定时控制寄存器TCR。

TMS320C54x的串行口有4种类型:标准同步串口

BP、缓冲同步串口BSP、多路缓冲串口McBSP和时分多

路同步串口TMD。

中断是由硬件或软件驱动的中断信号,使CPU中

断当前程序,去执行中断服务程序。

2021年2月25日