实验二算术运算实验

计算机组成原理--实验二算术逻辑运算实验

计算机组成原理--实验⼆算术逻辑运算实验实验⼆算术逻辑运算实验⼀、实验⽬的(1)了解运算器芯⽚(74LS181)的逻辑功能。

(2)掌握运算器数据的载⼊、读取⽅法,掌握运算器⼯作模式的设置。

(3)观察在不同⼯作模式下数据运算的规则。

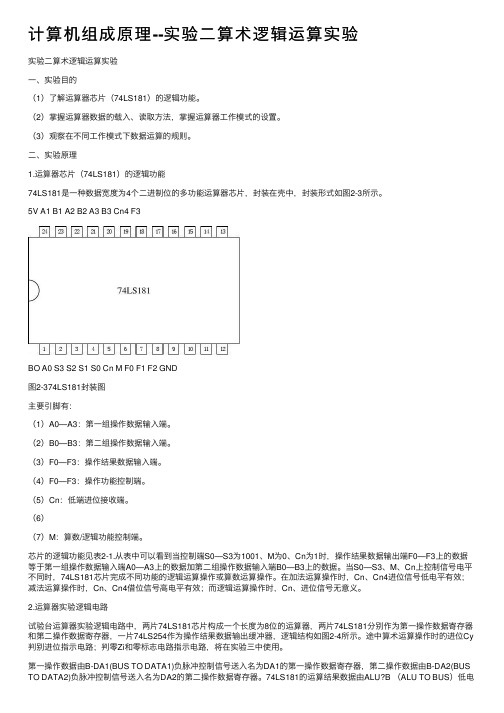

⼆、实验原理1.运算器芯⽚(74LS181)的逻辑功能74LS181是⼀种数据宽度为4个⼆进制位的多功能运算器芯⽚,封装在壳中,封装形式如图2-3所⽰。

5V A1 B1 A2 B2 A3 B3 Cn4 F3BO A0 S3 S2 S1 S0 Cn M F0 F1 F2 GND图2-374LS181封装图主要引脚有:(1)A0—A3:第⼀组操作数据输⼊端。

(2)B0—B3:第⼆组操作数据输⼊端。

(3)F0—F3:操作结果数据输⼊端。

(4)F0—F3:操作功能控制端。

(5)Cn:低端进位接收端。

(6)(7)M:算数/逻辑功能控制端。

芯⽚的逻辑功能见表2-1.从表中可以看到当控制端S0—S3为1001、M为0、Cn为1时,操作结果数据输出端F0—F3上的数据等于第⼀组操作数据输⼊端A0—A3上的数据加第⼆组操作数据输⼊端B0—B3上的数据。

当S0—S3、M、Cn上控制信号电平不同时,74LS181芯⽚完成不同功能的逻辑运算操作或算数运算操作。

在加法运算操作时,Cn、Cn4进位信号低电平有效;减法运算操作时,Cn、Cn4借位信号⾼电平有效;⽽逻辑运算操作时,Cn、进位信号⽆意义。

2.运算器实验逻辑电路试验台运算器实验逻辑电路中,两⽚74LS181芯⽚构成⼀个长度为8位的运算器,两⽚74LS181分别作为第⼀操作数据寄存器和第⼆操作数据寄存器,⼀⽚74LS254作为操作结果数据输出缓冲器,逻辑结构如图2-4所⽰。

途中算术运算操作时的进位Cy 判别进位指⽰电路;判零Zi和零标志电路指⽰电路,将在实验三中使⽤。

第⼀操作数据由B-DA1(BUS TO DATA1)负脉冲控制信号送⼊名为DA1的第⼀操作数据寄存器,第⼆操作数据由B-DA2(BUS TO DATA2)负脉冲控制信号送⼊名为DA2的第⼆操作数据寄存器。

实验二 算术运算

汇编语言实验报告(二)班级:01540802班姓名:南征学号: 20080705信息与电子学院实验二算术运算一、实验目的熟悉利用汇编语言对多精度十六进制和十进制的编程方法,弄清带符号数及不带符号数的运算区别,理解各状态标志位的含义,以及运算结果对各状态标志的影响,掌握无符号数的乘除法运算并保证运算结果不溢出。

二、实验要点对汇编语言的算术运算要分清是有符号的运算还是无符号的运算,当对无符号数进行加减时,要考虑进位CF,对于有符号数进行加减时,要考虑运算结果是否溢出。

为防止溢出,常将操作数利用CBW或CWD指令进行符号扩展后再进行加减运算。

对于多精度的加减运算时,对高位字节或字的加减法要分别采用ADC和DBB;对低位字节或字采用不带进位的加减指令ADD和SUB;在利用循环计算多字节的加减法时,可以用CLC指令将CF初始化为0,然后在循环体内统一使用带进位(或借位)的加减法指令。

在汇编语言进行十进制的加减运算时,首先需将操作数用BCD码示,并且要考虑操作数是用组合的BCD码还是用一个字节表示一个十进制数。

对于组合的BCD码加减法,其结果应放在AL寄存器中,再用DAA和DAS指令进行二——十进制调整。

二对于未组合的BCD码加减法,用AAA和AAS对结果进行二——十进制调整。

此外在进行十进制数减法时,要考虑用大数减小数,因为十进制数运算不能用补码表示。

对于有符号数惩罚要用IMUL指令,对无符号数乘法要用MUL指令。

字乘时AX为约定的一个乘数,其积在DX:AX中;字节相乘时AL为约定的一个乘数,其积在AX中。

乘法指令中的操作数,不得为立即数,可以为通用寄存器或存储器操作数。

对于除法要用IDIV、DIV分别对有符号数和无符号数进行除法运算。

字除法时被除数约定在DX:AX中;字节相除时,被除数约定在AX中,除法指令中的操作数可以为通用寄存器或者存储器操作数,但不得是立即数。

在进行除法运算时要考虑除数是否为零,以及其商是否溢出,在出现除零溢出时,将产生类型号为0的内部中断。

实验二运算器实验

实验二运算器实验实验二运算器am2901实验该实验操作不需用到电脑,不需实现电脑和实验箱的连接,操作全部在实验箱上完成。

实验过程当中,必须认真展开,避免损毁设备,分析可能将碰到的各种现象,推论结果与否恰当,记录运转结果。

实验目的:1、深入细致介绍am2901运算芯片的功能、结构;2、深入细致介绍4片am2901的级联方式;3、深化运算器部件的组成、设计、控制与使用等知识。

教学计算机的运算器部件主体由4片4位的运算器芯片am2901彼此串联形成,它输入16位的数据运算的结果(用y则表示)和4个结果特征位(用cy,f=0000,over,f15则表示)。

它的输出(用d则表示)就可以源自于内部总线。

确定运算器运算的数据来源、运算功能、结果处置,需要使用控制器提供的i8~i0、b3~b0、a3~a0共17个信号。

运算器的输入轻易相连接至地址寄存器ar的输出插槽,用作提供更多地址总线的信息来源。

运算器的输入还经过两个8位的244器件的掌控(采用dc1译码器的ytoib#信号)被送至内部总线ib,用作把运算器中的数据或者运算结果载入内存储器或者输入输出USB芯片。

运算器产生的4个结果特征位的信息需要保存,为此设置一个4位的标志寄存器flag,用于保存这4个结果特征信息,标志寄存器的输出分别用c、z、v、s表示。

控制标志寄存器何时和如何接收送给它的信息,需要使用控制器提供的sst2~sst0三位信号。

运算器还须要按照指令继续执行的建议,正确地获得最高位的位次输出信号,最高位和最低位的移位输出信号,为此须要布局另一个shift的线路,在控制器提供更多的ssh和sci1~sci0三位信号的掌控下,产生运算器最高位的位次输出信号,最高位和最低位的移位输出信号。

相关器件:4片am2901(alu)两片ar(74ls374)一片flag(gal20v8)一片shift(gal20v8)2片244(alutoib,74ls244)2个12位微动开关(红色)3个手动掌控信号内存芯片(hand,74ls240)am2901芯片的结构和功能:参考教材附录部分芯片具体内容线路表明:1、芯片输出受oe#信号控制,仅当其为低电平时,才有y值正常逻辑信号输出,否则输出为高阻态。

北京理工大学汇编实验二报告

北京理工大学汇编实验二报告本科实验报告实验名称:算术运算类操作实验课程名称:CPU与汇编实验实验时间:2015.10.29 任课教师:王耀威实验地点:10-102实验教师:潘丽敏实验类型:□原理验证■综合设计□自主创新学生姓名:王晓玥学号/班级:1120131332/05111311 组号:学院:信息与电子学院同组搭档:专业:信息工程成绩:一、实验要求和目的1、了解汇编语言中的二进制、十六进制、十进制、BCD 码的表示形式;2、掌握各类运算类指令对各状态标志位的影响及测试方法;3、熟悉汇编语言二进制多字节加减法基本指令的使用方法;4、熟悉无符号数和有符号数乘法和除法指令的使用;5、掌握符号位扩展指令的使用。

6、掌握 BCD 码调整指令的使用方法二、软硬件环境1、硬件环境:计算机系统 windows;2、软件环境:装有 MASM、DEBUG、LINK、等应用程序。

三、实验涉及的主要知识1、加减法处理指令主要有加法指令 ADD,带进位加法 ADC,减法指令 SUB,带进位减法指令 SBB。

2.乘除法指令和符号位扩展指令主要有无符号数乘法指令MUL,带符号数乘法指令IMUL,无符号数除法指令DIV,带符号数除法指令 IDIV,以及符号位从字节扩展到字的指令 CBW 和从字扩展到双字的指令 CWD。

3.BCD 码的调整指令主要有非压缩的BCD 码加法调整指令DAA,压缩的 BCD 码减法调整指令 DAS,非压缩的 BCD 码加法调整指令 AAA,非压缩的 BCD 码减法调整指令 AAS,乘法的非压缩 BCD码调整指令 AAM,除法的非压缩 BCD 码调整指令 AAD。

8088/8086 指令系统提供了实现加、减、乘、除运算的上述基本指令,可对表 1 所示的数据类型进行数据运算。

表 1-2-1 数据类型数据运算表数制二进制BCD码带符号无符号组合非组合运算符+、-、×、÷+、-+、-、×、÷操作数字节、字、多精度字节(二位数字)字节(一位数字)四、实验内容与步骤1、对于两组无符号数,087H 和 034H,0C2H 和5FH,试编程求这两组数的和差积商,并考虑计算结果对标志寄存器中状态标志位的影响:(1)实验流程将一组操作数分别用ADD,SUB,MUL,DIV运算(2)实验代码:DATAS SEGMENTBUF1 DB 087HBUF2 DB 034HBUF3 DB 4 DUP(?);此处输入数据段代码DATAS ENDSSTACKS SEGMENT;此处输入堆栈段代码STACKS ENDSCODES SEGMENTASSUME CS:CODES,DS:DATAS,SS:STACKS START:MOV AX,DATASMOV DS,AXMOV AX,0MOV SI,AX;两数相加MOV AL,BUF1MOV BL,BUF2ADD AL,BLMOV BUF3[SI],ALMOV AL,0MOV AL,0INC SIMOV BUF3[SI],AL;两数相减MOV AL,BUF1MOV BL,BUF2SUB AL,BLINC SIMOV BUF3[SI],ALMOV AL,0SBB AL,0INC SIMOV BUF3[SI],AL;两数相乘MOV AL,BUF1MOV BL,BUF2MUL BLINC SIMOV BUF3[SI],ALINC SIMOV BUF3[SI],AH;两数相除,AL中存放商,AH中存放余数MOV AX,0MOV AL,BUF1MOV BL,BUF2DIV BLINC SIMOV BUF3[SI],ALINC SIMOV BUF3[SI],AH;此处输入代码段代码MOV AH,4CHINT 21HCODES ENDSEND START(3)实验结果:1)第一组操作数87H,34H2)第二组操作数0C2H,5FH(4)计算结果计算状态标志表达式结果CF AF ZF OF SF PF 087H+034H 00BB 0 0 0 0 1 1 087H-034H 0053 0 0 0 1 0 1 087H*034H 1B6C 1 0 0 1 0 0 087H/084H 02(1F) 1 0 0 0 0 1 0C2H+05FH 0121 0 0 0 0 0 0 0C2H-O5FH 0063 0 0 1 0 0 1 0C2H*05FH 47FE 0 0 0 0 0 1 0C2H/05FH 02(04) 0 0 0 0 0 0(5)各运算对状态标志位的影响及其意义。

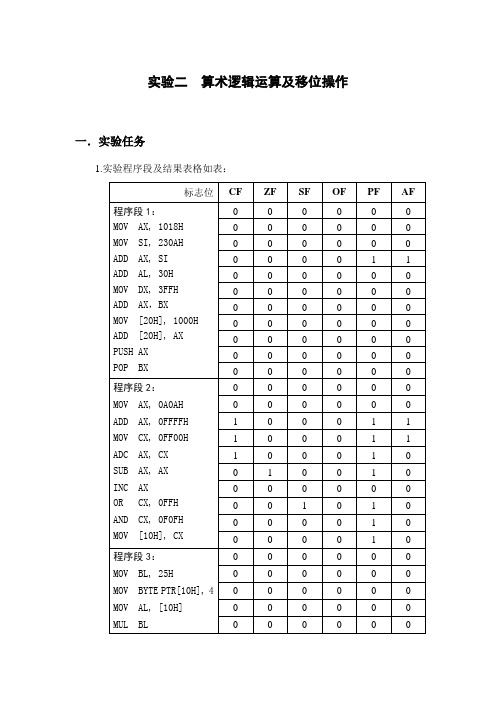

实验二 算术逻辑运算及移位操作

实验二算术逻辑运算及移位操作一.实验任务1.实验程序段及结果表格如表:分析:程序段1:MOV AX, 1018H ;AX←1018HMOV SI, 230AH ;SI←230AHADD AX, SI ;AX=3322H,低8位为00100010B,1的个数;为偶数,PF=1,同时D3向D4有进位发生,AF=1 ADD AL, 30H ;AX=3352H,低8位1个个数为奇数,PF=0 MOV DX, 3FFH ;DX←3FFHADD AX,BX ;AX=3352H,MOV [20H], 1000H ;[20H]←1000HADD [20H], AX ;[20H]=4352HPUSH AX ;POP BX ;BX=3352H程序段2:MOV AX, 0A0AH ;AX←0A0AHADD AX, 0FFFFH ;AX=0A09H,最高位进位CF=1,低8位1的;个数为偶数PF=1;D3向D4进位AF=1 MOV CX, 0FF00H ;CX←0FF00HADC AX, CX ;AX=090AH,最高位进位CF=1,低8位1的个;数为偶数PF=1SUB AX, AX ;AX=0,运算结果为零ZF=1INC AX ;AX=1HOR CX, 0FFH ;CX=0FFFFH,最高位为1,ZF=1,低8位1的;个数为偶数PF=1AND CX, 0F0FH ;CX=0F0FH,低8位1的个数为偶数PF=1MOV [10H], CX ;[10H]←0F0FH程序段3:MOV BL, 25H ;BL←25HMOV BYTE PTR[10H], 4 ;[10H]←04HMOV AL, [10H] ;AL←04HMUL BL ;AL=94H程序段4:MOV WORD PTR[10H],80H ;[10H]←0080HMOV BL, 4 ;BL←04HMOV AX, [10H] ;AX←0080HDIV BL ;AX=0020H程序段5:MOV AX, 0 ;AX←0000HDEC AX ;AX=0FFFFH,最高位为1,SF=1,低8;位1的个数为偶数PF=1,最高位向前、;D3向D4有借位,CF=1,AF=1 ADD AX, 3FFFH ;AX=3FFEH,D3向D4有进位,AF=1 ADD AX, AX ;AX=7FFCH,低8位1的个数为偶数,PF=1;D3向D4有进位,AF=1NOT AX ;AX=8003HSUB AX, 3 ;AX=8000H,低8位1的个数为偶数,PF=1;最高位为1,SF=1OR AX, 0FBFDH ;AX=0FBFDH,最高位为1,SF=1AND AX, 0AFCFH ;AX=0ABCDH,最高位为1,SF=1SHL AX,1 ;AX=579AH,低8位1的个数为偶数,PF=1,;算数结果溢出OF=1,最高位进位CF=1 RCL AX,1 ;AX=0AF35H,低8位1的个数为偶数,;PF=1,算数结果溢出OF=12.用BX寄存器作为地址指针,从BX所指的内存单元(0010H)开始连续存入三个无符号数(10H、04H、30H),接着计算内存单元中的这三个数之和,和放在0013H单元中,再求出这三个数之积,积放0014单元中。

《计算机组成原理》实验1寄存器试验,2运算器试验

实验指导书课程:计算机组成原理实验教师:班级:第一章系统概述1.1 实验系统组成第二章基础模块实验实验一寄存器实验实验目的:熟悉试验仪各部分功能。

掌握寄存器结构、工作原理及其控制方法。

实验内容:利用实验仪开关区上的开关sk23-sk16提供数据,其它开关做为控制信号,将数据通过DBUS写入OUT 寄存器,并将OUT寄存器的内容送往扩展区通过数码管和发光二极管显示。

实验原理:实验箱用74HC273 来构成寄存器。

(1)74HC273的功能如下:(2)实验箱中74HC273的连接方式:(3)实验逻辑框图12、打开实验仪电源,按CON单元的nRST按键,系统复位;如果EXEC键上方指示灯不亮,请按一次EXEC键,点亮指示灯,表示实验仪在运行状态。

3、利用开关和控制信号将数据通过DBUS写入OUT寄存器,并将OUT寄存器的内容送往扩展区通过数码管和发光二极管显示。

并写出将数据5FH写入OUT寄存器的操作过程。

实验二运算器实验实验目的:了解运算器的组成结构;掌握运算器的工作原理和控制方法。

实验内容:利用实验仪提供的运算器,通过开关提供数据信号,将数据写入寄存器A和寄存器B,并用开关控制ALU的运算方式,验证运算器的功能。

实验原理:(1)实验逻辑框图:信号说明:IN0~IN7:ALU数据输入信号ALU_D0~ALU_D7:ALU数据输出信号:寄存器A写信号,低电平有效。

当T1节拍信号到来,该信号有效时,IN0~IN7数据可以写入寄存器A。

:寄存器B写信号,低电平有效。

当T2节拍信号到来,该信号有效时,IN0~IN7数据可以写入寄存器B。

:ALU计算结果读出信号,当T3节拍信号到来,该信号有效时,ALU计算结果送往ALU_D0~ALU_D7。

S3~S0,CN_I:ALU运算控制信号,控制ALU的运算方法。

T1,T2,T3:三个节拍信号,高电平有效,由con区的uSTEP按键控制,在运行状态时,依次按下uSTEP 键会依次发出T1、T2、T3节拍。

实验二:算术逻辑运算和移位运算

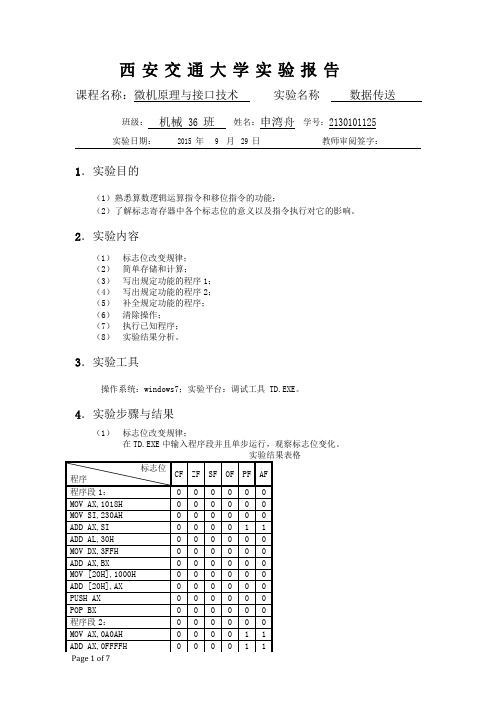

西安交通大学实验报告

课程名称:微机原理与接口技术实验名称数据传送

班级:机械36班姓名:申湾舟学号:2130101125

实验日期:2015年9 月29日教师审阅签字:1.实验目的

(1)熟悉算数逻辑运算指令和移位指令的功能;

(2)了解标志寄存器中各个标志位的意义以及指令执行对它的影响。

2.实验内容

(1)标志位改变规律;

(2)简单存储和计算;

(3)写出规定功能的程序1;

(4)写出规定功能的程序2;

(5)补全规定功能的程序;

(6)清除操作;

(7)执行已知程序;

(8)实验结果分析。

3.实验工具

操作系统:windows7;实验平台:调试工具TD.EXE。

4.实验步骤与结果

(1)标志位改变规律;

在TD.EXE中输入程序段并且单步运行,观察标志位变化。

(2)简单存储和计算;

(3)写出规定功能的程序1;

(4)写出规定功能的程序2;

(5)补全规定功能的程序;

(6)清除操作;

(7)执行已知程序;

(8)实验结果分析。

五、实验小结

Page2 of 7。

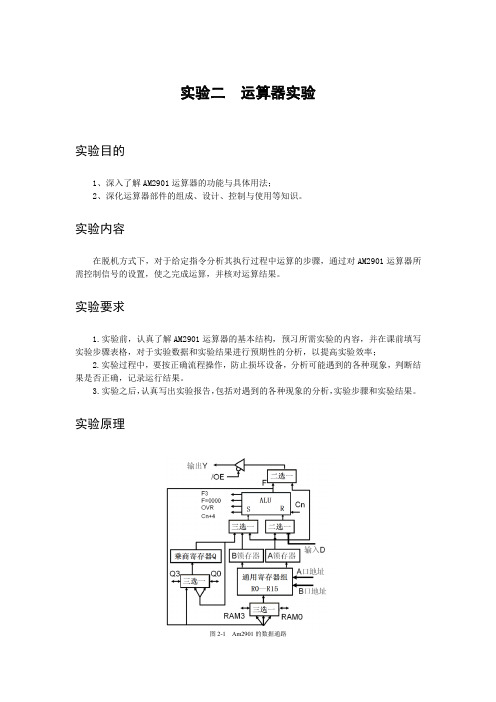

实验二 运算器实验

表2-4 最低进位Cin控制信号SCI SCI 0 0 1 1 0 1 0 1 Cin 0 1 C TCLK2 方波 典型指令 ADD、DEC INC、SUB ADC、SBB 本实验中不使用

表2-5 移位状态控制信号SSH SSH 0 0 1 1 0 1 0 1 左移 RAM0 0 C Q3 * Q0 * * F3 * 右移 RAM3 0 C CY F3⊕OV Q3 * * RAM0 RAM0 说明 补 0(逻辑左右移) 带进位移(循环移位) 带 Q 同时移位(乘除时) 补码右移

实验原理

图 2-1

Am2901 的数据通路

1、运算器数据通路

TEC-XP 教学机的运算器主要采用 4 片 Am2901 芯片级联组成,每片 Am2901 芯片实现 4 位运算,4 片芯片级联成 16 位的运算器。 Am2901 芯片的组成包括:1 个 4 位的算术逻辑单元 ALU、16 个 4 位的通用寄存器、1 个 4 位的乘商寄存器 Q 和若干个多路选择开关。Am2901 的数据通路如图 2-1 所示。 (1)算术逻辑单元 ALU ALU 有两个数据输入端 R 和 S。 R 端的数据来源有三个——寄存器 A、 数据线 D、 数值 0; S 端的数据来源有四个——寄存器 A、寄存器 B、乘商寄存器 Q、数值 0。在 RS 的各种组合 中除去没有意义的和重复的,只有 8 种有效的组合。ALU 的数据来源由控制信号 I2I1I0 决 定,其控制方式如表 2-1 所示。 ALU 可完成两个操作数的加、减、与、或、异或等多种操作,操作类型的控制有控制信 号 I5I4I3 决定,其控制方式如表 2-2 所示。ALU 若要实现乘除等其他运算,可使用串行算法 来完成。 ALU 的输出结果可保存到通用寄存器、乘商寄存器 Q,并且可以将其值乘除 2 之后再保 存,该过程控制由 I8I7I6 和 SSH 控制,其控制方式如表 2-3、表 2-5 所示。 ALU 根据其运算的结果会产生 4 个标志位——符号标志位 F3、零标志位 F=0、溢出标志 位 OVR 和进位标志位 Cn+4。ALU 运算后标志位设置可有多种不同的方式,其设置控制由 SST 控制信号决定,其控制方式如表 2-6 所示。 (2)通用寄存器组 Am2901 中的通用寄存器组是由 16 个寄存器构成, 具有双端口读写电路。 可以通过 A 口、 B 口输入的地址(4 位地址)选择寄存器,将其值送入 A、B 锁存器。其中 A 口地址指定的寄 存器是只读的,B 口地址指定的寄存器是可读写的。 A、 B 锁存器可作为 ALU 的输入数据, ALU 输出的结果值也可以保存到 B 口指定的寄存器 中,而且在写寄存器时,可以通过通用寄存器组入口处的三选一多路开关,选择写入 ALU 结果值,或其左移(乘 2) 、右移(除 2)之后的结果。 (3)乘商寄存器 乘商寄存器 Q 是为配合 ALU 的乘除运算而设置的。该寄存器输入端有三选一多路开关, 可选择 ALU 输出结果、 或乘商寄存器 Q 本身的内容作为其输入数据, 同时还可以将这两个输 入值左移(乘 2) 、右移(除 2)之后,再送入 Q 中。 (4)最低进位信号 Cin Am2901 的基本运算是加法电路, 其减法功能的实现是通过对减数求补而完成的。 因此, 在 ALU 运算时, 应使用 SCI 控制位设置最低进位信号 Cin 的状态, 具体控制方式见表 2-4。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验二算术运算实验一、实验目的1、掌握MASM for Windows 环境下的汇编语言编程环境使用;2、掌握汇编语言程序设计的基本流程及汇编语言中的二进制、十六进制、十进制、BCD码的表示形式;3、掌握汇编语言对多精度十六进制和十进制的编程方法及运算类指令对各状态标志位的影响及测试方法;4、掌握无符号数和有符号数运算区别及编程方法;5、掌握BCD码调整指令的使用方法二、软硬件实验环境1、硬件环境:惠普 64位一体化计算机及局域网;2、软件环境:windows 8,红蜘蛛管理系统, MASM for Windows。

三、实验基本原理算术运算实验需要对运行结果进行调试及查看状态字,其相关知识如下。

1)标志位在debug调试过程中,标志位用特殊符号表示的,其标志名和状态符号的对照表参照表 1 所示。

2)加减法指令ADD表示加法指令,ADC表示带进位加法指令,SUB表示减法指令,SBB表示带进位减法指令。

3)乘除法指令MUL表示无符号数乘法指令,IMUL表示带符号数乘法指令,DIV表示无符号数除法指令,IDIV 表示带符号数除法指令。

4)符号位扩展指令CBW表示从字节扩展到字的指令,CWD表示从字扩展到双字的指令。

5)BCD码的调整指令在进行十进制加减运算时,需要将数据用BCD码表示,还要考虑到是组合 BCD码还是非组合BCD码,组合BCD码是用一个字节表示两位十进制数,非组合BCD码是用一个字节表示一位十进制数,对于组合的 BCD码加减法运算其结果存放在 AL中。

组合的BCD码加法调整指令 DAA组合的BCD码减法调整指令 DAS非组合的BCD码加法调整指令 AAA非组合的BCD码减法调整指令 AAS乘法的非组合BCD码调整指令AAM除法的非组合BCD码调整指令AAD8088/8086指令系统提供了实现加、减、乘、除运算指令,可参照表2所示内容。

四、实验步骤与内容1)对于表格中三组无符号数,试编程求这三组数的指定运算结果,并考虑计算结果对标志寄存器中状态标志位的影响:①实验分析本实验要求简单,仅对指定三组数进行基本运算。

只需使用ADD SUB MUL DIV四个运算命令,并以MOV命令作为数值转移的手段即可。

运算结果和状态标志的情况可以通过debug 调试中的T命令进行逐步查看。

需要注意的主要有以下几点:1. 在进行加法和乘法运算时,会出现对高位的进位扩展。

因此,在记录结果的时候不能仅仅记录低2位(十六进制)的结果,应记录包含高位的完整结果;2. 在使用MUL和DIV命令时,语句的写法与ADD和SUB有区别;3. 除法运算既可得到商,也可得到余数,余数存在DL中;4. 查看结果时以三个语句为一次运算,输入三个T命令后的结果才是此次运算的结果。

②流程图③程序样例1、DATAS SEGMENT;此处输入数据段代码BUF1 DB 0ABH,64H,0A2HBUF2 DB 78H,5AH,3FHBUF3 DB 10 DUP⑺DATAS ENDSSTACKS SEGMENT;此处输入堆栈段代码STACKS ENDSCODES SEGMENTASSUME CS:CODES,DS:DATAS,SS:STACKS START:MOV AX,DATASMOV DS,AXMOV SI,0MOV CX,2Q1:MOV AH,0HMOV AL,BUF1[SI]MOV BL,ALMOV AL,BUF2[SI] ADD AX,BX ; 进行运算MOV BUF3[SI],ALADD SI,1HDEC CXJNZ Q1 ; 跳转再做一次第二组数的加法运算MOV AX,4CHINT 21HCODES ENDSEND START2、STACKS SEGMENT; 此处输入堆栈段代码STACKS ENDSCODES SEGMENTASSUME CS:CODES,DS:DATAS,SS:STACKS START:MOV AX,DATASMOV DS,AXMOV SI,0MOV CX,2Q1:MOV AH,0HMOV AL,BUF2[SI]MOV BL,ALMOV AL,BUF1[SI]MOV BUF3[SI],ALADD SI,1H ;do the operationDEC CXJNZ Q1 ;do it again with the second group of numbersMOV AX,4CHINT 21HCODES ENDSEND START 3、DATASSEGMENT;此处输入数据段代码BUF1 DB0ABH,64H,0A2HBUF2 DB78H,5AH,3FHBUF3 DB10 DUP?)DATASENDSSTACKSSEGMENT;此处输入堆栈段代码STACKSENDSCODES5EGMENTASSUMCS:CODES,DS:DATAS,SS:STACKSSTARTMOVXQATASMO\DS,AXMO\SI,2MOVCX,1Q1:MO\AH,0HMO\AL,BUF2[SI]MOV3L,ALMO\AL,BUF1[SI]DIV BXMOV3UF3[SI],ALADDSI,1H ;do the operationDECCXJNZ Q1 ;do it aga in with the sec ond group of nu mbers MO\AX,4CH INT 21H CODESENDS ENDSTART0ABH+78H64H+5AH0ABH-78Hkx^oGiaa HX=€Kf7a cx=oeez DX ^OOGO SP ^OQOG ar^eooo st =0000 1)1=0000 DS=a?7G ES=67t0 SS=flPFF CS=0771 [P=0915HU IIP El PL MS MA PE MC0771:001^ 89B4660O MOU [SUOOGGl^LDS :O00&-OG64H-5AH容HBOA Bx=ee» c )t=0S0i n^eeee^=0000 s 1=0091 vi=&&9&1£>(7旳0 SS-HI^K CS-^?1 IP-EW19 HW Ul 1 EL I'L MK HC FE AC3771;C0U S86HWOO MOU B[他66】,亂 »3 66^7^00A2H*3FHAX=Z7HE RX=fiflflF CX=fB01 DX=fiCMfl SP=fifiFM ST=(MfiZ DWfiflfiflDS-0770 ES-0760 SS-07bT CS-G771 IP-0015 NU UP El PL NZ HA FD PC £771^0015 G83i060t> HOU [3I*OO0®】jBL I>3;9060-060A2H/3FHX00GK BX^OCKF CX=t»01 DX=fc)tK4 时 GWW DS=O?7D ES=67EQ SS=0?bF CS-GP71 IP-001.9 U/71:f®l*J 8H84«)0a HUU L^l+WOhJ.ALBP^eeeo si^oeoz DI =OOOG )Hu UP EI PL ns HA RA HCKJ :4J0e8=002)在数据段定义了两个多精度的有符号16进制数,BUF1和BUF2求两数的和与差,并将计算值存放在BUF2为首地址的缓冲区中;同时将两组数据当作十进制数据来处理,再次求两数的和与差,并将结果存放在BUF2为首地址的缓冲区中。

试编程实现上述运算BUF1 DB 92H, 98H, 45H, 64H, 78HBUF2 DB 33H , 46H, 17H, 45H, 52H①实验分析本实验的思想是把这个两个多精度数进行按精度(每两位)进行运算,考虑进位与借位,每种运算都可以使用循环和带进位加法,或循环和带进位减法进行实现。

对于十进制数运算的要求,再辅以 DAA和DAS两种十进制调整命令,将结果变为BCD码即可。

本实验中需要注意的有以下几点:1. 本实验要求就过存入以 BUF2为首地址的缓冲区。

为在运算时保护BUF2的数据,需定义另一个存储空间来存储和BUF2 一样的数据;2. 在进行不同运算的间隙应当进行清除进位标志的操作,即使用CLC命令,避免上一运算的进位影响下一位运算的结果;3. DAA和 DAS都只能对AL里的结果转换为压缩 BCD码,因此十进制加减结果必须存入AL里,且转换为压缩 BCD码的结果要靠读取 AL来获得。

②程序流程图*③程序样例1、DATASSEGMENT; 此处输入数据段代码BUF1 DB92H,98H,45H,64H,78HBUF2 DB33H,46H,17H,45H,52HBUF3 DB10 DUP( ?)DATASENDSSTACKSSEGMENT; 此处输入堆栈段代码STACKSENDSCODESSEGMENTASSUMECS:CODES,DS:DATAS,SS:STACKS START:MOVAX,DATASMOVDS,AXMOVSI,0MOVCX,4MOVAH,00HQ1:MOVAL,BUF2[SI]MOVBL,ALMOVAL,BUF1[SI]ADCAL,BLMOVBUF2[SI],ALINC SIDECCXJNZ Q1MOVAX,4CHINT 21HCODESENDSEND START2、DATAS SEGMENT; 此处输入数据段代码BUF1 DB92H,98H,45H,64H,78HBUF2 DB33H,46H,17H,45H,52HBUF3 DB10 DUP( ?)DATASENDSSTACKSSEGMENT; 此处输入堆栈段代码STACKSENDSCODESSEGMENTASSUMECS:CODES,DS:DATAS,SS:STACKS START:MOVAX,DATASMOVDS,AXMOVSI,0MOVCX,4MOVAH,00HQ1:MOVAL,BUF2[SI]MOVBL,ALMOVAL,BUF1[SI]SBBAL,BLMOVBUF2[SI],ALINC SIDECCXJNZ Q1MOVAX,4CHINT 21HCODESENDSEND START3、DATASSEGMENT; 此处输入数据段代码BUF1 DB92H,98H,45H,64H,78HBUF2 DB33H,46H,17H,45H,52HBUF3 DB10 DUP( ?)DATASENDSSTACKSSEGMENT; 此处输入堆栈段代码STACKSENDSCODESSEGMENTASSUMECS:CODES,DS:DATAS,SS:STACKS START:MOVAX,DATASMOVDS,AXMOVSI,0MOVCX,4MOVAH,00HQ1:MOVAL,BUF2[SI] MOVBL,ALMOVAL,BUF1[SI]ADCAL,BLDAAMOVBUF2[SI],ALINC SIDECCXJNZ Q1MOVAX,4CHINT 21HCODESENDSEND START4、DATASSEGMENT; 此处输入数据段代码BUF1 DB92H,98H,45H,64H,78HBUF2 DB33H,46H,17H,45H,52HBUF3 DB10 DUP( ?) DATASENDSSTACKSSEGMENT; 此处输入堆栈段代码 STACKSENDSCODESSEGMENTASSUMECS:CODES,DS:DATAS,SS:STACKS START:MOVAX,DATASMOVDS,AXMOVSI,0MOVCX,4MOVAH,00HQ1:MOVAL,BUF2[SI]MOVBL,ALMOVAL,BUF1[SI]SBBAL,BLDAA。