门电路VHDL语言

第基本逻辑电路的VHDL设计PPT学习教案

5.1 组合逻辑电路设计

5.1.2 编码器设计 1. 8线-3线编码器的VHDL描述

本例中,运 用了case语 句完成了编 码器内部逻 辑结构设计, 其RTL电路 图如图5.4所 示。

图5.4 8线-3线编码器的RTL电路图

第12页/共99页

5.1 组合逻辑电路设计

5.1.2 编码器设计

(1)2线-4线译码器的VHDL设计 library ieee; ---【例5.5】 2线-4线译码器的VHDL代码 use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity decode_24 is port (a: in std_logic_vector(1 downto 0);

y1<=a and b; --构成与门

y2<=a or b;

--构成或门

y3<= not a ; --构成非门

y4<=a nand b; --构成与非门

y5<=a nor b; --构成异或门

y6<=not(a xor b); --构成异或非门

END;

第7页/共99页

5.1 组合逻辑电路设计

5.1.2 编码器设计 在数字系统中,常常需要将某信息变换为某一 特定的代码。把二进制码按一定的规律进行编 排,使每组代码具有特定的含义,称为编码。 具有编码功能的逻辑电路称为编码器。 编码器是将 2N 个分立的信息代码以N个二进 制码来表示。

WHEN "1101" => LED <= "1011110" ; --显示“D”

WHEN "1110" => LED <= "1111001" ; --显示“E” WHEN "1111" => LED <= "1110001" ; --显示“F”

8.VHDL语言基础(六)

双向和三态电路设计

1

双向和三态电路信号赋值

1、三态门设计

三态门,简称TSL(Three-state Logic)门,是在普 通门电路的基础上,附加使能控制端和控制电路构成 的。三态门除了通常的高电平和低电平两种输出状态 外,还有第三种输出状态-高阻态。处于高阻态时,电 路与负载之间相当于开路。

双向和三态电路信号赋值

2、双向端口设计 用INOUT模式设计双向端口也必须考虑三 态的使用,因为双向端口的设计与三态端口的 设计十分相似,都必须考虑端口的三态控制。 这是由于双向端口在完成输入功能时,必须使 原来呈输出模式的端口呈高阻态,否则,待输 入的外部数据势必会与端口处原有电平发生 “线与”,导致无法将外部数据正确地读入, 从而实现“双向”的功能。

24

双向和三态电路信号赋值

课堂练习:

修改8位4通道三态总线驱动器的第一 个设计,使其能综合出正确的电路。

25

2

双向和三态电路信号赋值

1、三态门设计

3

双向和三态电路信号赋值

1、三态门设计 三态门用途之一是实现总线传输。总线 传输的方式有两种,单向总线和双向总线。 单向总线方式下,要求只有需要传输信息的 那个三态门的控制端处于使能状态,其余各 门皆处于禁止状态。

4

双向和三态电路信号赋值

三态门实现总线传输的原理:

11

双向和三态电路信号赋值

2、双向端口设计

双向端口设计实例

12

双向和三态电路信号赋值

2、双向端口设计

双向端口设计实例

13

双向和三态电路信号赋值

14

双向和三态电路信号赋值

2、双向端口设计

分析:

q定义为双向端口,而x定义为三态控制输出口。 在q履行输入功能时,前者没有将其设定为高 阻态输出,即执行语句:q<=“ZZZZZZZZ”,从 而没有使q成为真正的双向端口,导致了错误 的逻辑电路; 执行语句:q<=“ZZZZZZZZ”,使q 在IF 语句 中有了完整的条件描述,从而克服了时序元件 的引入。

VHDL语言基础

3.1 概 述

3.1.5 VHDL与其他硬件描述语言的比较

VHDL: 具有较强的系统级抽象描述能力,适合行为级和RTL

级的描述,设计者可不必了解电路细节,所以工作比较 少,效率高。但对综合器的要求高,不易控制底层电路 的生成。IEEEE标准,支持广泛。

RTL: Register Translate Level (寄存器传输级)

with input select drive<=B”1111110” when 0, drive<=B”0110000” when 1, drive<=B”1101101” when 2, drive<=B”1111001” when 3, drive<=B”1111110” when 4, drive<=B”0110000” when 5, drive<=B”1101101” when 6, drive<=B”1111001” when 7,, drive<=B”0110000” when 8, drive<=B”1101101” when 9,

1、程序包说明(包首): 语法: package 程序包名 is { 包说明项 } end 程序包名;

包声明项可由以下语句组成: use 语句(用来包括其他程序包); 类型说明;子类型说明;常量说明;信号说明;

子程序说明;元件说明。

例:程序包说明:

2、程序包包体 程序包的内容:子程序的实现算法 包体的语法: package body 程序包名 is { 包体说明项 } end 程序包名;

如:一个可置数的16位计数器的电路原理图

3.1 概 述

用VHDL语言描述的可置数的16位计数器

3.1 概 述

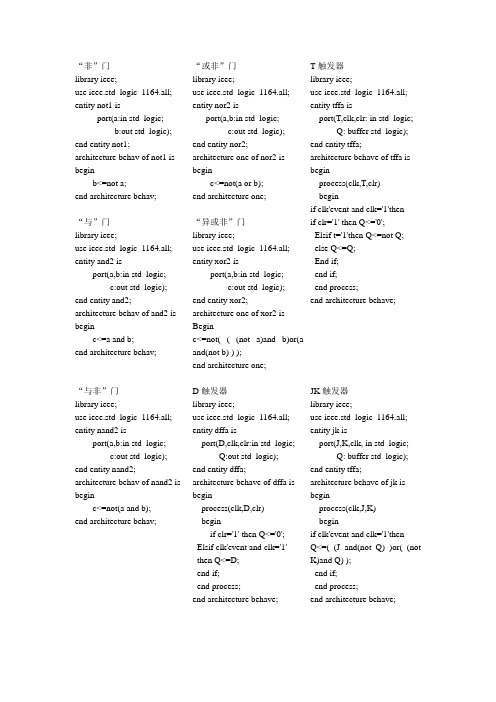

门电路VHDL语言

“非”门library ieee;use ieee.std_logic_1164.all; entity not1 isport(a:in std_logic;b:out std_logic); end entity not1; architecture behav of not1 is beginb<=not a;end architecture behav;“与”门library ieee;use ieee.std_logic_1164.all; entity and2 isport(a,b:in std_logic;c:out std_logic); end entity and2; architecture behav of and2 is beginc<=a and b;end architecture behav;“与非”门library ieee;use ieee.std_logic_1164.all; entity nand2 isport(a,b:in std_logic;c:out std_logic); end entity nand2; architecture behav of nand2 is beginc<=not(a and b);end architecture behav; “或非”门library ieee;use ieee.std_logic_1164.all;entity nor2 isport(a,b:in std_logic;c:out std_logic);end entity nor2;architecture one of nor2 isbeginc<=not(a or b);end architecture one;“异或非”门library ieee;use ieee.std_logic_1164.all;entity xor2 isport(a,b:in std_logic;c:out std_logic);end entity xor2;architecture one of xor2 isBeginc<=not( ( (not a)and b)or(aand(not b) ) );end architecture one;D触发器library ieee;use ieee.std_logic_1164.all;entity dffa isport(D,clk,clr:in std_logic;Q:out std_logic);end entity dffa;architecture behave of dffa isbeginprocess(clk,D,clr)beginif clr='1' then Q<='0';Elsif clk'event and clk='1'then Q<=D;end if;end process;end architecture behave;T触发器library ieee;use ieee.std_logic_1164.all;entity tffa isport(T,clk,clr: in std_logic;Q: buffer std_logic);end entity tffa;architecture behave of tffa isbeginprocess(clk,T,clr)beginif clk'event and clk='1'thenif clr='1' then Q<='0';Elsif t='1'then Q<=not Q;else Q<=Q;End if;end if;end process;end architecture behave;JK触发器library ieee;use ieee.std_logic_1164.all;entity jk isport(J,K,clk, in std_logic;Q: buffer std_logic);end entity tffa;architecture behave of jk isbeginprocess(clk,J,K)beginif clk'event and clk='1'thenQ<=( (J and(not Q) )or( (notK)and Q) );end if;end process;end architecture behave;移位寄存器library ieee;use ieee.std_logic_1164.all; useieee.std_logic_unsigned.all; entity reg isport(clk,din, dir: in std_logic;op: out std_logic);end entity reg;architecture a of reg issignal q:std_logic_vector(7 downto 0);beginprocess(clk)beginif clk'event and clk='1'thenif dir='0' then q(0)<=din;for i in 1 to 7 loopq(i)<=q(i-1);end loop;else q(7)<=din;for i in 1 to 7 loopq(i-1)<=q(i);end loop;end if;end if;end process;op<=q(7)when dir='0'elseq(0);end architecture a; 分频电路library ieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entity divf isport(clk: in std_logic;q: out std_logic);end entity divf;architecture a of divf issignal rst:std_logic;signal qn:std_logic_vector(2downto 0);beginprocess(clk,rst)beginif rst='1'then qn<="000";elsifclk'event and clk='1'thenqn<=qn+1;end if;end process;rst<='1'when qn=6 else'0';q<= qn(2);end architecture a;74LS160计数器library ieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entity ls74160 isport(clk,rst,ena,pe:instd_logic;d:in std_logic_vector(3 downto0);count:out std_logic_vector(3downto 0);co:out std_logic);end;architecture behave of ls74160issignal temp:std_logic_vector(3 downto 0);beginprocess(clk,rst,ena,pe)beginif (rst='1')thentemp<="0000";elsif(clk'eventandclk='1')thenif ena='1'thenif pe='1'then temp<=d;elsif temp="1001"thentemp<="0000";co<='1';else temp<=temp+1;co<='0';end if;end if;end if;end process;count<=temp;end behave;10进制计数器library ieee;use ieee.std_logic_1164.all; useieee.std_logic_unsigned.all; entity count10 isport(clk,rst,ena:in std_logi c; count:out std_logic_vector(3 downto 0);co:out std_logic);end count10;architecture behave of count10 issignal temp:std_logic_vector (3 downto 0);beginprocess(clk,rst,ena)beginif (rst='1')thentemp<="0000";elsif(clk'event and clk='1')then if ena='1'thenif(temp="1001")thentemp<="0000";co<='1';else temp<=temp+1;co<='0';end if;end if;end if;end process;count<=temp;end behave;输出逻辑宏单元(OLMC):输出引脚为12~19共8个。

vhdl课程设计三态门

vhdl课程设计三态门一、教学目标通过本节课的学习,学生应掌握三态门的基本原理和VHDL语言的编程方法,能够独立完成三态门电路的设计和验证。

具体目标如下:1.了解三态门的基本原理和功能;2.掌握VHDL语言的基本语法和编程方法;3.熟悉三态门电路的设计流程和验证方法。

4.能够运用VHDL语言编写三态门电路的代码;5.能够使用相关工具对三态门电路进行仿真和验证;6.能够分析并解决三态门电路设计中遇到的问题。

情感态度价值观目标:1.培养学生的创新意识和团队协作精神;2.增强学生对电子工程领域的兴趣和热情;3.培养学生严谨的科学态度和良好的沟通能力。

二、教学内容本节课的教学内容主要包括以下几个部分:1.三态门的基本原理和功能;2.VHDL语言的基本语法和编程方法;3.三态门电路的设计流程和验证方法;4.实际案例分析和相关练习。

具体的教学大纲如下:1.引言:介绍三态门的概念和应用场景;2.三态门的基本原理:讲解三态门的工作原理和电路结构;3.VHDL语言基础:介绍VHDL语言的基本语法和编程方法;4.三态门电路设计:讲解三态门电路的设计流程和注意事项;5.电路验证与仿真:介绍如何使用相关工具对三态门电路进行仿真和验证;6.案例分析与练习:分析实际案例,并进行相关练习。

三、教学方法为了提高学生的学习兴趣和主动性,本节课将采用以下教学方法:1.讲授法:讲解三态门的基本原理和VHDL语言的基本语法;2.讨论法:引导学生进行小组讨论,共同解决问题;3.案例分析法:分析实际案例,让学生更好地理解三态门电路的设计和验证;4.实验法:引导学生动手实践,完成三态门电路的设计和验证。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将准备以下教学资源:1.教材:提供相关教材,为学生提供理论知识的学习参考;2.参考书:提供相关参考书,帮助学生深入了解三态门电路的设计和验证;3.多媒体资料:制作课件和教学视频,为学生提供直观的学习资源;4.实验设备:准备实验设备,让学生能够动手实践,提高实际操作能力。

第2章 VHDL语言基础

End 实体名;

端口名

端口模式

数据类型

(2)ENTITY

端口模式(MODE)有以下几种类型: IN ;OUT;INOUT ;BUFFER 端口模式可用下图说明:(黑框代表一个设计或模块)

IN

OUT

BUFFER

INOUT

二输入与门电路设计范例

Library std; Use std.standard.all;

(4)CONFIGURATION定义区

定义格式: Configuration 配置名 of 实体名 is for 选用的结构体名 end for; end configuration 配置名 ;

二输入与门电路设计范例

a c

b电Leabharlann 真值表abc

0

0

0

1

0

0

0

1

0

1

1

1

二输入与门电路设计范例

Architecture Na of and2 is

‘1’; 符号<=为信号直接赋值符。

End Na;

--结构体Na

Architecture Nb of and2 is

Begin

c <= a and b;

--and 为逻辑与操作

End Nb; --结构体Nb

Library ieee; Use ieee.std_logic_1164.all;

Entity half_adder is Port( x,y : in std_logic;sum,carry : out hlf_adder); End half_adder;

(4)CONFIGURATION定义区

一个完整VHDL电路设计必须有一个实体 和对应的结构体,即实体和结构体对构成一个 完整的VHDL设计。

数字逻辑第7章 VHDL语言基础

主要用于描述数字逻辑电路的结构、行为、功

能和接口

前言

举例二路选择器 VHDL描述 库的调用 传统描述方式 VHDL描述

LIBRARY IEEE;

用与门、非门、 ENTITY MUX2 底 层 或 门 等 具 体 IS 器件来组成

结构体描述

ARCHITECTURE behav OF MUX2 IS

程序包调用 BEGIN

ARCHITECTURE 结构体名 OF 实体号名 IS 定义语句] 信号(signal); [定义语句] 信号(signal); 常数(constant); 常数(constant); 并行处理是 并行处理是 数据类型(type); 数据类型(type VHDL的特点 ); 的特点 函数(function); 函数(function); 元件(component) 元件(component)等; BEGIN 并行处理语句] [并行处理语句]; 结构体名; END 结构体名;

vhdl语言

VHDL语言简介VHDL(VHSIC Hardware Description Language)即可高速集成电路硬件描述语言,是一种用于描述数字系统和电路的硬件描述语言。

它在1981年由美国国防部的高速集成电路联合委员会(VHSIC)开发,用于设计大规模集成电路。

VHDL是一种面向对象的语言,可以用于描述各种数字系统,从简单的逻辑门到复杂的处理器。

它提供了丰富的语法和语义,使得设计人员可以准确地描述他们的电路和系统。

VHDL的优势VHDL作为一种硬件描述语言,在数字系统设计中具有许多优势。

1.可重用性:VHDL允许设计人员创建可重用的模块和子系统,这些模块和子系统可以在不同的项目中重复使用,提高了设计效率和可维护性。

2.仿真和验证:VHDL具有强大的仿真和验证能力,可以在设计之前对系统进行全面的仿真和验证。

这有助于检测和纠正潜在的问题,并确保系统在硬件实现之前达到预期的功能。

3.抽象级别:VHDL允许设计人员在不同的抽象级别上描述系统,从高级的行为级别到底层的结构级别。

这使得设计人员可以根据需要在不同的级别上工作,并且可以更容易地进行系统级别的优化。

4.灵活性和可扩展性:VHDL支持灵活的设计方法和工作流程,并允许设计人员在设计过程中进行迭代和修改。

它还可以与其他常用的设计工具和方法集成,以满足特定的需求。

VHDL语言的基本结构VHDL语言由模块、实体、架构以及信号和过程等基本元素组成。

模块(Module)模块是VHDL中描述数字系统的最基本单位。

一个模块可以包含多个实体和架构,并通过连接信号进行通信。

每个模块都有一个顶层实体和一个或多个架构。

实体(Entity)实体是描述模块的接口和行为的抽象。

它定义了输入输出端口,以及模块对外部环境的接口。

一个实体可以有一个或多个架构。

架构(Architecture)架构描述模块的具体行为和内部结构。

它定义了模块的内部信号和过程,以及对外部信号和过程的接口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

“非”门library ieee;use ieee.std_logic_1164.all; entity not1 isport(a:in std_logic;b:out std_logic); end entity not1; architecture behav of not1 is beginb<=not a;end architecture behav;“与”门library ieee;use ieee.std_logic_1164.all; entity and2 isport(a,b:in std_logic;c:out std_logic); end entity and2; architecture behav of and2 is beginc<=a and b;end architecture behav;“与非”门library ieee;use ieee.std_logic_1164.all; entity nand2 isport(a,b:in std_logic;c:out std_logic); end entity nand2; architecture behav of nand2 is beginc<=not(a and b);end architecture behav; “或非”门library ieee;use ieee.std_logic_1164.all;entity nor2 isport(a,b:in std_logic;c:out std_logic);end entity nor2;architecture one of nor2 isbeginc<=not(a or b);end architecture one;“异或非”门library ieee;use ieee.std_logic_1164.all;entity xor2 isport(a,b:in std_logic;c:out std_logic);end entity xor2;architecture one of xor2 isBeginc<=not( ( (not a)and b)or(aand(not b) ) );end architecture one;D触发器library ieee;use ieee.std_logic_1164.all;entity dffa isport(D,clk,clr:in std_logic;Q:out std_logic);end entity dffa;architecture behave of dffa isbeginprocess(clk,D,clr)beginif clr='1' then Q<='0';Elsif clk'event and clk='1'then Q<=D;end if;end process;end architecture behave;T触发器library ieee;use ieee.std_logic_1164.all;entity tffa isport(T,clk,clr: in std_logic;Q: buffer std_logic);end entity tffa;architecture behave of tffa isbeginprocess(clk,T,clr)beginif clk'event and clk='1'thenif clr='1' then Q<='0';Elsif t='1'then Q<=not Q;else Q<=Q;End if;end if;end process;end architecture behave;JK触发器library ieee;use ieee.std_logic_1164.all;entity jk isport(J,K,clk, in std_logic;Q: buffer std_logic);end entity tffa;architecture behave of jk isbeginprocess(clk,J,K)beginif clk'event and clk='1'thenQ<=( (J and(not Q) )or( (notK)and Q) );end if;end process;end architecture behave;移位寄存器library ieee;use ieee.std_logic_1164.all; useieee.std_logic_unsigned.all; entity reg isport(clk,din, dir: in std_logic;op: out std_logic);end entity reg;architecture a of reg issignal q:std_logic_vector(7 downto 0);beginprocess(clk)beginif clk'event and clk='1'thenif dir='0' then q(0)<=din;for i in 1 to 7 loopq(i)<=q(i-1);end loop;else q(7)<=din;for i in 1 to 7 loopq(i-1)<=q(i);end loop;end if;end if;end process;op<=q(7)when dir='0'elseq(0);end architecture a; 分频电路library ieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entity divf isport(clk: in std_logic;q: out std_logic);end entity divf;architecture a of divf issignal rst:std_logic;signal qn:std_logic_vector(2downto 0);beginprocess(clk,rst)beginif rst='1'then qn<="000";elsifclk'event and clk='1'thenqn<=qn+1;end if;end process;rst<='1'when qn=6 else'0';q<= qn(2);end architecture a;74LS160计数器library ieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entity ls74160 isport(clk,rst,ena,pe:instd_logic;d:in std_logic_vector(3 downto0);count:out std_logic_vector(3downto 0);co:out std_logic);end;architecture behave of ls74160issignal temp:std_logic_vector(3 downto 0);beginprocess(clk,rst,ena,pe)beginif (rst='1')thentemp<="0000";elsif(clk'eventandclk='1')thenif ena='1'thenif pe='1'then temp<=d;elsif temp="1001"thentemp<="0000";co<='1';else temp<=temp+1;co<='0';end if;end if;end if;end process;count<=temp;end behave;10进制计数器library ieee;use ieee.std_logic_1164.all; useieee.std_logic_unsigned.all; entity count10 isport(clk,rst,ena:in std_logi c; count:out std_logic_vector(3 downto 0);co:out std_logic);end count10;architecture behave of count10 issignal temp:std_logic_vector (3 downto 0);beginprocess(clk,rst,ena)beginif (rst='1')thentemp<="0000";elsif(clk'event and clk='1')then if ena='1'thenif(temp="1001")thentemp<="0000";co<='1';else temp<=temp+1;co<='0';end if;end if;end if;end process;count<=temp;end behave;输出逻辑宏单元(OLMC):输出引脚为12~19共8个。

输出逻辑宏单元包括或门、异或门、D触发器、4个4选1多路选择器、输出缓冲器等。

BCD—7段译码library ieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entity decord7 isport(a:in std_logic_vector(3downto 0);q:out std_logic_vector(6downto 0);en:out std_logic);end decord7;architecture behave of decord7isbeginprocess(a)begincase a(3 downto 0) iswhen"0000"=>q<="0111111";when"0001"=>q<="0000110";when"0010"=>q<="1011011";when"0011"=>q<="1001111";when"0100"=>q<="1100110";when"0101"=>q<="1101101";when"0110"=>q<="1111101";when"0111"=>q<="0000111";when"1000"=>q<="1111111";when"1001"=>q<="1101111";when others=>q<="0000000";end case;end process;en<='0';end behave;输入缓冲器:输入端为引脚2~9,共有8个输入。