专用集成电路设计

MIC总线控制器远程模块专用集成电路的设计与应用

1 引 言

MI ME C M itr c hp — m hpee C( P A ne ae c i f u il d x

ee tiap we o to n mo i r ma a e n i — lcrc l o r c n r l a d nt / n g me t n o

信号

输 出

健号

输入

信号

输 出 健号

输入 信号

圈 1 MZ 线连 接 圈 C总

M C总线系统将诸如 M L T I I—s D一 15 B这 53

信周期 。所有远程模块将接收和判断这个命令 , 硬件连接地址与命令中特定模块地址相同的模块

将立即通过 串行总线 传 回相应 的响应信息 , 总线

维普资讯

第2 5卷第 3期 20 0 7年 9月

蒸

J C t NGDI I IZ ANLU ONG T XUN

Vo . 5 N0. 12 3

Sp2 0 e .07

MC总线控制器远程模块专用集成电路的设计与应用 I

汪 健

( 中国兵器 工业 第 24研 究所 1

种基于命令/ - 响应通信方式 的数据 总线系统大部

分的软件和硬件功能集成到 M C控制器芯片中, I

而且远程模块不需要微处理器来控制通信或者执 行输 输出功能 , 使得 通信协议 的使 用非 常简 单, 不需要系统软件执行费时任务, 例如定时器控

制、 响应校验 、 或者其他通信管理等。总线控制器

蚌埠

234 ) 30 2

摘

要

M C总线是专 门为解决恶劣的军事环境 中电力及数据分配和管理 问题 而开发的串行现场 I

专用集成电路6-Calibre和Diva

6、版图验证工具 、

Outline

IC设计的基本知识 版图验证工具Diva 版图验证工具Calibre

1、IC设计的基本知识

ASIC设计方法分类:

定制 (Custom) ) 全定制 (Full-Custum) ) 基于包 (Cell-Based) ) 门陈列 (Gate Arrays) ) 线性陈列 (Linear Arrays) )

选择PEX运行设置文件pex_runset,操作步骤与DRC, LVS相同。

输出格式设为CALIBREVIEW

Run PEX运行三次

第一次,这里三个选项都选中, 第一次,这里三个选项都选中, 出现Calibre 出现Calibre finished with Error:SIGABRT错误 Error:SIGABRT错误 第二次,选中第二、三个选项, 第二次,选中第二、三个选项, 出现Calibre 出现Calibre finished with Error:SIGABRT错误 Error:SIGABRT错误 第三次, 第三次,仅选中最后一个选项

选择你的LVS运行目录

然后,保存lvs_runset文件,操作方法与前面保存drc_runset 文件一模一样。

这步操作是选择 从电路导出网表, 让这个导出的网表 与版图生成的网表 进行LVS。

然后就可以点“Run LVS”运行LVS。

LVS通过

(3)寄生参数抽取 (3)寄生参数抽取 PEX

规则文件同LVS 规则文件同LVS

反相器的抽取视图

(3)版图与电路对照验证LVS

LVS的任务是证明这个版图就是想要的那一个,也 就是说证明这个版图实现的功能与图

diva的LVS规则文件 的 规则文件 工艺库名

专用集成电路设计方法

专用集成电路设计方法

专用集成电路(ASIC)设计方法是一种用于开发和设计定制化电路的方法。

ASIC 设计通常用于特定的应用领域,例如通信、计算机、汽车等,因为它们能够提供高性能、低功耗和高度集成的解决方案。

而ASIC设计的方法主要包括以下几个步骤:

1. 需求分析:该阶段通过与客户和应用领域专家的沟通,确定ASIC的功能和性能要求,以及其应用领域的特殊需求。

2. 架构设计:在这个阶段,设计团队将根据需求分析的结果,确定ASIC的整体架构,包括功能模块组成、接口设计等。

这个阶段的关键是对系统级需求和资源进行平衡,以确保设计的可行性和性能优化。

3. 逻辑设计:逻辑设计阶段主要涉及到对ASIC的功能、功能模块和电路结构进行设计。

这个阶段使用硬件描述语言(HDL)进行设计,并进行逻辑仿真和验证。

4. 物理设计:物理设计阶段主要涉及将逻辑设计转化为物理结构,包括布局和布线。

这个阶段需要考虑到电路的功率、时序和面积等方面的优化。

5. 验证与测试:验证和测试阶段是为了确保ASIC设计的正确性和功能性。

这个阶段包括功能仿真、时序仿真、门级仿真和芯片级仿真等。

同时还需要进行物理

验证和测试,以验证芯片的性能和可靠性。

6. 制造:制造阶段是将ASIC设计转化为实际的芯片产品的过程。

这个阶段包括芯片制造、封装和测试等。

ASIC的制造过程需要符合特定的标准和流程,以确保芯片的质量和可靠性。

以上是一般ASIC设计方法的大致流程。

在实际应用中,可能会根据不同的需求和项目而有所调整。

同时,ASIC设计方法也在不断地演变和发展,以满足新的技术和市场需求。

复旦大学专用集成电路-国家重点实验室

复旦大学专用集成电路与系统国家重点实验室是国内集成电路设计领域唯一的国家重点实验室。

实验室的软、硬装备达到国际90代年的水平,具备深亚微米芯片的设计和研究能力,是国内最有影响的集成电路设计开发基地,也是国内集成电路设计人才培养最有实力的基地。

实验室面积超过2200平方米,拥有国际一流的软硬件设计环境。

▪50台先进的计算机工作站Sun Ultra 10, 60;▪Pentium IV 100台;▪系统设计软件Synopsys, Cadence;▪亚微米芯片设计软件Cadence, Avanti;▪SP设计软件COSSAP, DSP station;▪功耗分析软件Power Mill;▪数字电路测试仪;▪HP 82000逻辑分析仪;▪HP测试分析探针台2台;▪HP高频示波器等测试仪器;▪其它软件Saber、Hspice、Xillinx、Altera等。

专用集成电路与系统国家重点实验室“专用集成电路与系统”国家重点实验室是于1992年由国家计委批世界银行贷款筹建的,总贷款额为160万美元。

1995年9月通过国家2002年再次通过评估,是我国目前唯一的专门从事集成电路设计研家重点实验室。

实验室有固定人员60名,其中45岁以下的中青年教师约占70%,士学位的占中青年教师的70%以上。

实验室以微电子技术、计算机辅助技术和电路系统理论方法为基础多学科结合的综合优势,围绕集成电路这一关系到我国信息化发展的键问题,开展专用集成电路设计方法与系统集成创新技术的研究。

目决从系统到集成电路制造工艺之间所遇到的前沿理论问题和关键技术开发具有自主知识产权的用于先进电子系统的芯片技术,成为我国集设计研究、产业发展以及高层次人才培养的最重要基地之一。

近年来,实验室始终瞄准国际SoC发展前沿,面向国家重大需求国民经济主战场,紧紧围绕实验室的学术研究方向,共承担了各类研究课题274项,总经费5595.79万。

其中86 973计划、国家自然科学基金、国家攻关计划以及省部委项目共计146项,经费3404.6万元;与几十家国内外单位和企业合作完成研究课题128项,经费2191.19万元,创造了良好的社会效益和巨大的经济效益。

专用集成电路CPU设计工具问题小议

专用集成电路CPU设计工具问题小议摘要:主要介绍了专用集成电路cpu计算机辅助设计工具的方法和步骤、设计过程中遇到的问题和解决方案,以及用cad设计新型微处理器应该注意的问题。

关键词:专用集成电路计算机辅助设计工具新型微处理器中图分类号:tn401 文献标识码:a 文章编号:1672-3791(2012)09(a)-0117-01新型微处理器设计必须努力达到在可接受的耗电量和芯片面积条件下的最高性能。

因此,芯片工具方法论通常具有挑战性和两个突出的特点:基本构件是晶体管,晶体管的尺寸可以单独地控制并能够和其它的晶体管组成不同的逻辑族;物理设计是分块的、详细计划的,而且在实施细节被设计出来之前就要提交。

1 微结构设计和电路可行性研究工具微结构设计的目标是建立一个性能模型和一个微结构文档,该文档包含细致的流程图和具有重要性能的通路。

该性能模型通常被高度参数化以便在主要的结构特性上施行中产生更多“如果-怎么样”的测试。

该设计过程完全是人工的。

该性能模型通常用高级编程语言写成,所以这里仅需要一个好的文本编辑器和语言编译器。

对于微结构文档的编写,通常具有画图功能的字处理器就足够了。

电路可行性研究的目标是确保微结构可以实现。

基于微结构的知识,电路设计者将芯片分成许多块并创建一个芯片级的底层计划来涵盖这些模块。

多种分配电源的计划被测试之后,选择最优者。

电路可行性研究层次的基本工具是:电路图编辑器和连线器、布线编辑器和寄生抽取器、spice仿真器。

绝大多数商品化的电路图编辑器、布线编辑器、寄生抽取器和spice仿真器都有电路可行性研究能力。

为了方便芯片底层计划的设计,上面的工具能够执行“如果-怎么样”的测试、芯片分区、模块管脚布局和综合网络连线,并具有许多不同的用户控制算法。

然而,由于底层计划创建于设计的最早阶段,这些工具在操作部分完成设计数据。

绝大多数的商业化工具都没有为此目的而设计。

为了确保整体时序说明的完整性,一个用于检查高层模块之间时序和整体网络线路一致性的工具是必须的。

专用集成电路设计实用教程第二版

专用集成电路设计实用教程第二版

《专用集成电路设计实用教程第二版》是一本关于专用集成电路设计的实用教程。

本书系统地介绍了专用集成电路的基本概念、设计原理和设计方法。

全书内容主要分为六个部分。

第一部分介绍了专用集成电路设计的基本概念和设计流程。

包括电路设计的基本概念、电路设计的流程和方法等内容。

通过这一部分的学习,读者可以初步了解到专用集成电路设计的基本思想和方法。

第二部分介绍了专用集成电路设计的基本技术。

包括逻辑门电路设计、通用门电路设计、存储器电路设计等内容。

通过这一部分的学习,读者可以掌握专用集成电路设计的基本技术。

第三部分介绍了专用集成电路设计的高级技术。

包括电源管理电路设计、时钟管理电路设计、信号处理电路设计等内容。

通过这一部分的学习,读者可以进一步提升专用集成电路设计的技术水平。

第四部分介绍了专用集成电路设计的验证与测试。

包括电路验证的基本原理、电路测试的基本原理和方法等内容。

通过这一部分的学习,读者可以了解专用集成电路设计的验证与测试的相关知识。

第五部分介绍了专用集成电路设计的优化与改进。

包括电路仿真与优化、电路布局与布线、故障分析与调试等内容。

通过这一部分的学习,读者可以学习如何优化和改进专用集成电路设

计。

第六部分介绍了专用集成电路设计的应用实例。

通过具体的案例分析,读者可以学习如何将专用集成电路设计应用到实际项目中。

总之,《专用集成电路设计实用教程第二版》是一本系统、全面介绍专用集成电路设计的实用教材,适合专业学习和工程实践。

专用集成电路Assignment+3

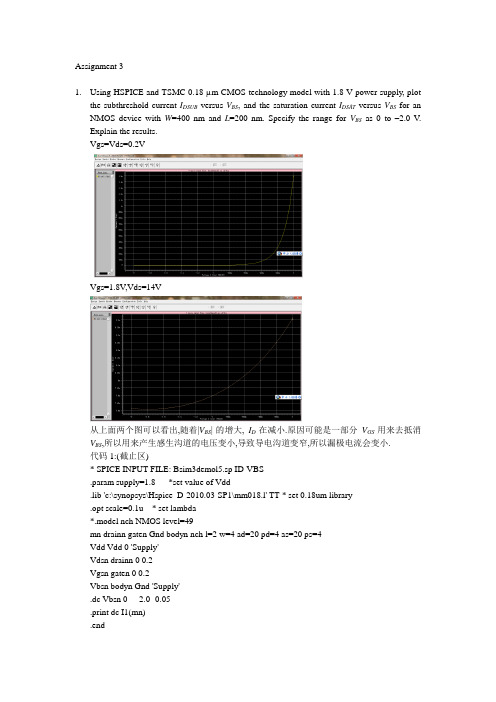

Assignment 3ing HSPICE and TSMC 0.18 µm CMOS technology model with 1.8 V power supply, plotthe subthreshold current I DSUB versus V BS, and the saturation current I DSAT versus V BS for an NMOS device with W=400 nm and L=200 nm. Specify the range for V BS as 0 to –2.0 V.Explain the results.Vgs=Vds=0.2VVgs=1.8V,Vds=14V从上面两个图可以看出,随着|V BS|的增大,I D在减小.原因可能是一部分V GS用来去抵消V BS,所以用来产生感生沟道的电压变小,导致导电沟道变窄,所以漏极电流会变小.代码1:(截止区)* SPICE INPUT FILE: Bsim3demol5.sp ID-VBS.param supply=1.8 *set value of Vdd.lib 'c:\synopsys\Hspice_D-2010.03-SP1\mm018.l' TT * set 0.18um library.opt scale=0.1u * set lambda*.model nch NMOS level=49mn drainn gaten Gnd bodyn nch l=2 w=4 ad=20 pd=4 as=20 ps=4Vdd Vdd 0 'Supply'Vdsn drainn 0 0.2Vgsn gaten 0 0.2Vbsn bodyn Gnd 'Supply'.dc Vbsn 0 -2.0 -0.05.print dc I1(mn).end代码1:(饱和区)* SPICE INPUT FILE: Bsim3demol5.sp ID-VBS.param supply=1.8 *set value of Vdd.lib 'c:\synopsys\Hspice_D-2010.03-SP1\mm018.l' TT * set 0.18um library.opt scale=0.1u * set lambda*.model nch NMOS level=49mn drainn gaten Gnd bodyn nch l=2 w=4 ad=20 pd=4 as=20 ps=4Vdd Vdd 0 'Supply'Vdsn drainn 0 14Vgsn gaten 0 1.8Vbsn bodyn Gnd 'Supply'.dc Vbsn 0 -2.0 -0.05.print dc I1(mn).ending HSPICE and TSMC 0.18 um CMOS technology model with 1.8 V power supply, plotlog I DS versus V GS while varying V DS for an NMOS device with L=200 nm, W=800 nm and a PMOS with L=200 nm, W= 2 µm. Which device exhibits more DIBL(Drain-Induced Barrier Lowering)? Why do PMOS transistors typically have a higher V T than NMOS transistors?阈值电压和以下几个因素有关:栅电极材料类型,栅氧化层厚度,衬底掺杂浓度,栅氧化层层中的电荷密度等相关,一般工艺中N/P MOS的栅氧化层厚度tox都是相同的,栅电极材料类型也相同,栅氧化层层中的电荷密度也相同,但是衬底浓度却不一样,NMOS直接做在Psub外延P-epi上面,而PMOS 做在P-epi的NWELL上面,所以NWELL的杂志浓度比P-epi跟大一些,衬底浓度越大,对应MOS管的阈值电压也越大,所以一般PMOS的阈值电压都要比NMOS要更大一些。

asic 芯片

asic 芯片ASIC芯片(Application-Specific Integrated Circuit)是一类专用集成电路芯片,也称为定制芯片。

相比于通用集成电路(如处理器、存储器等),ASIC芯片是根据特定的应用需求而设计的,因此能够提供更高的性能和更低的功耗。

ASIC芯片在各个领域都得到广泛应用,包括通信、计算机、工业控制、汽车、医疗等。

下面将从设计流程、应用案例和未来发展趋势三个方面来介绍ASIC芯片。

首先是ASIC芯片的设计流程。

ASIC芯片的设计是一个复杂的过程,通常分为前端设计和后端设计两个阶段。

前端设计主要包括功能设计、电路设计和逻辑验证。

功能设计是根据需求规格书确定芯片的功能模块和接口,并进行功能分析;电路设计则是根据功能要求,设计电路的结构和参数,如时钟、存储器、逻辑门等;逻辑验证是通过仿真和验证工具对设计进行全面测试,以确保功能的正确性。

后端设计主要包括物理设计、布局设计和版图设计。

物理设计是将逻辑电路映射到实际的物理器件,进行数电转换、时序优化等操作;布局设计则是确定各个电路模块的位置和相互连接方式;版图设计则是将布局设计结果转化为最终的芯片版图。

完成设计后,还需要进行流片和封装测试。

流片是指将版图发送给芯片制造企业,进行样片生产;封装测试则是将芯片封装为最终的芯片模块,并经过各种测试和验收,确保芯片的可靠性和稳定性。

其次是ASIC芯片的应用案例。

ASIC芯片广泛应用于各个领域,以下以通信和计算机领域为例介绍两个典型的应用案例。

在通信领域,ASIC芯片被广泛用于移动通信设备中,如手机、路由器和基站等。

它们能够提供高效的信号处理、数据传输和接口控制功能,满足不同通信标准和需求。

例如,LTE芯片可以实现高速无线数据传输,提供更快的网络连接速度;而基站芯片能够实现大规模的无线通信覆盖,提供更好的通信服务质量。

在计算机领域,ASIC芯片被广泛用于数据中心和云计算设备中。

它们能够提供高性能的计算、存储和网络功能,满足大规模数据处理和分析的需求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

专用集成电路课程设计简易电子琴通信工程学院011051班侯珂01105023目录1 引言 (1)1.1设计的目的 (1)1.2设计的基本内容 (2)2 EDA、VHDL简介 (2)2.1EDA技术 (2)2.2硬件描述语言——VHDL (3)2.2.1 VHDL的简介 (3)2.2.2 VHDL语言的特点 (3)2.2.3 VHDL的设计流程 (4)3 简易电子琴设计过程 (5)3.1简易电子琴的工作原理 (5)3.2简易电子琴的工作流程图 (5)3.3简易电子琴中各模块的设计 (6)3.3.1 乐曲自动演奏模块 (7)3.3.2 音调发生模块 (8)3.3.3 数控分频模块 (9)3.3.4 顶层设计 (10)4 系统仿真 (12)5 结束语 (14)收获和体会.................................................................................................. 错误!未定义书签。

参考文献 .. (15)附录 (16)1 引言我们生活在一个信息时代,各种电子产品层出不穷,作为一个计算机专业的学生,了解这些电子产品的基本组成和设计原理是十分必要的,我们学习的是计算机组成的理论知识,而课程设计正是对我们学习的理论的实践与巩固。

本设计主要介绍的是一个用超高速硬件描述语言VHDL设计的一个具有若干功能的简易电子琴,其理论基础来源于计算机组成原理的时钟分频器。

摘要本系统是采用EDA技术设计的一个简易的八音符电子琴,该系统基于计算机中时钟分频器的原理,采用自顶向下的设计方法来实现,它可以通过按键输入来控制音响。

系统由乐曲自动演奏模块、音调发生模块和数控分频模块三个部分组成。

系统实现是用硬件描述语言VHDL按模块化方式进行设计,然后进行编程、时序仿真、整合。

本系统功能比较齐全,有一定的使用价值。

关键字电子琴、EDA、VHDL、音调发生1.1 设计的目的本次设计的目的就是在掌握计算机组成原理理论的基础上,了解EDA技术,掌握VHDL硬件描述语言的设计方法和思想,通过学习的VHDL语言结合电子电路的设计知识理论联系实际,掌握所学的课程知识,例如本课程设计就是基于所学的计算机原理中的时钟分频器和定时器的基础之上的,通过本课程设计,达到巩固和综合运用计算机原理中的知识,理论联系实际,巩固所学理论知识,并且提高自己通过所学理论分析、解决计算机实际问题的能力。

1.2 设计的基本内容基于MAX+PLUS平台,运用VHDL语言对简易电子琴的各个模块进行设计,并使用EDA 工具对各模块进行仿真验证。

本设计包含如下三个模块:乐曲自动演奏模块,音调发生模块,数控分频模块,最后把各个模块整合后,通过电路的输入输出对应关系连接起来。

2 EDA、VHDL简介2.1 EDA技术EDA技术是在电子CAD技术基础上发展起来的计算机软件系统,有狭义与广义之分,本设计讨论的是狭义的EDA技术。

它是指以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成软件方式设计的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿真,直到对于特定目标芯片的适配编译、逻辑映射、逻辑下载等工作,最终形成集成电子系统或专用集成芯片的一门新技术。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。

本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。

2.2 硬件描述语言——VHDL2.2.1 VHDL的简介VHDL是一种用来描述数字逻辑系统的“编程语言”它的全名是Very-High-Speed Integrated Circuit HardwareDescription Language,诞生于1982年。

1987年底,VHDL被IEEE(The Institute of Electrical and Electronics Engineers)和美国国防部确认为标准硬件描述语言。

它源于美国政府于1980年开始启动的超高速集成电路计划,VHDL主要用于描述数字系统的结构、行为、功能和接口。

除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。

VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件、一个电路模块或一个系统)分成外部(或称可是部分,即端口)和内部(或称不可视部分,既设计实体的内部功能和算法完成部分)两部分。

在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。

这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

应用VHDL进行工程设计的优点是多方面的。

VHDL的应用必将成为当前以及未来EDA解决方案的核心,更是整个电子逻辑系统设计的核心。

2.2.2 VHDL语言的特点(1)VHDL具有更强的行为描述能力,从而决定了他成为电子工程领域事实上通用的硬件描述语言。

强大的行为描述能力是避开具体的器件结构,从逻辑行为上描述和设计大规模电子系统的重要保证。

(2)VHDL语句的行为描述能力和程序结构,决定了他具有支持大规模设计的分解和已有设计的再利用功能。

高效、高速完成符合市场需求的必须有多人甚至多个代发组共同并行工作才能实现的大规模系统设计。

VHDL中设计实体的概念、程序包的概念、设计库的概念为设计的分解和并行工作提供了有利的支持。

(3)VHDL丰富的仿真语句和库函数,使得在任何大系统的设计早期,就能查验设计系统的功能可行性,随时可对设计进行仿真模拟,使设计者对整个工程的结构和功能可行性做出判断。

(4)用VHDL完成的一个确定的设计,可以利用EDA工具进行逻辑综合和优化,并自动的把VHDL描述设计转变成门级网表(根据不同的实现芯片)。

(5)VHDL对设计的描述具有相对独立性。

设计者可以不懂硬件的结构,也不必管理最终设计实现的目标器件是什么,而进行独立的设计。

正因为VHDL的硬件描述与具体的工艺技术和硬件结构无关,所以VHDL设计程序的硬件实现目标器件有广阔的悬着范围。

(6)VHDL具有类属描述语句和子程序调用等程序,对于完成的设计,在不改变源程序的条件下,只需要改变类属参数量或者函数,就能轻易地改变设计的规模和结构。

2.2.3 VHDL的设计流程用VHDL语言设计电路的流程:在用VHDL语言来设计电路时,主要的过程是这样的:(1)创建VHDL设计工程及使用文本编辑器输入设计源文件。

(2)使用编译工具编译源文件。

VHDL的编译器有很多,ACTIVE公司,MODELSIM 公司,SYNPLICITY公司,SYNOPSYS公司,VERIBEST公司等都有自己的编译器。

(3)目标器件的选择和源程序的编译及综合。

(4)编辑测试文件及器件引脚的锁定和适配。

(5)系统的功能仿真。

对进入功能仿真,给测试向量赋值,再设置波形的观察格式。

作为一个独立的设计项目而言,仿真文件的提供足可以证明你设计的完整性。

(6)连接硬件测试系统,进行下载操作,再通过硬件系统进行测试。

(7)综合。

综合的目的是在于将设计的源文件由语言转换为实际的电路。

这一部分的最终目的是生成门电路级的网表(Netlist)。

(8)布局、布线。

这一步的目的是生成用于烧写的编程文件。

在这一步,将用到第(7)步生成的网表并根据CPLD/FPG厂商的器件容量,结构等进行布局、布线。

这就好像在设计PCB时的布局布线一样。

先将各个设计中的门根据网表的内容和器件的结构放在器件的特定部位。

然后,在根据网表中提供的各门的连接,把各个门的输入输出连接起来。

(9)后仿真。

这一步主要是为了确定你的设计在经过布局布线之后,是不是还满足你的设计要求。

3 简易电子琴设计过程3.1简易电子琴的工作原理音乐产生原理及硬件设计由于一首音乐是许多不同的音阶组成的,而每个音阶对应着不同的频率,这样我们就可以利用不同的频率的组合,即可构成我们所想要的音乐了,3.2简易电子琴的工作流程图开始TO初始化并开中断允放TO中断按键按下是否成功识别按键功能根据按键功能,装入音符T到TO中启动TO工作按键释放是否成功?停止TO工作TO中断入重装THO,TLO初值P1.0取反中断返回图3.2 简易电子琴的工作流程图3.3简易电子琴中各模块的设计为了更清楚的了解电子琴的工作过程,我们利用EDA工具(本课程设计Max+plus)对各个模块实施时序仿真(Timing Simulation),由自顶向下的设计方式,最后将三个模块进行整合,做出简易电子琴整个系统的时序仿真图。

3.3.1 乐曲自动演奏模块乐曲自动演奏模块的作用是产生8位发声控制输入信号。

当进行自动演奏时,由存储在此模块中的8位二进制作为发声控制输入,从而自动演奏乐曲。

这段模块的原理图如图3.3所示:CLKAUTO INDEX0[7.0]INDEX2[7.0]3.3 乐曲自动演奏模块原理图乐曲自动演奏模块可以由VHDL语言来实现,下面是一段主要代码:BEGINIF AUTO='0'THENCASE COUNT ISWHEN 0=>INDEX0<="00000100"; --3WHEN 1=>INDEX0<="00000100"; --3WHEN 2=>INDEX0<="00000100"; --3WHEN 3=>INDEX0<="00000100"; --3WHEN 29=>INDEX0<="00000100"; --3WHEN 30=>INDEX0<="00000010"; --2WHEN 31=>INDEX0<="00000010"; --2END CASE;ELSE INDEX0<=INDEX2;END IF;END PROCESS;3.3.2 音调发生模块音调发生模块的作用是产生音阶的分频预置值。