数字电路与逻辑设计试题及答案2套

1.三极管有NPN和PNP两种类型,当它工作在放大状态时,发射结____,集

电结______;NPN型三极管的基区是______型半导体,集电区和发射区是______型半导体。

2.把高电压作为逻辑1,低电平作为逻辑0的赋值方法称作_______逻辑赋

值。一种电路若在正逻辑赋值时为与非门,则在负逻辑赋值时为________。

3.四位二进制编码器有____个输入端;____个输出端。

4.将十进制数287转换成二进制数是________;十六进制数是_____

__。

5.根据触发器功能的不同,可将触发器分成四种,分别是____触发器、___

_触发器、____触发器和____触发器。

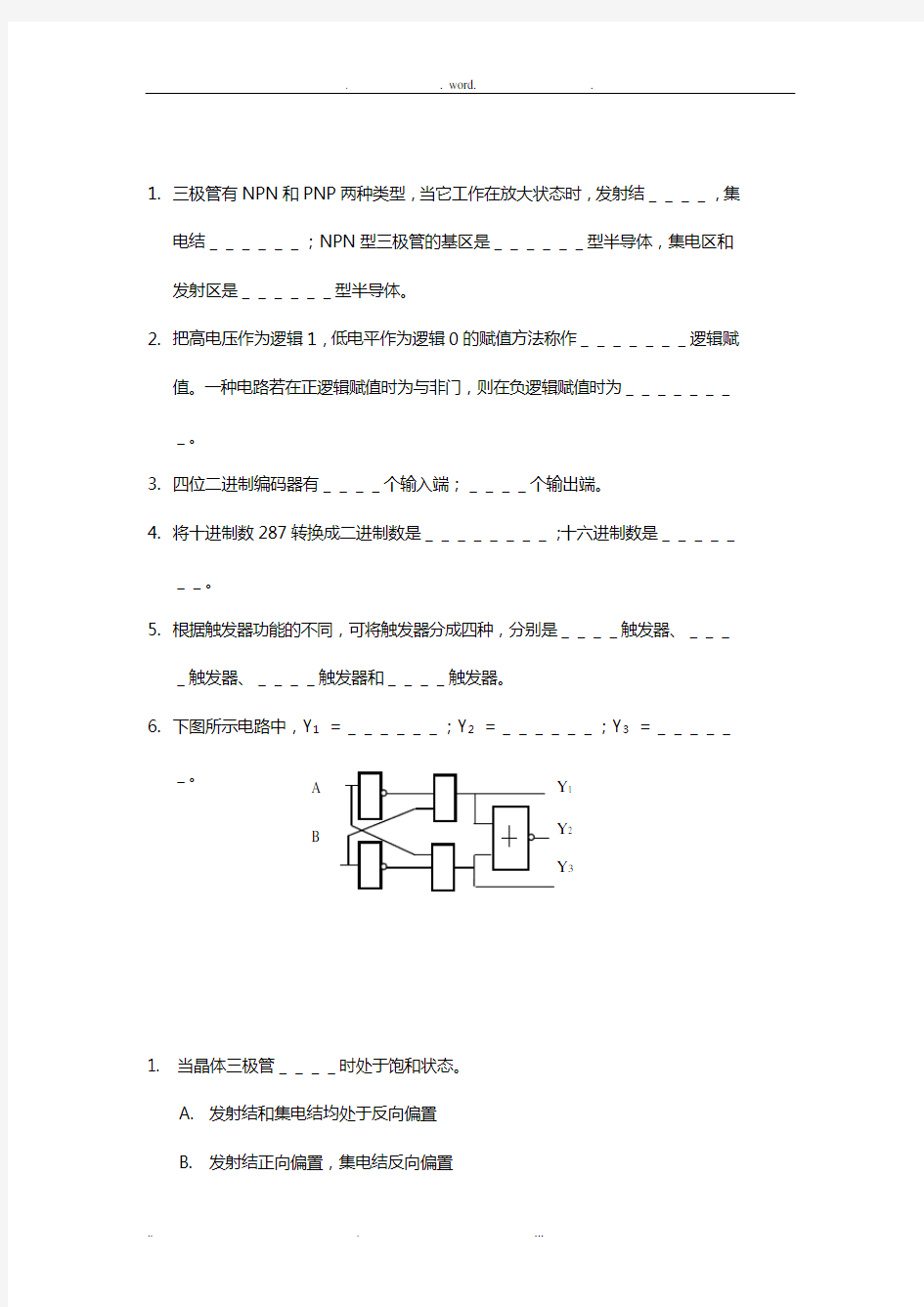

6.下图所示电路中,Y1=______;Y2=______;Y3=_____

1. 当晶体三极管____时处于饱和状态。

A.发射结和集电结均处于反向偏置

B.发射结正向偏置,集电结反向偏置

C. 发射结和集电结均处于正向偏置

2. 在下列三个逻辑函数表达式中,____是最小项表达式。

A .

B A B A )B ,A (Y += B.

C B C B A BC A )C ,B ,A (Y ++= C. C AB ABC B C A C B A )

D ,C ,B ,A (Y +++??=

3.用8421码表示的十进制数45,可以写成__________

A .45 B. [101101]BCD C. [01000101]BCD D. [101101]2 4.采用OC 门主要解决了_____

A .TTL 与非门不能相与的问题 B. TTL 与非门不能线与的问题 C. TTL 与非门不能相或的问题

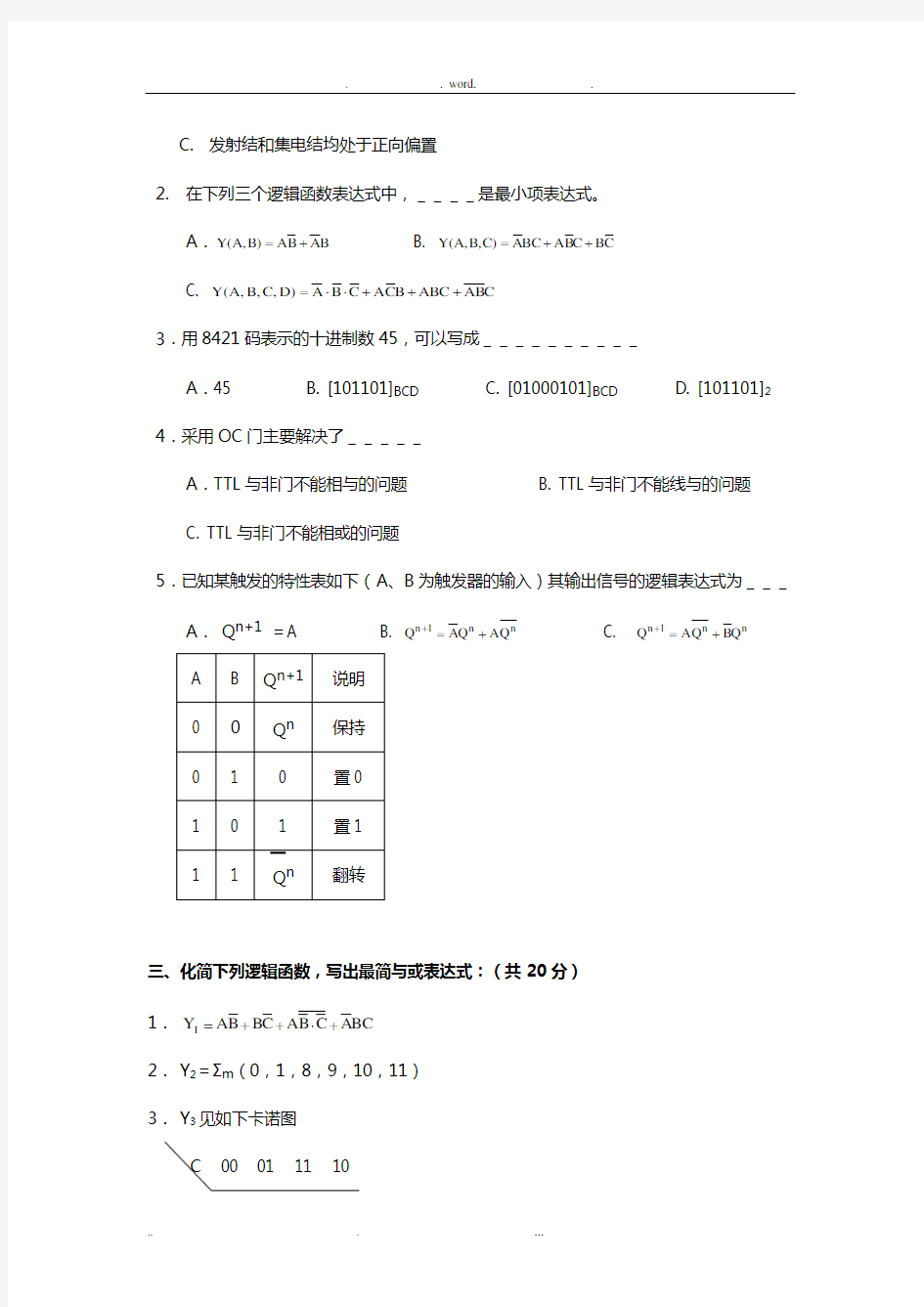

5.已知某触发的特性表如下(A 、B 为触发器的输入)其输出信号的逻辑表达式为___

A . Q n+1 =A B. n n 1n Q A Q A Q +=+ C. n n 1n Q

B Q A Q +=+

三、化简下列逻辑函数,写出最简与或表达式:(共20分) 1. BC A C B A C B B A Y 1+?++= 2. Y 2=Σm (0,1,8,9,10,11) 3. Y 3见如下卡诺图

四、分析设计题 (共 30分)

1.四选一数据选择器的功能见下表,要实现Y (A ,B ,C )=Σm (1,4,6,7)功能,芯片应如何连接,画出电路连接图(需写出必要的解题步骤)(20分)

2.触发器电路如下图所示,试根据CP 及输入波形画出输出端Q 1 、Q 2 的波形。设各触”(10分)。

《数字集成电路基础》试题二评分标准

一、填空题(共30分。每空2分,第5小题每空1分)

1.正偏;反偏;P;N。

2.正逻辑;负或非门。

3.16;4。

4.(100011111)2 ;(11F)16 。

5.RS;JK;D;T。

6.Y1=A B;Y2=A B+A B ;Y3=AB

二、选择题(共20分。每题4分)

(1)C (2) A (3) C (4) B (5) C

三、化简下列逻辑函数,写出最简与或表达式(共20分。第1题6分;第2、3题,每题7分)

(1) Y 1=A+B

(2) C B B A Y 2?+= 或 C B B A ??

(3) D C D C B A Y 3++=

四、分析设计题 (共 30分。第1题20分;第2题10分) 1、 ABC C AB C B A C B A )C ,B ,A (Y ++?+?= ……………2分

化简得:

Y (A,B,C )=A B C +A C +A B= A B C +A B C +A B C +A B =A B C +A B C +A B ……………4分

而由功能表可得

Y =A B D 0+A B D 1+A B D 2+A B D 3 …………4分

所以 D 0=C

D 1=0 D 2=C D 3=1

……………5分

图全对5分

2、

Q 1;Q 2的波形各5分。

一、

填空题(本题满分20分,共含10道小题,每小题2分)

1. 在权电阻网络D/A 转换器中,已知REF V =5V ,当输入数字量为01100123=d d d d 时输

出电压的大小为( )V 。 2.

168210)()()()43.465(===

3. TTL 与非门多余输入端的处理方法是( ),能实现总线连接方式的门电路有( )。

4. 逻辑函数中的( )和( )统称为无关项。

5. 10)459(转换为8421BCD 码为( ),转换为余三码为( )。

二、 逻辑函数式的化简(本题满分12分,共含2道小题,每小题6分)

1. 用卡诺图将逻辑函数Y 化为最简与或式:

∑∑+=)14,11,10,6,3,2()13,12,8,4,1(),,,(d m D C B A Y

2. 把下列逻辑函数式化简为最简与或式:

))((''+''=AC BD D C AB Y

三、

试用一片8选1数据选择器74HC151设计电路,实现如下功能:既可

以实现三人表决(遵循少数服从多数原则)功能,又可以实现判断三输入逻辑是否一致(如果一致输出结果为高电平)的功能:当控制信号M=0时,实现三人表决功能;当M=1时,实现判断三逻辑是否一致的功能。要求给出设计的全过程,并画出逻辑电路图。(16分)

四、如图所示的主从JK触发器电路中,CLK和A的电压波形如图所示,试

画出Q端对应的电压波形。设触发器的初始状态为Q=0。(14分)

A

CLK

0Q

CLK

五、试写出下图所示时序电路的驱动方程、状态方程和输出方程,画出电路

的状态转换表和状态转换图,分析电路的逻辑功能。(14分)

六、试用一片4位同步二进制计数器74LS161接成十一进制计数器(允许

附加必要的门电路,采用清零法),并作简要说明。74LS161的引脚图如下所示。(12分)